目前頻率合成器的研究雖然已經(jīng)非常成熟,但是在其實(shí)際應(yīng)用中經(jīng)常會(huì)出現(xiàn)難以解決的問(wèn)題。合成器設(shè)計(jì)者們主要關(guān)心的是相位噪聲。這在多普勒雷達(dá)、捷變頻雷達(dá)以及各種通信系統(tǒng)中極其重要。在這些應(yīng)用中,合成器相位噪聲可能會(huì)限制系統(tǒng)的動(dòng)態(tài)范圍和接收靈敏度。在機(jī)載合成器設(shè)計(jì)中關(guān)鍵的步驟包括:選擇最優(yōu)結(jié)構(gòu)使相位噪聲最小,抑制其它信號(hào)源帶來(lái)的雜散,以及提高效率,減小合成器體積。本文將介紹一種頻率合成器的設(shè)計(jì),其性能如下:

·頻率以20MHz為步進(jìn),從8.9 GHz變化到9.3GHz。

·100Hz頻偏處相位噪聲為-80dBc/Hz,10kH到600kHz頻偏相位噪聲為-97dBc/Hz。

·合成器必須采用100Hz處相位噪聲-115dBc/Hz的100MHz參考頻率。

·為了達(dá)到誤差小于1ppm的合成頻率,切換時(shí)間為20![]() 。

。

·在帶寬從10MHz到輸出信號(hào)二次諧波頻率范圍內(nèi)雜散幅度小于-64dBc。

·二次諧波幅度為-48dBc,三次諧波幅度為-55dBc。

·供電電壓12V時(shí),輸出功率+13dBm,消耗功率2.3W。

·合成器體積250![]() ,重量為470克。

,重量為470克。

壓控振蕩器(VCO)相位噪聲分析:VCO頻段選取

合成器包括壓控振蕩器(VCO)、鎖相環(huán)(PLL)電路和參考信號(hào)源。鎖相環(huán)IC頻帶的上限低于所需輸出頻帶,僅僅達(dá)到其一半。設(shè)計(jì)合成器有兩種不同方法——用頻率為輸出頻率一半的VCO產(chǎn)生PLL輸入信號(hào),然后對(duì)其進(jìn)行倍頻得到輸出;或用工作于輸出頻率的VCO產(chǎn)生信號(hào)然后分頻得到PLL輸入信號(hào)。VCO的相位噪聲性能是選擇最佳方法的主要準(zhǔn)則。用Leeson等式描述VCO相位噪聲為:

其中:

![]() =頻率偏移(Hz)

=頻率偏移(Hz)

![]() =振蕩頻率(Hz)

=振蕩頻率(Hz)

![]() =等效噪聲阻抗為R的共振電路負(fù)載Q值

=等效噪聲阻抗為R的共振電路負(fù)載Q值

![]() =作為放大器元件的有源設(shè)備閃爍轉(zhuǎn)角頻率(Hz)

=作為放大器元件的有源設(shè)備閃爍轉(zhuǎn)角頻率(Hz)

F = 有源設(shè)備的噪聲指數(shù)

k=玻爾茨曼常數(shù),![]() (J/K)

(J/K)

T=溫度(開(kāi)氏溫標(biāo))

![]() =有源設(shè)備輸入端信號(hào)的平均功率

=有源設(shè)備輸入端信號(hào)的平均功率

![]() =振蕩電壓調(diào)諧增益(Hz/V)

=振蕩電壓調(diào)諧增益(Hz/V)

![]() 這一項(xiàng)表示阻抗R的噪聲。通常遠(yuǎn)小于其它噪聲而可能被忽略。

這一項(xiàng)表示阻抗R的噪聲。通常遠(yuǎn)小于其它噪聲而可能被忽略。

于是有:

其中噪聲電平數(shù)NF表示每一邊帶的寬帶熱噪聲,Pout為dBm形式的振蕩器輸出功率,G為dB形式的有源設(shè)備增益,![]() 為振蕩器-3dBm半頻帶寬度。

為振蕩器-3dBm半頻帶寬度。

可以對(duì)已公布的4.3GHzVCO計(jì)算其L(![]() )典型值。該VCO擁有4%的調(diào)諧帶寬,這一帶寬很接近合成器的需求。包含一個(gè)串聯(lián)諧振電路和一個(gè)正反饋共射放大器,其中使用了Agilent公司的硅雙極性晶體管AT-42086。此晶體管噪聲系數(shù)F=8.5dB。因?yàn)檩斎攵诉h(yuǎn)遠(yuǎn)沒(méi)有達(dá)到使噪聲最小的最佳值,因此噪聲系數(shù)顯著惡化。該VCO的輸出功率為10.5dBm,晶體管增益為8dB。因此NF=-167.8dBc/Hz。

)典型值。該VCO擁有4%的調(diào)諧帶寬,這一帶寬很接近合成器的需求。包含一個(gè)串聯(lián)諧振電路和一個(gè)正反饋共射放大器,其中使用了Agilent公司的硅雙極性晶體管AT-42086。此晶體管噪聲系數(shù)F=8.5dB。因?yàn)檩斎攵诉h(yuǎn)遠(yuǎn)沒(méi)有達(dá)到使噪聲最小的最佳值,因此噪聲系數(shù)顯著惡化。該VCO的輸出功率為10.5dBm,晶體管增益為8dB。因此NF=-167.8dBc/Hz。

串聯(lián)諧振電路的整體有源阻抗為12.8![]() ,容抗為206

,容抗為206![]() ,負(fù)載Q值為16.1,因此

,負(fù)載Q值為16.1,因此![]() 。硅雙極性晶體管的閃爍轉(zhuǎn)角頻率確定為經(jīng)驗(yàn)數(shù)值4kHz。那么對(duì)于

。硅雙極性晶體管的閃爍轉(zhuǎn)角頻率確定為經(jīng)驗(yàn)數(shù)值4kHz。那么對(duì)于![]() =100kHz,計(jì)算得到VCO相位噪聲為-105.5dBc/Hz,而測(cè)量出的相位噪聲為-104.4dBc/Hz。

=100kHz,計(jì)算得到VCO相位噪聲為-105.5dBc/Hz,而測(cè)量出的相位噪聲為-104.4dBc/Hz。

9.1GHzVCO的L(![]() )典型值可以根據(jù)Leeson等式預(yù)測(cè)出并與4.55GHzVCO(輸出頻率的一半)的L(

)典型值可以根據(jù)Leeson等式預(yù)測(cè)出并與4.55GHzVCO(輸出頻率的一半)的L(![]() )值進(jìn)行對(duì)比,這兩種VCO具有相同的調(diào)諧帶寬即合成器所要求帶寬的4.4%。這里假定兩個(gè)VCO均采用雙極性晶體管,因?yàn)樗葓?chǎng)效應(yīng)晶體管的相位噪聲低10-15dB。

)值進(jìn)行對(duì)比,這兩種VCO具有相同的調(diào)諧帶寬即合成器所要求帶寬的4.4%。這里假定兩個(gè)VCO均采用雙極性晶體管,因?yàn)樗葓?chǎng)效應(yīng)晶體管的相位噪聲低10-15dB。

造成9.1GHzVCO性能惡化的第一個(gè)因素是輸出頻率增加。如果Leeson等式中![]() 乘以2,那么在

乘以2,那么在![]() 區(qū)域內(nèi)L(

區(qū)域內(nèi)L(![]() )增加6dB。當(dāng)然,這種惡化在通過(guò)倍頻4.55GHzVCO后生成合成器輸出頻率時(shí)能夠被抵消。

)增加6dB。當(dāng)然,這種惡化在通過(guò)倍頻4.55GHzVCO后生成合成器輸出頻率時(shí)能夠被抵消。

第二個(gè)惡化因素是晶體管![]() 在面積較小的設(shè)備中較高,相反地,更大面積的設(shè)備能夠在更低頻率上得到更大的輸出功率。因此,一般來(lái)說(shuō)9.1GHzVCOLeeson等式中的

在面積較小的設(shè)備中較高,相反地,更大面積的設(shè)備能夠在更低頻率上得到更大的輸出功率。因此,一般來(lái)說(shuō)9.1GHzVCOLeeson等式中的![]() 值比4.55GHzVCO低3到6dB。如果兩個(gè)VCO的晶體管噪聲系數(shù)為常數(shù),則9.1GHzVCO的噪聲水平通常要高出3到6dB。

值比4.55GHzVCO低3到6dB。如果兩個(gè)VCO的晶體管噪聲系數(shù)為常數(shù),則9.1GHzVCO的噪聲水平通常要高出3到6dB。

第三個(gè)惡化因素是![]() 值下降,這是由于頻率翻倍時(shí)諧振器容抗變成原來(lái)的一半。當(dāng)然,設(shè)計(jì)者可以用一個(gè)較小容值的變?nèi)荻O管來(lái)保持恒定容抗,但他也可以在更低頻率的VCO中使用這個(gè)變?nèi)荻O管。

值下降,這是由于頻率翻倍時(shí)諧振器容抗變成原來(lái)的一半。當(dāng)然,設(shè)計(jì)者可以用一個(gè)較小容值的變?nèi)荻O管來(lái)保持恒定容抗,但他也可以在更低頻率的VCO中使用這個(gè)變?nèi)荻O管。

比如,Microsemi公司的高Q值微波突變變?nèi)荻O管GC1300有C(0V)=1.2pF,C(4V)=0.8pF。該變?nèi)荻O管串聯(lián)一個(gè)0.27pF電容后,就能夠覆蓋合成器帶寬的4.4%。諧振器容抗在4.55GHz時(shí)為170![]() ,而在9.1GHz時(shí)為85

,而在9.1GHz時(shí)為85![]() 。如果對(duì)于這兩種VCO,其串聯(lián)諧振電路的總的有源阻抗均保持恒定,那么9.1GHz VCO的負(fù)載Q值為4.55GHzVCO的一半,并且其相位噪聲比4.55GHz VCO高6dB。由于9.1GHzVCO的相位噪聲比4.55GHz VCO加上倍頻器的還高9到12dB,因此合成器中采用了4.55GHz VCO。

。如果對(duì)于這兩種VCO,其串聯(lián)諧振電路的總的有源阻抗均保持恒定,那么9.1GHz VCO的負(fù)載Q值為4.55GHzVCO的一半,并且其相位噪聲比4.55GHz VCO高6dB。由于9.1GHzVCO的相位噪聲比4.55GHz VCO加上倍頻器的還高9到12dB,因此合成器中采用了4.55GHz VCO。

把VCO或集成振蕩器子模塊作為體組件并向?qū)iT(mén)廠商購(gòu)買將會(huì)更加實(shí)際。對(duì)于4.55GHzVCO,Hittite Microwave公司的HMC429LP4集成VCO是最好的選擇,因?yàn)樗哂?/span>100kHz頻偏、單邊帶相位噪聲-105dBc/Hz以及4.4到4.7GHz的調(diào)諧頻段。

鎖相環(huán)(PLL)相位噪聲分析:最優(yōu)PLL結(jié)構(gòu)的選擇

選擇最佳PLL結(jié)構(gòu)的主要標(biāo)準(zhǔn)是其相位噪聲性能。圖1給出PLL噪聲模型。這

圖1 PLL噪聲模型

個(gè)模型中,![]() 表示參考相位,

表示參考相位,![]() 表示參考相位的噪聲。

表示參考相位的噪聲。![]() 和

和![]() 表示PLL輸入、輸出相位。1/M和1/N分別為分頻器參考和主要系數(shù)。

表示PLL輸入、輸出相位。1/M和1/N分別為分頻器參考和主要系數(shù)。![]() 和

和![]() 為相位檢測(cè)器、低通濾波器和VCO的傳輸函數(shù)。

為相位檢測(cè)器、低通濾波器和VCO的傳輸函數(shù)。![]() 表示PLL芯片噪聲,其中包括分頻器噪聲和相位檢測(cè)器噪聲。另外一項(xiàng)

表示PLL芯片噪聲,其中包括分頻器噪聲和相位檢測(cè)器噪聲。另外一項(xiàng)![]() 表示濾波器(Ufn)的均方根(RMS)噪聲電壓。

表示濾波器(Ufn)的均方根(RMS)噪聲電壓。![]() 表示VCO噪聲。開(kāi)環(huán)增益表示如下:

表示VCO噪聲。開(kāi)環(huán)增益表示如下:

噪聲輸入至PLL輸出端的傳輸函數(shù)定義如下:

生產(chǎn)廠商通常給出VCO、參考源和PLL芯片的相位噪聲數(shù)據(jù),如單邊帶相位噪聲![]() 和

和![]() 。PLL輸出端相位噪聲為:

。PLL輸出端相位噪聲為:

其中:

僅為VCO的輸出相位噪聲,

僅為VCO的輸出相位噪聲,

僅為參考源的輸出相位噪聲,

僅為參考源的輸出相位噪聲,

僅為PLL芯片的輸出相位噪聲,

僅為PLL芯片的輸出相位噪聲,

僅為濾波器的相位噪聲。

僅為濾波器的相位噪聲。

整數(shù)N鎖相環(huán)

最簡(jiǎn)單的PLL結(jié)構(gòu)為整數(shù)N鎖相環(huán)。在這種結(jié)構(gòu)下輸出頻率為:

![]()

其中![]() =10MHz為相位檢測(cè)器頻率(輸出頻率的一半),N=445…465為主分頻系數(shù)。介于Analog Devices公司的ADF4107PLL芯片有很寬的輸入頻帶(高達(dá)7GHz)、高相位檢測(cè)器頻率(高達(dá)104MHz),以及低除法器、相位檢測(cè)器相位噪聲(

=10MHz為相位檢測(cè)器頻率(輸出頻率的一半),N=445…465為主分頻系數(shù)。介于Analog Devices公司的ADF4107PLL芯片有很寬的輸入頻帶(高達(dá)7GHz)、高相位檢測(cè)器頻率(高達(dá)104MHz),以及低除法器、相位檢測(cè)器相位噪聲(![]() =10MHz時(shí)

=10MHz時(shí)![]() =-149dBc/Hz),這里使用該芯片作為PLL。PLL參考源采用Morion公司的MV87-1-100MHz恒溫控制晶體振蕩器(OCXO),理由是其相位噪聲很低,100Hz頻偏時(shí)其相位噪聲為-115dBc/Hz。PLL采用了二階無(wú)源充電泵濾波器。該濾波器的傳輸函數(shù)即為其阻抗。G(s)相位拐點(diǎn)處的頻率

=-149dBc/Hz),這里使用該芯片作為PLL。PLL參考源采用Morion公司的MV87-1-100MHz恒溫控制晶體振蕩器(OCXO),理由是其相位噪聲很低,100Hz頻偏時(shí)其相位噪聲為-115dBc/Hz。PLL采用了二階無(wú)源充電泵濾波器。該濾波器的傳輸函數(shù)即為其阻抗。G(s)相位拐點(diǎn)處的頻率![]() 與PLL帶寬相同。G(s)的相位項(xiàng)在

與PLL帶寬相同。G(s)的相位項(xiàng)在![]() 處取得最大值

處取得最大值![]() 。一般的經(jīng)驗(yàn)法則是從

。一般的經(jīng)驗(yàn)法則是從![]() 開(kāi)始對(duì)PLL進(jìn)行設(shè)計(jì)。但是,這里推薦把

開(kāi)始對(duì)PLL進(jìn)行設(shè)計(jì)。但是,這里推薦把![]() 緩緩提升至

緩緩提升至![]() ,式5-8傳輸函數(shù)中

,式5-8傳輸函數(shù)中![]() 處只有1dB的過(guò)沖。

處只有1dB的過(guò)沖。

為了使PLL在所有頻偏處均能獲得最小相位噪聲,帶寬![]() 必須靠近某點(diǎn),使自由運(yùn)行VCO相位噪聲與來(lái)自其它噪聲源的所有PLL相位噪聲相等。如果

必須靠近某點(diǎn),使自由運(yùn)行VCO相位噪聲與來(lái)自其它噪聲源的所有PLL相位噪聲相等。如果![]() 較小,PLL無(wú)法在頻偏比較高時(shí)改進(jìn)VCO相位噪聲。

較小,PLL無(wú)法在頻偏比較高時(shí)改進(jìn)VCO相位噪聲。![]() 較大時(shí),當(dāng)頻偏超過(guò)

較大時(shí),當(dāng)頻偏超過(guò)![]() 時(shí)PLL會(huì)使VCO相位噪聲惡化。由式11、12,有

時(shí)PLL會(huì)使VCO相位噪聲惡化。由式11、12,有![]() ,N=455,M=10,Nref=-125.8dBc/Hz以及

,N=455,M=10,Nref=-125.8dBc/Hz以及![]() =-94.8dBc/Hz。

=-94.8dBc/Hz。

假定![]() ,環(huán)路濾波器噪聲比

,環(huán)路濾波器噪聲比![]() 低很多,那么

低很多,那么![]() 成為最主要噪聲源。從VCO相位噪聲圖來(lái)看,

成為最主要噪聲源。從VCO相位噪聲圖來(lái)看,![]() =75kHz此時(shí)

=75kHz此時(shí)![]() 為-101dBc/Hz。當(dāng)

為-101dBc/Hz。當(dāng)![]() =

=![]() 75kHz由式9算出

75kHz由式9算出![]() =-93.7dBc/Hz。如果定義了

=-93.7dBc/Hz。如果定義了![]() 和

和![]() ,則濾波器元件參數(shù)可知:

,則濾波器元件參數(shù)可知:![]() 。為了獲得濾波器輸出端的均方根噪聲電壓,實(shí)際應(yīng)用中的電阻

。為了獲得濾波器輸出端的均方根噪聲電壓,實(shí)際應(yīng)用中的電阻![]() 可以用一個(gè)理想電阻和一個(gè)串聯(lián)等價(jià)噪聲源代替,噪聲源的均方根電壓為:

可以用一個(gè)理想電阻和一個(gè)串聯(lián)等價(jià)噪聲源代替,噪聲源的均方根電壓為:

濾波器產(chǎn)生的輸出相位噪聲僅可由式12-14得到:

![]() =75kHz時(shí)算得Nfn = -112dBc/Hz。為了確定這種設(shè)想,利用Analog Devices公司的ADI SimPLL軟件按照之前定義的那些參數(shù)對(duì)PLL性能進(jìn)行仿真。由式4計(jì)算出的開(kāi)環(huán)增益和相位如圖2所示。僅由參考源

=75kHz時(shí)算得Nfn = -112dBc/Hz。為了確定這種設(shè)想,利用Analog Devices公司的ADI SimPLL軟件按照之前定義的那些參數(shù)對(duì)PLL性能進(jìn)行仿真。由式4計(jì)算出的開(kāi)環(huán)增益和相位如圖2所示。僅由參考源![]() 和僅由PLL芯片

和僅由PLL芯片![]() 產(chǎn)生的輸出相位噪聲根據(jù)廠商給出的數(shù)據(jù)和式11、12計(jì)算出來(lái),結(jié)果如圖3所示。僅由VCO

產(chǎn)生的輸出相位噪聲根據(jù)廠商給出的數(shù)據(jù)和式11、12計(jì)算出來(lái),結(jié)果如圖3所示。僅由VCO![]() 和僅由環(huán)路濾波器

和僅由環(huán)路濾波器![]() 產(chǎn)生的輸出相位噪聲,根據(jù)廠商提供數(shù)據(jù)和式10、15算出結(jié)果見(jiàn)圖4。由式9可算出PLL總輸出相位噪聲,如圖5所示。

產(chǎn)生的輸出相位噪聲,根據(jù)廠商提供數(shù)據(jù)和式10、15算出結(jié)果見(jiàn)圖4。由式9可算出PLL總輸出相位噪聲,如圖5所示。

圖2 開(kāi)環(huán)增益(藍(lán))和相位(紅)

圖3 僅由參考源(藍(lán))和僅由PLL芯片(紅)得到輸出相位噪聲

圖4 僅由VCO(藍(lán))和僅由環(huán)路濾波器(紅)得到的輸出相位噪聲

圖5 PLL總輸出相位噪聲

在PLL帶寬中有兩個(gè)區(qū)域。在第一個(gè)區(qū)域(![]() 500Hz)內(nèi),參考源輸出相位噪聲是所有噪聲源中最大的。在第一個(gè)區(qū)域內(nèi)

500Hz)內(nèi),參考源輸出相位噪聲是所有噪聲源中最大的。在第一個(gè)區(qū)域內(nèi)![]() 處合成器輸出相位噪聲(SPN)由下式給出:

處合成器輸出相位噪聲(SPN)由下式給出:

第二個(gè)區(qū)域(1kHz![]() 50kHz)內(nèi),芯片輸出相位噪聲在所有噪聲源中最大。其大小依鑒相器頻率而定,關(guān)系如下:

50kHz)內(nèi),芯片輸出相位噪聲在所有噪聲源中最大。其大小依鑒相器頻率而定,關(guān)系如下:

其中當(dāng)![]() 時(shí)

時(shí)![]() =-219dBc/Hz為鑒相器ADF4107的相位噪聲水平。因此,在第二個(gè)區(qū)域內(nèi),合成器輸出相位噪聲由下式給出

=-219dBc/Hz為鑒相器ADF4107的相位噪聲水平。因此,在第二個(gè)區(qū)域內(nèi),合成器輸出相位噪聲由下式給出

分?jǐn)?shù)N鎖相環(huán)

由式16、18可看出要減小![]() 和

和![]() ,必須增大

,必須增大![]() 、減小N。然而這樣就會(huì)使N變?yōu)樾?shù)。為了工作在小數(shù)N模式下,必須用到小數(shù)N鎖相環(huán)芯片。這里采用Analog Devices公司的ADF4193芯片和Z-Communications公司的V630ME09 VCO來(lái)仿真小數(shù)N鎖相環(huán)的性能。因?yàn)檫@種PLL芯片的最大輸入頻率只有3.5GHz,所以采用了一個(gè)4倍頻器產(chǎn)生合成器輸出信號(hào)。這樣輸出頻率就為:

、減小N。然而這樣就會(huì)使N變?yōu)樾?shù)。為了工作在小數(shù)N模式下,必須用到小數(shù)N鎖相環(huán)芯片。這里采用Analog Devices公司的ADF4193芯片和Z-Communications公司的V630ME09 VCO來(lái)仿真小數(shù)N鎖相環(huán)的性能。因?yàn)檫@種PLL芯片的最大輸入頻率只有3.5GHz,所以采用了一個(gè)4倍頻器產(chǎn)生合成器輸出信號(hào)。這樣輸出頻率就為:

其中INT為N的整數(shù)部分,FRAC/MOD則為N的小數(shù)部分。因?yàn)?/span>ADF4193最大鑒相器頻率為26MHz,所以把![]() 設(shè)為25MHz(M=4),MOD=25。這樣就可得到INT=89…92,FRAC=0…24和頻率間隔為4

設(shè)為25MHz(M=4),MOD=25。這樣就可得到INT=89…92,FRAC=0…24和頻率間隔為4![]() =4MHz的一組輸出頻率。這里只需利用其中的每間隔四個(gè)頻點(diǎn)的頻率。PLL相位噪聲-頻偏曲線如圖6所示。

=4MHz的一組輸出頻率。這里只需利用其中的每間隔四個(gè)頻點(diǎn)的頻率。PLL相位噪聲-頻偏曲線如圖6所示。

圖6 小數(shù)N PLL的相位噪聲仿真

在第一個(gè)區(qū)域內(nèi)![]() 處合成器輸出相位噪聲為:

處合成器輸出相位噪聲為:

它與整數(shù)N PLL在頻偏100Hz時(shí)的![]() 相同,這是因?yàn)檫@兩個(gè)合成器參考頻率的總倍頻系數(shù)相同。在第二個(gè)區(qū)域內(nèi)合成器的輸出相位噪聲由下式給出

相同,這是因?yàn)檫@兩個(gè)合成器參考頻率的總倍頻系數(shù)相同。在第二個(gè)區(qū)域內(nèi)合成器的輸出相位噪聲由下式給出

與整數(shù)N PLL相比有4dB的性能提升,這是因?yàn)樵谛?shù)N PLL中的![]() 也比整數(shù)N PLL中大4dB。

也比整數(shù)N PLL中大4dB。

混合型合成器

另一個(gè)使合成器工作在分?jǐn)?shù)N模式下的方法是采用能夠進(jìn)行頻率轉(zhuǎn)移的混合合成器結(jié)構(gòu),如圖7所示。這種結(jié)構(gòu)包含第一種擁有最大允許值![]() 的固定整

的固定整

圖7 帶頻率轉(zhuǎn)移的混合合成器結(jié)構(gòu)

數(shù)N PLL和第二種可調(diào)整的整數(shù)N PLL。這些信號(hào)源的信號(hào)通過(guò)混頻器、濾波器和倍頻器混合。最終輸出頻率為:

其中![]() 、

、![]() 分別為第一和第二種PLL的頻率。固定PLL

分別為第一和第二種PLL的頻率。固定PLL![]() 的鑒相頻率為100MHz,達(dá)到了

的鑒相頻率為100MHz,達(dá)到了![]() 的最大允許值。可調(diào)PLL

的最大允許值。可調(diào)PLL![]() 的鑒相頻率為輸出頻率的一半或10MHz。

的鑒相頻率為輸出頻率的一半或10MHz。

式22表示FPD=100MHz時(shí)“真”小數(shù)N PLL。式22中的系數(shù)為:

其中int(x)為變量x的取整運(yùn)算。

由于第一、第二PLL芯片相互獨(dú)立,其輸出的相位噪聲相互獨(dú)立。因此,如果兩個(gè)噪聲相同,他們合并將得到最小值為:

兩個(gè)PLL均采用ADF4107,因?yàn)樗季哂凶钚〉?/span>PN基。因此有

![]() ,那么有

,那么有![]() 。

。

為了產(chǎn)生![]() 并且保持ADF4107的最小輸入頻率(1.0GHz),可以得到

并且保持ADF4107的最小輸入頻率(1.0GHz),可以得到![]() ,

,![]() =105…125。于是由式24、25有INT=34+10…12=44…46,FRAC=0…9

=105…125。于是由式24、25有INT=34+10…12=44…46,FRAC=0…9

因此PLL頻率值為![]() =3400MHz,

=3400MHz,![]() =1050…1250MHz。

=1050…1250MHz。

固定PLL的性能仿真采用Hittite Microwave公司的HMC389LP4。第一和第二個(gè)PLL的相位噪聲與頻偏之間的關(guān)系如圖8、9所示。

圖8 固定PLL的相位噪聲仿真

圖9 可調(diào)PLL輸出相位噪聲仿真

芯片相位噪聲約等于-107dBc/Hz。兩個(gè)芯片的輸出相位噪聲相互獨(dú)立,在4.45-4.65GHz內(nèi)合并后比之前大3dB,為-104dBc/Hz。![]() 等于-104+6=-98dBc/Hz。這比整數(shù)N PLL的性能提升8dB,這是因?yàn)榛旌虾铣善髦?/span>FPD比整數(shù)N PLL大10dB,而合并后性能損失只有3dB。在頻偏100Hz處,兩個(gè)PLL和合并以后的相位噪聲可以由以下式子獲得:

等于-104+6=-98dBc/Hz。這比整數(shù)N PLL的性能提升8dB,這是因?yàn)榛旌虾铣善髦?/span>FPD比整數(shù)N PLL大10dB,而合并后性能損失只有3dB。在頻偏100Hz處,兩個(gè)PLL和合并以后的相位噪聲可以由以下式子獲得:

![]() ,

,

![]() ,

,

![]()

![]() 等于-81.9+6=-75.9dBc/Hz。這與整數(shù)N PLL的

等于-81.9+6=-75.9dBc/Hz。這與整數(shù)N PLL的![]() 相同,這是因?yàn)閮蓚€(gè)合成器內(nèi)總的參考頻率倍頻系數(shù)相同。可以看到無(wú)論什么結(jié)構(gòu)都不能夠提升參考源相位噪聲,但混合合成器使PLL芯片輸出相位噪聲性能提升了8dB。

相同,這是因?yàn)閮蓚€(gè)合成器內(nèi)總的參考頻率倍頻系數(shù)相同。可以看到無(wú)論什么結(jié)構(gòu)都不能夠提升參考源相位噪聲,但混合合成器使PLL芯片輸出相位噪聲性能提升了8dB。

實(shí)際頻率轉(zhuǎn)移結(jié)構(gòu)

頻率轉(zhuǎn)移結(jié)構(gòu)存在兩個(gè)缺點(diǎn)——混頻器輸出電平低和混頻器雜散相對(duì)電平高。圖10給出了改良的實(shí)際結(jié)構(gòu)。HMC429LP4 VCO(1)產(chǎn)生一個(gè)4.45至4.65GHz的信號(hào)。擁有+14dBm功率的信號(hào)經(jīng)過(guò)隔離器(2)和場(chǎng)效應(yīng)管放大器(3)后,被功分器(4)分成2個(gè)部分。第一部分通過(guò)一個(gè)隔離器(5)進(jìn)入場(chǎng)效應(yīng)倍頻器(6)。第二部分通過(guò)隔離器(13)作為LO進(jìn)入Hittite Microwave公司的雙平衡混頻器HMC213MS8(14)。

圖10 實(shí)際頻率轉(zhuǎn)移結(jié)構(gòu)

固定3.4GHzPLL包含一個(gè)HMC389LP4 VCO(18)、隔離器(17)、功分器(16)、ADF4107PLL芯片(20)和無(wú)源三極環(huán)路濾波(21)。功分器(16)輸出的3.4GHz信號(hào)經(jīng)過(guò)諧波濾波器(15)進(jìn)入混頻器(14)RF輸入端,信號(hào)功率為-10dBm。混頻器(14)把4.45GHz到4.65GHzLO頻率轉(zhuǎn)換到1.05至1.25GHz IF頻率。然后功率為+2dBm的該IF信號(hào)經(jīng)過(guò)低通濾波器(19)和一個(gè)MMIC放大器(24)進(jìn)入ADF4107 PLL芯片。可調(diào)1.05至1.25GHz PLL包括一個(gè)芯片(25)、有源三極環(huán)路濾波器,成為“虛擬VCO”,它的靈敏度和相位噪聲與HMC429LP4 VCO相似。信號(hào)經(jīng)過(guò)倍頻器(6)以后,通過(guò)隔離器(7)輸入到帶通濾波器(BPF)(8)中。然后通過(guò)隔離器(9)進(jìn)入二級(jí)FET放大器(10)。信號(hào)經(jīng)過(guò)放大后功率為+16dBm,它再通過(guò)隔離器(11)和諧波濾波器(12)到達(dá)輸出端,此時(shí)功率為+13dBm。從外部100MHzOCXO輸入的參考源信號(hào)經(jīng)過(guò)放大器(22)放大后輸入PLL芯片(20,25)。頻率控制TTL信號(hào)輸入至Analog Devices公司的ADuC814 微轉(zhuǎn)換器(23)。然后把控制比特信息寫(xiě)入PLL芯片。

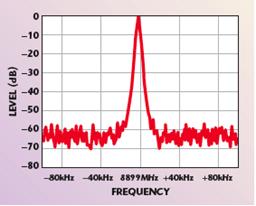

圖11 合成器輸出頻譜測(cè)量值

這種結(jié)構(gòu)與之前介紹的結(jié)構(gòu)有兩個(gè)不同點(diǎn)。首先,4.45至4.65GHz信號(hào)由更高功率的VCO產(chǎn)生,作為混頻器LO。其次,混頻器在這里的作用相當(dāng)于下變頻器,對(duì)于3.4和1.05-1.25GHz信號(hào),它均以更低功率運(yùn)行。其結(jié)果是使倍頻器器輸入端希望得到的信號(hào)功率更高無(wú)用信號(hào)的功率更低。這一結(jié)果非常重要,因?yàn)楸额l器會(huì)產(chǎn)生高階雜散,這些雜散在BPF(8)帶寬內(nèi)會(huì)增大。圖11給出HP8592頻譜分析儀測(cè)量出來(lái)的合成器輸出頻譜,該頻譜分析儀的帶寬解析度為3kHz。合成器輸出端連接一個(gè)6dB衰減器。在20-100kHz頻偏內(nèi)測(cè)量出來(lái)的平均噪聲大約等于-63dBc。因而以dBc/Hz為單位的平均噪聲給出如下:

![]()

這很符合理論結(jié)果-98dBc/Hz。

實(shí)際應(yīng)用結(jié)構(gòu)中的雜散抑制

在實(shí)際應(yīng)用結(jié)構(gòu)中存在三種雜散源—混頻器、倍頻器和PLL充電泵。混頻器(14)在LO輸入端有一個(gè)-33dBm、3.4GHz的RF泄露信號(hào)。隔離器(13)把該信號(hào)衰減至-50dBm。倍頻器產(chǎn)生一個(gè)具有很高帶寬的高次雜散,但在無(wú)用的3.4GHz頻率上該雜散的功率非常低。倍頻器輸出端所需信號(hào)為二次諧波,所有其它諧波都是無(wú)用的,必須通過(guò)BPF(8)進(jìn)行抑制。在4.5GHz頻率上合成器輸出雜散功率為-64dBc。BPF(8)對(duì)三次諧波的抑制大概為48dB,濾波器(12)提供一個(gè)20dB的額外抑制。PLL充電泵雜散是由充電泵不均衡以及輸出端DC電流引起。充電泵輸出端的總泄漏電流IL可假定為所有源的泄露總和。充電泵電流波形I(t)是幅度為![]() 、循環(huán)頻率為FPD的周期短時(shí)脈沖序列。對(duì)該信號(hào)進(jìn)行復(fù)立葉變換,并根據(jù)FM理論,可以得到一次雜散的相對(duì)值為:

、循環(huán)頻率為FPD的周期短時(shí)脈沖序列。對(duì)該信號(hào)進(jìn)行復(fù)立葉變換,并根據(jù)FM理論,可以得到一次雜散的相對(duì)值為:

其中![]() 為頻率

為頻率![]() 處的環(huán)路濾波器阻抗。

處的環(huán)路濾波器阻抗。

首先計(jì)算3.4GHz固定PLL的最大雜散值。該PLL參數(shù)為:![]() =100MHz,

=100MHz,

![]() =

=![]() ,

,![]() ,N=34,

,N=34,![]() ,

,![]() 。環(huán)路濾波器元件參數(shù)為:

。環(huán)路濾波器元件參數(shù)為:![]() =692pF,

=692pF,![]() =5.49nF,

=5.49nF,![]() =289

=289![]() 。環(huán)路濾波器阻抗值

。環(huán)路濾波器阻抗值![]() =2.3

=2.3![]() 。VCO(18)調(diào)諧端口的泄漏電流最大值為10

。VCO(18)調(diào)諧端口的泄漏電流最大值為10![]() 。式27給出了該雜散最大值:

。式27給出了該雜散最大值:![]() =-99dBc。這個(gè)值是可以接受的,但需要額外加一個(gè)截止頻率為3.0MHz的RC低通濾波器以抑制來(lái)自參考源的100MHz電磁干擾(EMI)。額外增加的RC電路組成一個(gè)三級(jí)無(wú)源環(huán)路濾波器,應(yīng)盡可能地靠近VCO(18)調(diào)諧管腳。它對(duì)參考源頻率產(chǎn)生額外的30dB衰減。合成器輸出一次雜散為-123dBc,在實(shí)際中不可測(cè)量。

=-99dBc。這個(gè)值是可以接受的,但需要額外加一個(gè)截止頻率為3.0MHz的RC低通濾波器以抑制來(lái)自參考源的100MHz電磁干擾(EMI)。額外增加的RC電路組成一個(gè)三級(jí)無(wú)源環(huán)路濾波器,應(yīng)盡可能地靠近VCO(18)調(diào)諧管腳。它對(duì)參考源頻率產(chǎn)生額外的30dB衰減。合成器輸出一次雜散為-123dBc,在實(shí)際中不可測(cè)量。

在1.05-1.25GHz可調(diào)PLL中,VCO(1)調(diào)諧端的泄漏電流也為10![]() ,但鑒相器頻率為10MHz。與濾波器(21)相同的環(huán)路濾波器僅能將雜散抑制到-51dBc(一次輸出雜散)。對(duì)充電泵采用最終頻率為3.2MHz的有源350kHz三次環(huán)路濾波器抑制其雜散。其原理圖如圖12。其中運(yùn)算放大器(op-amp)采用Analog Devices公司的低噪聲OP184FS。有源濾波器的主要優(yōu)點(diǎn)是把泄漏電流減小至0.6

,但鑒相器頻率為10MHz。與濾波器(21)相同的環(huán)路濾波器僅能將雜散抑制到-51dBc(一次輸出雜散)。對(duì)充電泵采用最終頻率為3.2MHz的有源350kHz三次環(huán)路濾波器抑制其雜散。其原理圖如圖12。其中運(yùn)算放大器(op-amp)采用Analog Devices公司的低噪聲OP184FS。有源濾波器的主要優(yōu)點(diǎn)是把泄漏電流減小至0.6![]() 。它將一次輸出雜散衰減至-72dBc。測(cè)量出的雜散為-70dBc。

。它將一次輸出雜散衰減至-72dBc。測(cè)量出的雜散為-70dBc。

圖12 有源350kHz三階環(huán)路濾波器原理圖

對(duì)來(lái)自供電單元的雜散抑制

獲得高功效對(duì)機(jī)載設(shè)備尤為重要。合成器所有組件所需電壓為+3.0或+5.0V,但電源電壓為+12V。DC-DC降壓器可以解決這個(gè)問(wèn)題,但其第四個(gè)雜散源和額外的相位噪聲,同時(shí)占用了通常為190![]() 的狹小空間的一部分。因此需要對(duì)DC-DC降壓器的電磁噪聲進(jìn)行高強(qiáng)度抑制4,5。噪聲有兩種傳播路徑—導(dǎo)線傳播和降壓器電感的磁場(chǎng)傳播。采用小空隙的自屏蔽電感磁芯可以對(duì)后一條傳播路徑進(jìn)行抑制。導(dǎo)線傳播有兩種模式—共模和差模。對(duì)共模傳播的噪聲,可以把PCB上的降壓器懸置(減小與地面間的寄生電容),并在它的輸入輸出端接共模扼流來(lái)進(jìn)行抑制。差模波紋和噪聲采用LC-LPF和Analog Devices公司的調(diào)壓器ADP3301抑制。在260kHz降壓器轉(zhuǎn)換頻率處PLL不工作,VCO(1)近似運(yùn)行在自激勵(lì)狀態(tài)下。有人發(fā)現(xiàn)了來(lái)自電源波紋的260kHz雜散。VCO輸出端的正弦調(diào)頻(FM)雜散功率由下式給出4,5:

的狹小空間的一部分。因此需要對(duì)DC-DC降壓器的電磁噪聲進(jìn)行高強(qiáng)度抑制4,5。噪聲有兩種傳播路徑—導(dǎo)線傳播和降壓器電感的磁場(chǎng)傳播。采用小空隙的自屏蔽電感磁芯可以對(duì)后一條傳播路徑進(jìn)行抑制。導(dǎo)線傳播有兩種模式—共模和差模。對(duì)共模傳播的噪聲,可以把PCB上的降壓器懸置(減小與地面間的寄生電容),并在它的輸入輸出端接共模扼流來(lái)進(jìn)行抑制。差模波紋和噪聲采用LC-LPF和Analog Devices公司的調(diào)壓器ADP3301抑制。在260kHz降壓器轉(zhuǎn)換頻率處PLL不工作,VCO(1)近似運(yùn)行在自激勵(lì)狀態(tài)下。有人發(fā)現(xiàn)了來(lái)自電源波紋的260kHz雜散。VCO輸出端的正弦調(diào)頻(FM)雜散功率由下式給出4,5:

其中:

Um=峰值調(diào)制電壓

Fmod=260kHz

Kp=2![]() 14MHz/V為推頻靈敏度

14MHz/V為推頻靈敏度

DC-DC降壓器有一個(gè)20mV的峰值輸出波紋,LC-LPF對(duì)波紋的抑制為34dB,ADP3301對(duì)波紋的抑制為35dB。那么,Um=7![]() V、LVCO(1)=-74dBc,合成器輸出雜散功率比之前高6dB:-68dBc

V、LVCO(1)=-74dBc,合成器輸出雜散功率比之前高6dB:-68dBc

波紋通過(guò)充電泵供電線路傳入VCO調(diào)諧端口。充電泵的電源供應(yīng)抑制率(PSRR)可能大于20dB,但是其調(diào)諧靈敏度KVCO=2![]() 110MHz/V比推頻靈敏度大18dB。因此,調(diào)諧端波紋產(chǎn)生的260kHz雜散水平小于-70dBc。波紋進(jìn)入VCO調(diào)諧端另一條路徑為運(yùn)算放大器(26)的供電線。但由于OP184的電源供應(yīng)抑制率(PSRR)在100-300kHz波段內(nèi)大約為30dB,因此從這條路徑傳輸?shù)妮敵鲭s散為-80dBc。這些雜散合并后得到總的輸出雜散水平為-63dBc。在合成器輸出端降壓器雜散測(cè)量值大約為-65dBc。

110MHz/V比推頻靈敏度大18dB。因此,調(diào)諧端波紋產(chǎn)生的260kHz雜散水平小于-70dBc。波紋進(jìn)入VCO調(diào)諧端另一條路徑為運(yùn)算放大器(26)的供電線。但由于OP184的電源供應(yīng)抑制率(PSRR)在100-300kHz波段內(nèi)大約為30dB,因此從這條路徑傳輸?shù)妮敵鲭s散為-80dBc。這些雜散合并后得到總的輸出雜散水平為-63dBc。在合成器輸出端降壓器雜散測(cè)量值大約為-65dBc。

實(shí)際應(yīng)用結(jié)構(gòu)中的寬頻帶噪聲

為了設(shè)計(jì)最優(yōu)PLL,它的帶寬必須盡可能地設(shè)置在自激勵(lì)VCO相位噪聲與芯片相位噪聲相同的那個(gè)點(diǎn)上。然而在實(shí)際應(yīng)用中,必須考慮供電電源和環(huán)路濾波器元件產(chǎn)生的噪聲。必須得到VCO(1)運(yùn)行在自激勵(lì)狀態(tài)下時(shí),其供電線上電壓噪聲產(chǎn)生的200kHz頻偏相位噪聲。VCO輸出端相位噪聲為:

調(diào)壓器ADP3301在fOS=200kHz處輸出噪聲電壓密度UNS=40nV/![]() 。那么其供電PN為-114dBc/Hz。必須得到VCO(1)調(diào)諧端200kHz,Ufn下總噪聲電壓密度。這種噪聲由七個(gè)相互獨(dú)立的噪聲源源產(chǎn)生—電阻R1至R4所產(chǎn)生噪聲、運(yùn)算放大器等效輸入噪聲電壓和電流。第七個(gè)為調(diào)壓器產(chǎn)生的噪聲,它通過(guò)充電泵后,最小衰減20dB,通過(guò)運(yùn)算放大器后衰減30dB。

。那么其供電PN為-114dBc/Hz。必須得到VCO(1)調(diào)諧端200kHz,Ufn下總噪聲電壓密度。這種噪聲由七個(gè)相互獨(dú)立的噪聲源源產(chǎn)生—電阻R1至R4所產(chǎn)生噪聲、運(yùn)算放大器等效輸入噪聲電壓和電流。第七個(gè)為調(diào)壓器產(chǎn)生的噪聲,它通過(guò)充電泵后,最小衰減20dB,通過(guò)運(yùn)算放大器后衰減30dB。

經(jīng)過(guò)均方根合并后,VCO(1)調(diào)諧端200kHz頻偏總噪聲電壓密度可得:Ufn=7.8nV/![]() 。由式29可得VCO輸出相位噪聲

。由式29可得VCO輸出相位噪聲

PN tune = 20log(KVCOUfn/(![]() 2

2![]() fOS))=-110.3dBc/Hz

fOS))=-110.3dBc/Hz

在“純凈的”供電電源和“純凈的”調(diào)諧電壓下,VCO(1)在200kHz頻偏處有LVCO=-111dBc/Hz。因此,在實(shí)際應(yīng)用結(jié)構(gòu)中,VCO(1)在200kHz頻偏處的總相位噪聲為:

LVCO(1)=10log(antilog(LVCO/10)

+antilog(PN supply/10)

+antilog(PN tune/10))=

-106.7dBc/Hz

芯片相位噪聲等于-107dBc/Hz。如果PLL帶寬設(shè)為200kHz,那么將會(huì)在200kHz頻偏處產(chǎn)生一個(gè)3dB的過(guò)沖。因而把PLL帶寬設(shè)為350kHz,![]() 為

為![]() 。

。

圖13所示為10kHz分辨率帶寬、帶寬跨度為2MHz測(cè)量所得合成器輸出頻譜。與仿真結(jié)果相比,在300到1000kHz頻偏范圍內(nèi)有額外的相位噪聲。由式1來(lái)看,相位噪聲響應(yīng)在350kHz以上應(yīng)該有一個(gè)-20dB/十倍頻程的斜坡。然而途中曲線在300-600kHz范圍內(nèi)是恒定值。這一效應(yīng)由于運(yùn)算放大器和充電泵PSRR在300-600kHz波段內(nèi)減小。

圖13、合成器輸出頻譜

諧波抑制器

接下來(lái)的問(wèn)題就是如何獲高效率,低諧波電平。當(dāng)產(chǎn)生飽和的高諧波分量時(shí)放大器效率最大。諧波濾波器(12)包含帶開(kāi)路短截線的微帶線。它們的長(zhǎng)度為1.5倍、2倍和3倍FOUT頻率對(duì)應(yīng)波長(zhǎng)的1/4,間隔為FOUT波長(zhǎng)的1/4。傳輸線放置在12.5GHz截止頻率波導(dǎo)寬面。波導(dǎo)的窄面放置一個(gè)吸收器,其上有全部短截線的末端。短截線發(fā)射出來(lái)的大諧波信號(hào)被迅速吸收。插入損耗在FOUT、2FOUT和3FOUT處分別為3dB、36dB和40dB。測(cè)量得到的二次諧波水平為-48dBc,三次諧波水平小于-55dBc。輸出功率為+13dBm,總功耗為2.3W。

微音效應(yīng)的抑制

抑制微音效應(yīng)對(duì)機(jī)載設(shè)備非常重要。瓷片電容存在壓電效應(yīng)。如果將它們應(yīng)用在高阻電路,如VCO調(diào)諧端,中則成為微音調(diào)頻源。由于100Hz處的共振,激勵(lì)VCO調(diào)諧端0.13![]() V的壓電電壓會(huì)產(chǎn)生-30dBc輸出雜散。鐵氧體微波隔離器也存在微音效應(yīng)。因?yàn)樗鼈兙?/span>VCO的負(fù)載,所以成為微音調(diào)頻源。

V的壓電電壓會(huì)產(chǎn)生-30dBc輸出雜散。鐵氧體微波隔離器也存在微音效應(yīng)。因?yàn)樗鼈兙?/span>VCO的負(fù)載,所以成為微音調(diào)頻源。

必須量由調(diào)諧端口,供電端口和和負(fù)載反射系數(shù)調(diào)制產(chǎn)生的VCO低頻率調(diào)制PLL抑制。對(duì)于固定和可調(diào)PLL,調(diào)諧端口的調(diào)頻測(cè)量都是很容易的。首先,通過(guò)把充電泵設(shè)置為三態(tài)使PLL不工作。在VCO調(diào)諧端利用一個(gè)大電阻輸入小幅正弦信號(hào)。由此測(cè)量出自激勵(lì)狀態(tài)下雜散相對(duì)水平。下式給出

其中Um和Fmod為調(diào)諧端口的調(diào)制信號(hào)的幅度和頻率。然后把PLL置于工作狀態(tài),測(cè)量出此狀態(tài)下的相對(duì)雜散水平,式子給出如下:

其中s=j2![]() Fmod。20

Fmod。20![]() 表示PLL調(diào)頻抑制。其分別對(duì)固定和可調(diào)PLL計(jì)算。相位項(xiàng)(1+G(s))也計(jì)算得出。圖14、15給出仿真結(jié)果。在500Hz處有一個(gè)大約為100dB的調(diào)頻抑制。在這樣低的電平上測(cè)量會(huì)非常困難的,于是在實(shí)際測(cè)量中采用Fmod=20kHz。對(duì)于兩個(gè)PLL測(cè)量出來(lái)的調(diào)頻抑制均為37-39dB。這與仿真結(jié)果大致相同。

表示PLL調(diào)頻抑制。其分別對(duì)固定和可調(diào)PLL計(jì)算。相位項(xiàng)(1+G(s))也計(jì)算得出。圖14、15給出仿真結(jié)果。在500Hz處有一個(gè)大約為100dB的調(diào)頻抑制。在這樣低的電平上測(cè)量會(huì)非常困難的,于是在實(shí)際測(cè)量中采用Fmod=20kHz。對(duì)于兩個(gè)PLL測(cè)量出來(lái)的調(diào)頻抑制均為37-39dB。這與仿真結(jié)果大致相同。

圖14、固定PLL的調(diào)頻響應(yīng)仿真

圖15、可調(diào)PLL的調(diào)頻響應(yīng)仿真

結(jié)論

本文介紹了機(jī)載頻率合成器的實(shí)用設(shè)計(jì)。一種混合合成器結(jié)構(gòu)可以使芯片相位噪聲性能提升8dB。最佳的實(shí)用合成器結(jié)構(gòu)對(duì)來(lái)自所有源的雜散進(jìn)行抑制,使其輸出水平小于-64dBc。計(jì)算了這些雜散的水平,并且討論了雜散抑制方法。最佳的供電單元結(jié)構(gòu)使設(shè)計(jì)具有功效高、雜散低和體積小的特點(diǎn),但在300-600kHz頻偏范圍內(nèi)有一個(gè)較低的來(lái)自供電電源的額外相位噪聲。仿真和測(cè)量了PLL調(diào)頻抑制。