??? 摘 要: 介紹一種TPC碼迭代譯碼器" title="譯碼器">譯碼器的硬件設計方案,基于軟判決譯碼規(guī)則,采用完全并行規(guī)整的譯碼結構,使用VHDL硬件描述語言,實現(xiàn)了碼率為1/2的(8,4)二維乘積碼迭代譯碼器,并特別通過硬件測試激勵來實時測量所設計迭代譯碼器的誤碼率情況,提出了優(yōu)化設計方案,和傳統(tǒng)的硬件仿真" title="硬件仿真">硬件仿真方法相比大大提高了仿真效率。仿真結果證明該譯碼器有很大的實用性和靈活性。

??? 關鍵詞: TPC碼? 軟判決譯碼? 外信息? 迭代譯碼? VHDL? FPGA

?

??? 1993年伴隨著著名的Turbo碼的提出,法國的RM.Pyndiah于1994年將Turbo軟迭代譯碼的思想應用于早期的乘積碼[1]之中,提出了分組Turbo碼(BTC)[2],即Turbo乘積碼(TPC碼),正是從這個時期開始乘積碼獨特的優(yōu)點再次得到了編碼界的關注。相對于Turbo碼而言,Turbo乘積碼很好地實現(xiàn)了譯碼性能與硬件實現(xiàn)的復雜度的折衷,很容易由硬件實現(xiàn)。近年來一些著名的硬件和芯片制造商相繼開發(fā)出一些針對無線通信應用的乘積碼的編譯碼芯片和相應的IP核,可以說如何有效地設計一個TPC碼的迭代譯碼器已經(jīng)成為目前國內(nèi)外圍繞Turbo碼在無線通信領域中應用的一個重要問題。

??? 本文提出了二維TPC碼的迭代譯碼器的FPGA設計方案,特別建立了FPGA硬件仿真模型" title="仿真模型">仿真模型,大大提高了信道編碼硬件仿真效率,為了評估TPC譯碼器的譯碼性能好壞,通過改變不同信噪比下的輸入激勵,可以分析所設計譯碼器的誤碼率情況。經(jīng)過功能驗證" title="功能驗證">功能驗證,譯碼功能與C程序仿真的功能非常吻合,從而證明了整個設計的合理性,為今后實現(xiàn)更實用、更長碼長和更高碼率的TPC碼譯碼器做了有益的嘗試。

1 編譯碼原理

??? 構造TPC碼的線性分組碼很多,如漢明碼、單校驗碼(SPC)、RS碼和BCH碼等等,目前國際上多采用SPC碼和擴展?jié)h明碼構造。

??? 為了使設計驗證過程不至于繁瑣,方便更加清楚地說明問題,這里假定以簡單的(3,2,2)單校驗碼為成員碼。對于碼長較短、碼塊小的簡單碼型可以回避開RM.Pyndiah提出的復雜的修正Chase譯碼算法[3],而采用Turbo軟迭代譯碼原理,這樣可以降低譯碼復雜度,但譯碼效果肯定會有所下降。為此做了一些有益的設計嘗試。

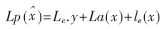

?具體算法采用逐位MAP譯碼規(guī)則,最終目的是要得到信息x的最大似然后驗信息。最終的譯碼結果包含三部分獨立的似然概率估計值。即:信道軟輸出、先驗概率和外信息[4][5],即:

???? ?

?

??? 圖1給出了一個簡單兩維(8,4)TPC碼迭代譯碼的過程。

?????????????

2 電路設計

2.1 迭代譯碼核心

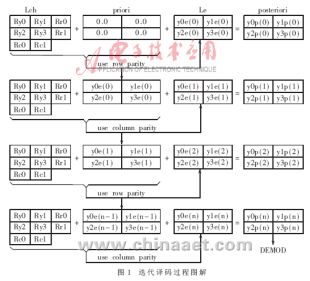

??? 當用FPGA器件實現(xiàn)TPC碼的整體譯碼功能時,迭代譯碼過程的具體實現(xiàn)主要是行和列外信息計算模塊。如圖2所示,附加了若干D觸發(fā)器作為總體控制時序控制模塊,進行數(shù)據(jù)緩沖,保證和協(xié)調(diào)各個譯碼模塊的連續(xù)進行和同步工作。

???????????????????

2.2 功能驗證電路

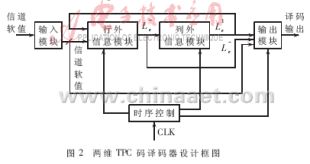

??? 為進一步驗證此二維TPC碼譯碼器的糾錯性能的好壞,把譯碼器的輸出結果和理論輸入進行比較來分析譯碼器的譯碼功能是否完善,特別設計了功能驗證模塊,并編寫了測試激勵。

?圖3為該譯碼器的功能驗證方塊圖,分為譯碼控制與輸入模塊(input)、原始輸入?yún)⒖寄K(senddata)、TPC碼迭代譯碼模塊(TPC decoder)及誤碼率計算分析模塊(Error Counter)。

???????????????????????????

3 仿真波形" title="仿真波形">仿真波形

??? 整個TPC碼譯碼器由上述方案中的幾個下層文件組成了頂層文件。整個設計采用VHDL語言編寫了各個模塊的程序代碼,各個模塊源程序成功通過編譯。程序在Xilinx公司的開發(fā)工具ISE8.1和與Xilinx公司配套的ModelsimXE 6.0a集成仿真工具的環(huán)境下仿真調(diào)試通過。圖4為該(8,4)二維乘積碼的譯碼性能功能仿真波形,其中時鐘信號CLK周期為10MHz,上升沿有效,啟動信號START下降沿有效,為8個時鐘周期。譯碼后4bit信息為:y0d、y1d、y2d、y3d。從圖4中可見數(shù)據(jù)的譯碼輸出仿真測試結果波形。

??????????

????? 基于硬件仿真模塊,在不同的輸入測試激勵文件的控制下,對應不同的信噪比環(huán)境,分別輸入各種不同的激勵,可以從低噪聲一直到非常大的噪聲。圖4為輸入激勵為信噪比9dB時輸出的波形圖,誤碼率計算分析模塊在啟動信號start的上升沿采樣數(shù)據(jù),下降沿則輸出誤碼率統(tǒng)計結果。如圖5所示,在輸入激勵為SNR=9dB時,誤碼率為7/10000。

???????????

??? 可以看出所設計的TPC碼迭代譯碼器具有較好的譯碼效果,通過改變輸入激勵部分參數(shù),可以設計出更多碼型的TPC碼譯碼器,具有較高的實用價值。

4 幾點思考

??? (1)方案中所建立的功能驗證系統(tǒng)是任何信道編碼譯碼器驗證測時通用的。該方案完全改變了傳統(tǒng)方式,非常值得推廣使用。從以往的信道編譯碼的工程實踐看,對于功能仿真測試部分實現(xiàn)方式雖然很多,但是效率低,不直觀。通常采用從最后MODELSIM仿真波形文件中提取具體仿真數(shù)據(jù),然后對所有數(shù)據(jù)進行分析歸納統(tǒng)計,最后得出整個誤碼率情況。這種方法速度慢、精度低。文中所提出的二維乘積碼采用的硬件驗證系統(tǒng)的建立為譯碼器的硬件仿真開拓了一個新的高效率思路,不僅仿真速度快,而且通用性強,可以應用到任何信道糾錯譯碼模塊的硬件仿真測試系統(tǒng)中去,而且不需要人為分析數(shù)據(jù)結果,全部過程從Modelsim仿真波形自動讀出,精確度非常高。采用硬件FPGA仿真誤碼率,不僅比軟件仿真速度快,而且靈活方便,非常值得推廣。

??? (2)該方案可以做更優(yōu)化設計,如圖6所示。進一步延伸這個考慮,如果補充上TPC編碼模塊和信道模塊(AWGN 和Fading)以及軟判決映射器,整個驗證系統(tǒng)將更為通用。

???????????????????

??? 其中信息源模塊由線性反饋移位寄存器LFSR(Linear Feedback Shift Registers)構成,產(chǎn)生(0,1)序列送入TPC碼編碼器產(chǎn)生二維碼塊,隨后來自碼塊的比特數(shù)據(jù)疊加上來自AWGN或是衰落信道模塊產(chǎn)生的噪聲后被軟判決映射器從(0,1)映射為(-1,+1)比特流,經(jīng)過串入并出轉換后并行輸出給TPC碼譯碼器,經(jīng)譯碼器譯出的信息比特將會和原始輸入信息進行異或比較,最后由誤碼率計算模塊輸出誤碼率。

??? 這樣一個TPC碼驗證測試激勵系統(tǒng)提供了快速的硬件仿真模型,非常值得推廣,相比較利用C程序軟件仿真,仿真時間大致為10:1,大大提高了TPC碼性能仿真效率。

??? 如何有效地設計一個TPC碼的譯碼器成為目前圍繞TPC碼的無線通信應用領域的一個重要問題。本文針對短碼、小碼塊的TPC碼迭代譯碼器的FPGA設計,特別建立了TPC 碼迭代譯碼器的硬件仿真模型,大大提高了性能仿真效率,提出了信道編碼譯碼器硬件設計的優(yōu)化設計方案,作為一種有益的探索和嘗試,為下一步實現(xiàn)各種信道編碼譯碼器積累了寶貴經(jīng)驗。該硬件仿真模型的靈活性非常強,通過改變設計中的一些輸入和控制參數(shù),可以設計更多IEEE802.16標準推薦的更實用碼型和迭代次數(shù)的TPC碼。

參考文獻

[1] ELIAS P.Error-free coding,IRE Trans.on Inf.Theory,vol.IT-4,1954.(9):29-37.

[2] PYNDIAH R,GLAVIEUX A,PICART A,et al.Near optimum decoding of product codes,in proc.of IEEE? GLOBECOM′94 Conference,vol.1/3,1994,11~12。

[3] PYNDIAH R.Near optimum decoding of product codes:Block Turbo Codes,IEEE? Trans.on Comm.,vol 46,1998(8).

[4] BERROU C,GLAVIEUX A,THITIMAJSHIMA P.Near?Shannon limit error-correcting coding and decoding:Turbocodes(1),IEEE Int.Conf.on Comm.ICC′93,vol 2/3,1993(5).

[5] 王新梅,肖國鎮(zhèn).糾錯碼-原理與方法(修訂版).西安:西安電子科技大學出版社,2002.