1971年,美國(guó)學(xué)者J.TIerney等人撰寫的《A Digital Frequency Synthesizer》一文首次提出了以全數(shù)字技術(shù),從相位概念出發(fā)直接合成所需波形的一種新合成原理。限于當(dāng)時(shí)的技術(shù),沒(méi)有得到重視,但隨著微電子技術(shù)的迅速發(fā)展,它以有別于其他頻率合成方法的優(yōu)越性能和特點(diǎn)成為現(xiàn)代頻率合成技術(shù)的佼佼者,具體體現(xiàn)在相對(duì)帶寬寬,頻率轉(zhuǎn)換時(shí)間短,頻率分辨率高,輸出相位連續(xù),可產(chǎn)生多種調(diào)制信號(hào),控制靈活方便。因此,對(duì)于正弦信號(hào)發(fā)生器的設(shè)計(jì),可以采用DDS,即直接數(shù)字頻率合成方案實(shí)現(xiàn)。DDS的輸出頻率是數(shù)字可調(diào)的,完全能實(shí)現(xiàn)頻率為1 kHz~10 MHz之間的正弦信號(hào),這是實(shí)際應(yīng)用中產(chǎn)生可調(diào)頻率正弦信號(hào)波形較為理想的方案。實(shí)現(xiàn)DDS常用3種技術(shù)方案:高性能DDS單片電路的解決方案;低頻正弦波DDS單片電路的解決方案;自行設(shè)計(jì)的基于FPGA芯片的解決方案。雖然有的專用DDS芯片的功能也比較多,但控制方式卻是固定的,因此不一定滿足用戶需求。而基于FPGA則可以根據(jù)需要方便地實(shí)現(xiàn)各種比較復(fù)雜的調(diào)頻、調(diào)相和調(diào)幅功能,具有良好的實(shí)用性。專用DDS芯片由于采用特定的集成工藝,內(nèi)部數(shù)字信號(hào)抖動(dòng)很小,可以輸出高質(zhì)量的模擬信號(hào);利用FPGA也能輸出較高質(zhì)量的信號(hào),雖然達(dá)不到專用DDS芯片的水平,但信號(hào)精度誤差非常小,能滿足大多數(shù)信號(hào)源要求。DDS是本系統(tǒng)的關(guān)鍵技術(shù),在介紹本系統(tǒng)之前,先單獨(dú)介紹DDS的原理。

l DDS電路工作原理

1.1 DDS的工作原理

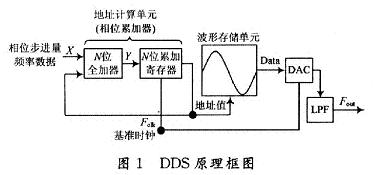

DDS的工作原理是以數(shù)控振蕩器的方式產(chǎn)生頻率、相位可控制的正弦波。如圖1所示,電路一般包括基準(zhǔn)時(shí)鐘、頻率累加器、相位累加器、幅度/相位轉(zhuǎn)換電路、D/A轉(zhuǎn)換器和低通濾波器(LPF)。頻率累加器對(duì)輸入信號(hào)進(jìn)行累加運(yùn)算,產(chǎn)生頻率控制數(shù)據(jù)X(frequency data或相位步進(jìn)量)。相位累加器由N位全加器和N位累加寄存器級(jí)聯(lián)而成,對(duì)代表頻率的二進(jìn)制碼進(jìn)行累加運(yùn)算,是典型的反饋電路,產(chǎn)生累加結(jié)果Y。幅度/相位轉(zhuǎn)換電路實(shí)質(zhì)上是一個(gè)波形寄存器,以供查表使用。讀出的波形數(shù)據(jù)送入D/A轉(zhuǎn)換器和低通濾波器轉(zhuǎn)換成符合要求的模擬信號(hào)。

1.2 具體工作過(guò)程

信號(hào)產(chǎn)生過(guò)程:如圖1所示,N位加法器將頻率控制數(shù)據(jù)X與累加寄存器輸出的累加相位數(shù)據(jù)在時(shí)鐘脈沖Fclk控制下相加,把相加后的結(jié)果Y送至累加寄存器的輸入端。累加寄存器一方面將在上一時(shí)鐘周期作用后所產(chǎn)生的新的相位數(shù)據(jù)反饋到加法器的輸入端,以使加法器在下一時(shí)鐘的作用下繼續(xù)與頻率控制數(shù)據(jù)X相加;另一方面將這個(gè)值作為取樣地址值送入幅度/相位轉(zhuǎn)換電路(即圖1中的波形存儲(chǔ)器),幅度/相位轉(zhuǎn)換電路根據(jù)這個(gè)地址輸出相應(yīng)的波形數(shù)據(jù)。最后經(jīng)D/A轉(zhuǎn)換器和低通濾波器將波形數(shù)據(jù)處理成所需要的模擬波形。相位累加器在基準(zhǔn)時(shí)鐘的作用下,進(jìn)行線性相位累加,當(dāng)相位累加器加滿量時(shí)就會(huì)產(chǎn)生一次溢出,這樣就完成了一個(gè)周期,這個(gè)周期也就是DDS信號(hào)的一頻率周期。 DDS輸出信號(hào)的頻率由下式給定:

![]()

假定基準(zhǔn)時(shí)鐘為70 MHz,累加器為16位,則:

![]()

再假定X=4 096,則Fout=(4 096/65 536)×70=4.375 MHz。

可見(jiàn),通過(guò)設(shè)定相位累加器位數(shù)、頻率控制字X和基準(zhǔn)時(shí)鐘的值,就可以產(chǎn)生任一頻率的輸出。DDS的頻率分辨率定義為:

![]()

由于基準(zhǔn)時(shí)鐘一般固定,因此相位累加器的位數(shù)就決定了頻率分辨率。如上面的例子,相位累加器為16位,那么頻率分辨率就可以認(rèn)為是16位。位數(shù)越多,分頻率越高。

2 正弦信號(hào)發(fā)生器系統(tǒng)結(jié)構(gòu)設(shè)計(jì)及實(shí)現(xiàn)

2.1 系統(tǒng)結(jié)構(gòu)圖

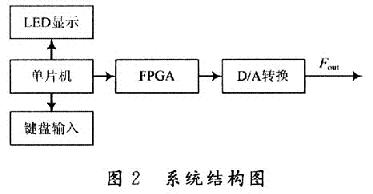

正弦信號(hào)發(fā)生器系統(tǒng)結(jié)構(gòu)圖如圖2所示。

2.2 單元電路

2.2.1 單片機(jī)控制模塊實(shí)現(xiàn)方式

單片機(jī)實(shí)現(xiàn)部分主要處理數(shù)據(jù)輸入及數(shù)據(jù)顯示,此模塊以AT89S51為中心,控制鍵盤輸入和LED顯示,其中鍵盤輸入值作為頻率控制字送給FPGA處理。單片機(jī)的P1口直接與鍵盤連接,無(wú)鍵按下時(shí)為高電平,當(dāng)有鍵按下時(shí)就變?yōu)榈碗娖健?梢栽O(shè)計(jì)鍵1為“0”值鍵、鍵2為“1”值鍵,滿足頻率控制字以二進(jìn)制進(jìn)行輸入;鍵3為輸入確定鍵;鍵4和鍵5為頻率步進(jìn)控制鍵,鍵4為加100 Hz鍵,鍵5為減100 Hz鍵,當(dāng)鍵3按下時(shí)將輸入設(shè)置的頻率控制字以二進(jìn)制數(shù)形式送至P2口,然后通過(guò)串行口輸出并驅(qū)動(dòng)LED靜態(tài)顯示。PO.O和PO.1及PO.2控制數(shù)據(jù)輸出的先后順序。此模塊功能具體實(shí)現(xiàn)可通過(guò)匯編語(yǔ)言編程后下載到單片機(jī)調(diào)試并實(shí)現(xiàn),限于篇幅,具體程序不在此展現(xiàn),只展示設(shè)計(jì)思路。

2.2.2 FPGA處理模塊

(1)FPGA處理模塊控制原理

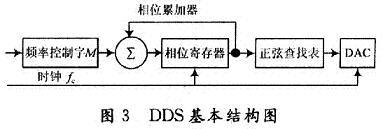

FPGA處理模塊是本系統(tǒng)的核心,系統(tǒng)結(jié)構(gòu)圖中FPGA模塊里的DDS基本結(jié)構(gòu)圖如圖3所示。

圖3中DDS工作原理為:相位累加器由32位加法器與32位累加寄存器級(jí)聯(lián)構(gòu)成。在時(shí)鐘脈沖,fc的控制下,加法器將頻率控制字M與累加寄存器輸出的累加相位數(shù)據(jù)相加,把相加后的結(jié)果送到累加寄存器的數(shù)據(jù)輸入端,以使加法器在下一個(gè)時(shí)鐘脈沖的作用下繼續(xù)與頻率控制字相加。這樣,相位累加器在時(shí)鐘作用下,不斷對(duì)頻率控制字進(jìn)行線性相位累加。由此可以看出,相位累加器在每一個(gè)時(shí)鐘輸入時(shí),把頻率控制字累加一次,相位累加器輸出的數(shù)據(jù)就是合成信號(hào)的相位。

DDS采用改變尋址的步長(zhǎng)來(lái)改變輸出信號(hào)的頻率,步長(zhǎng)即為對(duì)數(shù)字波形查表的相位增量,由累加器對(duì)相位增量進(jìn)行累加,累加器的值作為查表地址,這樣就可把存儲(chǔ)在波形存儲(chǔ)器內(nèi)的波形抽樣值(二進(jìn)制編碼)經(jīng)查找表查出,完成相位到幅值轉(zhuǎn)換,波形存儲(chǔ)器的輸出送到D/A轉(zhuǎn)換器,D/A轉(zhuǎn)換器將數(shù)字量形式的波形幅值轉(zhuǎn)換成所要求合成頻率的模擬量形式信號(hào)。低通濾波器用于濾除不需要的取樣分量,以便輸出頻譜純凈的正弦波信號(hào)。