一.概述

頻率合成主要有三種方法:直接模擬合成法、鎖相環(huán)合成法和直接數(shù)字合成法(Direct Digital Frequency Synthesis,一般簡(jiǎn)稱DDS)。直接模擬合成法利用倍頻、分頻、混頻及濾波,從單一或幾個(gè)參考頻率中產(chǎn)生多個(gè)所需的頻率。該方法頻率轉(zhuǎn)換時(shí)間短,但是體積大、功耗大,目前已基本不被采用。鎖相環(huán)合成法通過(guò)鎖相環(huán)完成頻率的加、減、乘、除運(yùn)算。該方法結(jié)構(gòu)簡(jiǎn)化、便于集成,且頻譜純度高,目前使用比較廣泛,但存在高分辨率和快轉(zhuǎn)換速度之間的矛盾,一般只能用于大步進(jìn)頻率合成技術(shù)中。DDS 是近年來(lái)迅速發(fā)展起來(lái)的一種新的頻率合成方法。該方法與前兩種方法相比,這種方法簡(jiǎn)單可靠、控制方便,且具有很高的頻率分辨率和轉(zhuǎn)換速度,可以實(shí)現(xiàn)可編程和全數(shù)字化,控制靈活方便,并具有極高的性價(jià)比。

目前雖然有很多專用DDS 芯片,但控制方式卻是固定的,在某些場(chǎng)合,專用的DDS 芯片在控制方式、置頻速率等方面與系統(tǒng)的要求差距很大,不一定是我們所需要的。而用高性能的FPGA 器件設(shè)計(jì)符合自己需要的DDS 電路是一個(gè)很好的方法。可編程邏輯器件以其速度高、規(guī)模大、可編程,以及有強(qiáng)大EDA軟件支持等特性,十分適合實(shí)現(xiàn)DDS 技術(shù)。

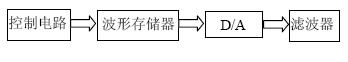

DDS 的原理框圖如圖1,控制電路按照一定的地址關(guān)系從存儲(chǔ)器中讀取數(shù)據(jù),進(jìn)行數(shù)摸轉(zhuǎn)換,就可以得到一定頻率的輸出波形,再通過(guò)濾波器對(duì)輸出波形進(jìn)行平滑處理。

圖1 DDS 原理框圖

基于FPGA 的DDS 控制電路的實(shí)現(xiàn)有采用相位累加和比例乘法器兩種方案,下面將分別介紹。

二.采用相位累加控制實(shí)現(xiàn)DDS

1.工作原理

電路如圖2 所示,相位累加器由N位加法器與N位相位寄存器級(jí)聯(lián)構(gòu)成,類似于一個(gè)簡(jiǎn)單的加法器。每來(lái)一個(gè)時(shí)鐘脈沖fclk,加法器就將頻率控制字M 與相位寄存器輸出的累加相位數(shù)據(jù)相加,然后把相加后的結(jié)果送至相位寄存器輸入端。相位寄存器在下一個(gè)時(shí)鐘的作用下就將加法器在上一個(gè)時(shí)鐘作用后產(chǎn)生的新相位數(shù)據(jù)反饋到加法器的輸入端,以使加法器繼續(xù)將相位數(shù)據(jù)與頻率控制字M 相加。頻率控制字M 由累加器累加以得到相應(yīng)的這個(gè)相位數(shù)據(jù)將作為取樣地址值送入的波形存儲(chǔ)器,波形存儲(chǔ)器根據(jù)這個(gè)地址輸出相應(yīng)的波形數(shù)據(jù)。最后經(jīng)D/A 轉(zhuǎn)換器和低通濾波器將波形數(shù)據(jù)轉(zhuǎn)換成所需要的模擬波形。

圖2 相位累加器

當(dāng)相位累加器累加滿量時(shí),就會(huì)產(chǎn)生一次溢出,完成一個(gè)周期性的動(dòng)作,這個(gè)周期就是合成信號(hào)的一個(gè)周期,累加器的溢出頻率也就是DDS 的合成信號(hào)頻率。

根據(jù)以上原理,輸出信號(hào)頻率與累加器時(shí)鐘fclk, 累加器位數(shù)N,相位增量M 的關(guān)系為f0=(fclk, • M )/ 2N 。其中:采樣點(diǎn)為2N/M,若fclk,一定,f0 越高,采樣點(diǎn)數(shù)越少;最小步進(jìn)為fclk/2N,達(dá)到最小步進(jìn)值時(shí),采樣點(diǎn)數(shù)最多。設(shè)計(jì)中根據(jù)所要求的最高頻率和最少采樣點(diǎn)數(shù)可確定需要的fclk;根據(jù)最小步進(jìn)和fclk,可確定N 的位數(shù);根據(jù)最高輸出頻率和最小步進(jìn)可確定M 的位數(shù)。

2.設(shè)計(jì)實(shí)現(xiàn)

如要求設(shè)計(jì)產(chǎn)生頻率范圍為0HZ~~160KHZ,頻率的最小步進(jìn)為5HZ 的信號(hào)。

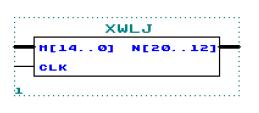

根據(jù)公式可計(jì)算出fclk、N、和M 。f0 若達(dá)到160KHZ,采樣點(diǎn)數(shù)達(dá)64 點(diǎn),則累加器時(shí)鐘fclk 為不小于10.24MHZ;為實(shí)現(xiàn)5HZ 的步進(jìn),此時(shí)采樣點(diǎn)數(shù)最多,有 5= fclk / 2N ,得到N=21,即累加器為21 位;最終輸出頻率與相位增量M 的關(guān)系為f0 =5M,由于最高達(dá)到160KHZ,則M≥160000/5=32000,而215=32768,所以選擇相位增量的位數(shù)為15 位。相位累加器XWLJ 采用VHDL 設(shè)計(jì),其高九位給波形存儲(chǔ)器作為地址,根據(jù)以上要求的VHDL 設(shè)計(jì),編譯成功后自動(dòng)生成的邏輯符號(hào)如圖3 所示。

圖3 XWLJ 邏輯符號(hào)

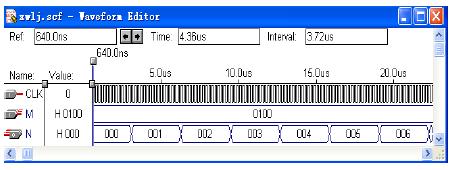

若當(dāng)頻率控制字為M=0100H 時(shí),其仿真波形如圖4 所示。可以看出,N 的輸出高九位按設(shè)計(jì)要求實(shí)現(xiàn)了相位累加的功能。

圖4 相位累加器仿真波形

三.采用比例乘法器控制實(shí)現(xiàn)DDS

1.比例乘法器工作原理

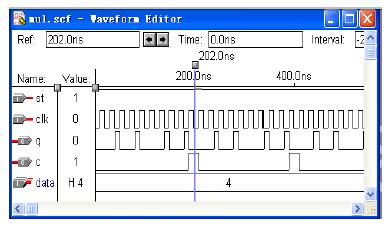

根據(jù)硬件比例乘法器(CC14527)的原理,我們對(duì)其進(jìn)行VHDL 設(shè)計(jì)實(shí)現(xiàn)。其完成的功能為:ST為片選信號(hào),當(dāng)ST 有效時(shí),在CLK 每十個(gè)脈沖中輸出端Q 將輸出DATA[3..0](0~9)個(gè)脈沖,同時(shí)在CLK 滿10 個(gè)脈沖時(shí),C 端產(chǎn)生一個(gè)脈沖控制信號(hào)。在Max+plusⅡ下編譯成功后自動(dòng)生成的邏輯符號(hào)MUL 如圖5 所示。其仿真波形如圖6,可以看出,當(dāng)data 為4,在clk 十個(gè)脈沖中, q 輸出4 個(gè)脈沖,在CLK 滿10 個(gè)脈沖時(shí),C 端產(chǎn)生一個(gè)脈沖控制信號(hào),完全實(shí)現(xiàn)了比例乘法器功能。

圖5 比例乘法器的邏輯符號(hào)

圖6 比例乘法器仿真波形

2 設(shè)計(jì)實(shí)現(xiàn)

在兩個(gè)比例乘法器級(jí)聯(lián)時(shí),令高位輸入數(shù)據(jù)q0,低位輸入數(shù)據(jù)q1,在每10 個(gè)脈沖中高位輸出q0個(gè)脈沖,同時(shí)高位C 端禁止低位CLK 進(jìn)入,當(dāng)高位滿10 個(gè)脈沖后高位C 端允許低位CLK 進(jìn)入1 個(gè)脈沖,這樣在100 個(gè)脈沖中整體上將輸出10q0+q1 個(gè)脈沖。于是在n 級(jí)級(jí)聯(lián)后,若輸入頻率為f,則輸出脈沖頻率為[10 n-1q0+10n-2q1+…+10q(n-2)+q(n-1)]f/10n。

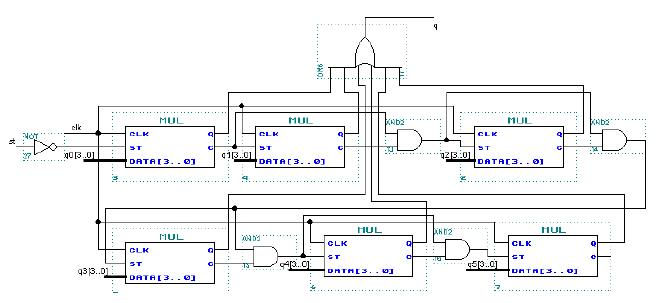

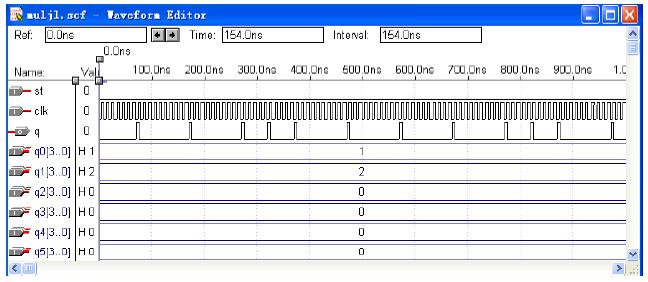

在Max+plusⅡ軟件環(huán)境下,對(duì)上面采用VHDL 語(yǔ)言已經(jīng)實(shí)現(xiàn)的比例乘法器模塊MUL,采用6 級(jí)級(jí)聯(lián)產(chǎn)生DDS 控制電路頂層圖如圖7 所示, 為了清楚地顯示設(shè)計(jì)功能,仿真時(shí)q0 取1,q1 取2,其仿真波形如圖8 所示,可以看出,在CLK 的100 個(gè)脈沖中,q 輸出12 個(gè)脈沖。在給定輸入下,完全實(shí)現(xiàn)了設(shè)計(jì)的功能。

圖7 MUL 級(jí)聯(lián)構(gòu)成的DDS 控制電路

圖8 MUL 級(jí)聯(lián)構(gòu)成的DDS 控制電路的仿真波形

若在單片機(jī)的控制下,F(xiàn)PGA 接收單片機(jī)傳送過(guò)來(lái)的用戶要求的波形數(shù)據(jù),及其頻率數(shù)據(jù),并送到FPGA 以產(chǎn)生所需要的輸出頻率值。若時(shí)鐘信號(hào)為16MHz 時(shí),則產(chǎn)生的頻率為實(shí)際所置頻率的16 倍。在用戶給定某一頻率后,通過(guò)單片機(jī)將其乘8 后再送給FPGA,乘法器再將其擴(kuò)大16 倍,得到用戶預(yù)置頻率128 倍頻,故可以對(duì)波形的采樣點(diǎn)達(dá)128 個(gè),提高波形準(zhǔn)確度,很容易實(shí)現(xiàn)低值的頻率步進(jìn),步進(jìn)可以降低到1Hz。

3. 結(jié)論

實(shí)踐證明,通過(guò)FPGA 實(shí)現(xiàn)的DDS 控制電路與其它的控制芯片如單片機(jī)等相結(jié)合,可以準(zhǔn)確、靈活和方便地實(shí)現(xiàn)任意信號(hào)發(fā)生電路的設(shè)計(jì)。 以上兩種控制方案,只要累加器位數(shù)和比例乘法器級(jí)聯(lián)足夠多,就可以實(shí)現(xiàn)頻率的步進(jìn)小,產(chǎn)生的頻率信號(hào)準(zhǔn)確,穩(wěn)定性好,頻率的分辨率高,頻率轉(zhuǎn)換快,容易控制。FPGA 的功能完全取決于設(shè)計(jì)需求,具有相當(dāng)大的靈活性,比購(gòu)買專用DDS 芯片具有很高的性價(jià)比。基于FPGA 的DDS 控制技術(shù),將在現(xiàn)代化電子系統(tǒng)和儀器儀表工業(yè)等領(lǐng)域廣泛應(yīng)用。

本文作者創(chuàng)新點(diǎn):在本文中,給出了兩種基于FPGA 的DDS 控制電路,增加了設(shè)計(jì)的選擇性,從而可以根據(jù)設(shè)計(jì)外圍電路要求,選擇一種更適合于系統(tǒng)設(shè)計(jì)的DDS 控制電路,可以使設(shè)計(jì)更加靈活、方便,易于實(shí)現(xiàn)。

參考文獻(xiàn):

[1] 黃正謹(jǐn). CPLD 系統(tǒng)設(shè)計(jì)入門與應(yīng)用 [M].北京.電子工業(yè)出版社,2002

[2] 侯伯亨 顧新. VHDL 硬件描述語(yǔ)言與數(shù)字邏輯電路設(shè)計(jì). [M].西安. 西安電子科技大學(xué)出版社,1999

[3] 高速雷達(dá)數(shù)字信號(hào)發(fā)生器的FPGA 設(shè)計(jì)與實(shí)現(xiàn)技巧. [J].微計(jì)算機(jī)信息,2006 年,第3-2 期,166-168 頁(yè)

[4] 李景華 杜玉遠(yuǎn).可編程邏輯器件及EDA 技術(shù). [M].沈陽(yáng).東北大學(xué)出版社.2000