隨著現(xiàn)代電子技術(shù)的不斷發(fā)展,在通信系統(tǒng)中往往需要在一定頻率范圍內(nèi)提供一系列穩(wěn)定和準(zhǔn)確的頻率信號(hào),一般的振蕩器己不能滿足要求,這就需要頻率合成技術(shù)。直接數(shù)字頻率合成(Direct DIGITAL Frequency Synthesis,DDS)是把一系列數(shù)據(jù)量形式的信號(hào)通過D/A轉(zhuǎn)換器轉(zhuǎn)換成模擬量形式的信號(hào)合成技術(shù)。DDS具有相對(duì)帶寬寬、頻率轉(zhuǎn)換時(shí)間短、頻率分辨率高、輸出相位連續(xù)、可產(chǎn)生寬帶正交信號(hào)及其他多種調(diào)制信號(hào)等優(yōu)點(diǎn),已成為現(xiàn)代頻率合成技術(shù)中的姣姣者。目前在高頻領(lǐng)域中,專用DDS芯片在控制方式、頻率控制等方面與系統(tǒng)的要求差距很大,利用FPGA來設(shè)計(jì)符合自己需要的DDS系統(tǒng)就是一個(gè)很好的解決方法。

現(xiàn)場(chǎng)可編程門陣列(FPGA)器件具有工作速度快、集成度高、可靠性高和現(xiàn)場(chǎng)可編程等優(yōu)點(diǎn),并且FPGA支持系統(tǒng)現(xiàn)場(chǎng)修改和調(diào)試,由此設(shè)計(jì)的DDS電路簡(jiǎn)單,性能穩(wěn)定,也基本能滿足絕大多數(shù)通信系統(tǒng)的使用要求。

1 DDS的結(jié)構(gòu)原理

DDS的基本原理是利用有限的離散數(shù)據(jù),通過查表法得到信號(hào)的幅值,通過數(shù)模轉(zhuǎn)換器D/A后生成連續(xù)波。DDS的原理框圖如圖1所示。

其中:頻率控制字為fword;相位累加器的位數(shù)為N。相位累加器以步長(zhǎng)fword做累加,產(chǎn)生所需的頻率控制數(shù)據(jù);把得到的頻率控制數(shù)據(jù)作為地址對(duì)ROM存儲(chǔ)器進(jìn)行尋址。數(shù)據(jù)存儲(chǔ)器(ROM)實(shí)質(zhì)是一個(gè)相位/幅度轉(zhuǎn)換電路,ROM中存儲(chǔ)二進(jìn)制碼表示所需合成信號(hào)的相位/幅度值,相位寄存器每尋址一次ROM,就輸出一個(gè)相對(duì)應(yīng)的信號(hào)相位/幅度值。

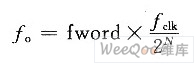

理想情況下,累加器的N位全部用來尋址時(shí),DDS的合成頻率為:

式中:fword為頻率控制字;N為相位累加器位數(shù);fclk為輸入時(shí)鐘。當(dāng)fworld=1時(shí),得DDS的最小分辨率。如果改變頻率控制字,就可以改變合成的頻率的頻偏。

2 DDS調(diào)頻系統(tǒng)在FPGA中的實(shí)現(xiàn)

2.1 累加控制模塊的設(shè)計(jì)

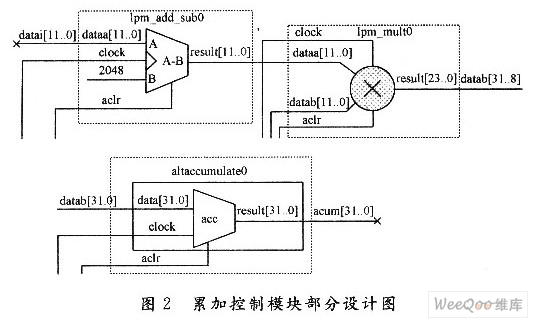

累加控制模塊通過調(diào)用QuartusⅡ中模塊化庫(kù)LPM進(jìn)行設(shè)計(jì)。即由加法器lpm_add_sub和乘法器lpm_mult及累加器altaccumulate模塊構(gòu)成。若要求DDS系統(tǒng)精度高,相位累加器的位數(shù)N須較大。現(xiàn)在大多數(shù)專用的DDS芯片的位數(shù)都在24~32位之間,這里取N=32。累加控制模塊如圖2所示。

ADC轉(zhuǎn)換芯片處理后的8位數(shù)字信號(hào),為了使DDS合成的頻率較大,末尾補(bǔ)4個(gè)O作為參數(shù)化模塊lpm_add_sub的12位輸入datai。由于ADC信號(hào)輸出的是8位二進(jìn)制偏移碼,與計(jì)算機(jī)處理的二進(jìn)制補(bǔ)碼形式不同,需將二進(jìn)制偏移碼轉(zhuǎn)換成二進(jìn)制補(bǔ)碼,在這里與另一路輸入信號(hào)常數(shù)2 048做減法,就能達(dá)到求補(bǔ)的目的,并輸出12位有符號(hào)數(shù)。

12位的輸出接入lpm_mult模塊,lpm_mult的另一路輸入為12位任意數(shù)輸入。乘法器的輸出直接影響累加器累加相位的速度。當(dāng)乘以一個(gè)比較大的數(shù),則頻率變化加快。

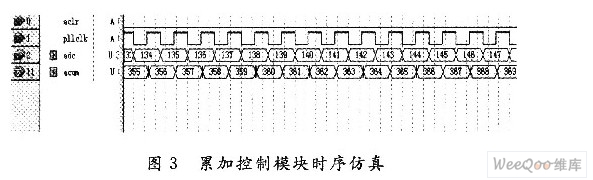

同理,為了使合成頻率較大,乘法器的24位輸出在末尾補(bǔ)O成為32位數(shù)datab送到累加模塊altaccumulate中。為了節(jié)省ROM容量,最后取altaccumulate輸出的高10位作為ROM查找表的地址信號(hào)。累加控制模塊的時(shí)序仿真如圖3所示。

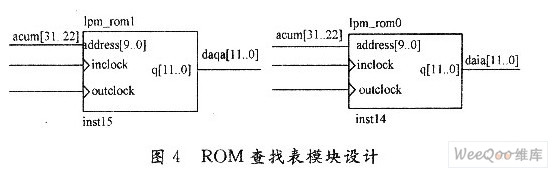

2.2 ROM查找表的設(shè)計(jì)

針對(duì)不同的可編程器件,ROM查找表的設(shè)計(jì)采用的方法也不相同。主要是基于lpm_rom和VHDL選擇語句這兩種方法。使用lpm_rom的波形存儲(chǔ)表只需要產(chǎn)生數(shù)據(jù)文件*.mif,然后直接在定制lpm_rom時(shí),添加數(shù)據(jù)文件即可。不過這種方法在FPGA支持內(nèi)部嵌入式陣列塊(EAB)時(shí)才可以使用;使用VHDL選擇語句比較直觀,但當(dāng)輸入數(shù)據(jù)量大的時(shí)候,這種方法是比較繁瑣的。此次設(shè)計(jì)采用第一種方法。

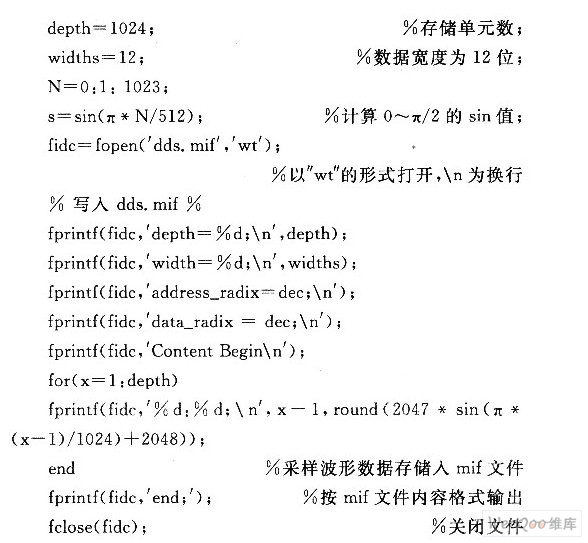

mif文件是在編譯和仿真過程中作為存儲(chǔ)器(ROM或RAM)初始化輸入的文件,即memory initializatiON file。創(chuàng)建mif文件的方式有很多種,在這次設(shè)計(jì)中,在Matlab中采用C語言來生成mif文件。mif文件編寫格式如下:

通常相位累加器的位數(shù)N很大,實(shí)際設(shè)計(jì)中受到體積和成本的限制。為了節(jié)省ROM的容量采用相位截?cái)嗟姆椒ǎ话阒蝗±奂悠鬏敵龅母邘孜蛔鳛镽OM的尋址地址。設(shè)計(jì)中取累加結(jié)果的高10(M=10)位來進(jìn)行查表,也就是說正余弦ROM有210=1 024個(gè)尋址地址,數(shù)據(jù)寬度為12。如圖4所示,設(shè)計(jì)了2個(gè)lpm_rom模塊,分別是sin波形存儲(chǔ)器和cos波形存儲(chǔ)器。

3 單片機(jī)控制電路

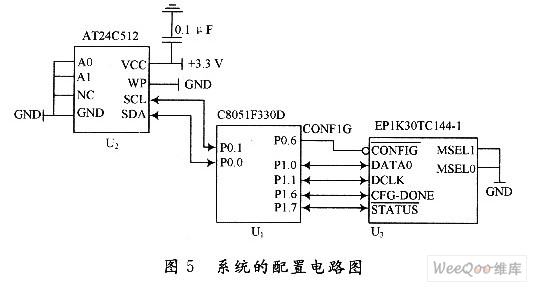

此次選擇的FPGA芯片為Altera公司的ACEXlK系列的EPlK30TTl44-2。它可以采用專用的配置器件來配置,也可以采用單片機(jī)來配置。前者價(jià)格昂貴,而且專用配置器件的ROM為一次性編程,不易實(shí)現(xiàn)FPGA的系統(tǒng)功能轉(zhuǎn)換。采用單片機(jī)C8051F330D對(duì)FPGA進(jìn)行被動(dòng)串行(PS方式)配置,使用可多次修改的AT24C512(E2PROM)作為配置文件存儲(chǔ)器,真正做到“現(xiàn)場(chǎng)可編程”,對(duì)提高生產(chǎn)率、降低生產(chǎn)成本均有好處。

系統(tǒng)的配置電路如圖5所示。其電路的工作過程為:經(jīng)QuartusⅡ編譯生成的配置文件(.rbf),利用PC機(jī)端的控制程序,通過PC機(jī)的串行通信口,經(jīng)U1存儲(chǔ)在U2中,U1再根據(jù)系統(tǒng)的要求通過P0.6,P1.O,P1.1,P1.6和P1.7等5個(gè)I/O口將其存儲(chǔ)在U2中的配置數(shù)據(jù)下載到電路中的FPGA器件U3中。PC機(jī)的控制程序在此略。

4 設(shè)計(jì)結(jié)果

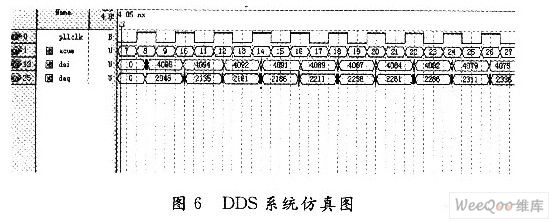

累加控制器、ROM查找表組成一個(gè)整體,實(shí)現(xiàn)了一個(gè)基本的DDS系統(tǒng)。DDS系統(tǒng)的最后仿真結(jié)果如圖6所示。

圖6中的pllclk,acum,dai,daq分別代表時(shí)鐘輸入、累加輸出及正弦波和余弦波輸出。把O~2π的相位分成3FF段,取出相應(yīng)的幅度值存儲(chǔ)于ROM中。ROM中存儲(chǔ)數(shù)據(jù)如下,相位數(shù)據(jù)(O~3FF),幅度數(shù)據(jù)(O~FFF)。從仿真圖可以看出dai[11..O]輸出從EFF~FFF~0~EFF變化,daq[11..O]輸出從FFF~O~FFF變化。最后通過單片機(jī)配置FPGA運(yùn)行,把得出的信號(hào)通過D/A轉(zhuǎn)換和濾波能夠得到所需的正弦波和余弦波信號(hào)。

5 結(jié)語

給出了基于FPGA的DDS設(shè)計(jì)的實(shí)現(xiàn)方案。通過仿真分析可以看出,DDS輸出信號(hào)具有如下特點(diǎn):

(1)頻率穩(wěn)定性好,轉(zhuǎn)換時(shí)間短,分辨率高,相位變化連續(xù)。

(2)設(shè)計(jì)者只需要通過改變測(cè)試輸入數(shù)據(jù),就能夠快速準(zhǔn)確地實(shí)現(xiàn)不同波形并且驗(yàn)證正確性,使得測(cè)試工作更加全面高效,從而提高了調(diào)試效率和成功率。

(3)整個(gè)信號(hào)實(shí)現(xiàn)過程較為簡(jiǎn)單,實(shí)用性較強(qiáng)。

限于實(shí)驗(yàn)條件,此次設(shè)計(jì)在降低相位截?cái)嗾`差等方面仍有改進(jìn)的空間,還可以進(jìn)一步優(yōu)化,限于篇幅,在此不多做介紹。