摘 要: 討論了一種HDLC協(xié)議數(shù)據(jù)轉(zhuǎn)發(fā)的全自動硬件設(shè)計。在SDH產(chǎn)品的ECC接口中采用硬件實(shí)現(xiàn)" title="硬件實(shí)現(xiàn)">硬件實(shí)現(xiàn),通過自動控制BD的方式,實(shí)現(xiàn)HDLC協(xié)議的數(shù)據(jù)重新打包轉(zhuǎn)發(fā)、錯誤處理、重發(fā)幀數(shù)據(jù)等操作,不必CPU干預(yù)。該設(shè)計實(shí)現(xiàn)了兩個ECC口收發(fā)全雙工、8個DCC口點(diǎn)對點(diǎn)同時收發(fā)的高速率、多通道" title="多通道">多通道設(shè)計。

關(guān)鍵詞: ECC HDLC BD

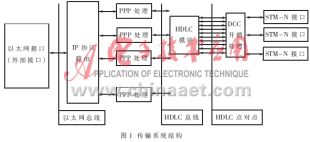

在傳輸產(chǎn)品中,IP over SDH的基本思路,是將IP數(shù)據(jù)通過點(diǎn)到點(diǎn)協(xié)議(PPP)直接映射到SDH幀,從而省掉了中間復(fù)雜的ATM層。具體作法是先把IP數(shù)據(jù)報封裝進(jìn)PPP分組,然后再利用高級數(shù)據(jù)鏈路" title="鏈路">鏈路控制規(guī)程HDLC按照RFC1662的規(guī)定組幀,最后將字節(jié)同步映射進(jìn)SDH包中,加上相應(yīng)的SDH開銷置入STM-N幀中。IP over SDH簡單的系統(tǒng)結(jié)構(gòu)如圖1所示,其中PPP層的功能包括IP多協(xié)議封裝、差錯檢驗(yàn)和鏈路初始化控制,而HDLC為PPP封裝的IP數(shù)據(jù)包提供定界,并用01111110表示一幀的開始和結(jié)束。

本文討論如何用全自動硬件方式實(shí)現(xiàn)圖1中所示的HDLC模塊。

1 傳統(tǒng)的CPU實(shí)現(xiàn)方式

在圖1中,HDLC模塊實(shí)現(xiàn)一個HDLC總線到多個點(diǎn)對點(diǎn)HDLC接口之間的數(shù)據(jù)轉(zhuǎn)發(fā)。將HDLC總線的接口稱為ECC口,HDLC點(diǎn)對點(diǎn)接口稱為DCC口。傳統(tǒng)的實(shí)現(xiàn)方法如圖2所示,是若干HDLC控制器芯片加一塊CPU實(shí)現(xiàn)ECC到DCC的數(shù)據(jù)轉(zhuǎn)發(fā)功能。CPU通過軟件配置,向HDLC幀中插入或提取用戶自定義的10個字節(jié)(包括源地址、目標(biāo)地址、DCC端口號、幀長度等)。以下行為例,HDLC控制器在ECC接口接收數(shù)據(jù)后,向CPU申請使用SRAM中的緩沖區(qū),CPU進(jìn)行仲裁,分配緩沖區(qū)描述符BD,數(shù)據(jù)就可以存放在SRAM中。CPU在這些數(shù)據(jù)發(fā)送時需要指定DCC通道。由于數(shù)據(jù)量較大,每一幀都要進(jìn)行BD的處理,且數(shù)據(jù)申請導(dǎo)致中斷處理頻繁,軟件很容易出錯。

另外,隨著單板集成度的提高,ECC接口的數(shù)據(jù)量越來越大,DCC接口的通道也越來越多。如果采用傳統(tǒng)的CPU實(shí)現(xiàn)方式,就必須不斷增加HDLC控制器,所要求的CPU性能也越來越高,這在技術(shù)上難以實(shí)現(xiàn),成本上也不能接受,因而必須確定一種更經(jīng)濟(jì)、有效的技術(shù)方式來實(shí)現(xiàn)大容量、高效率、低成本的ECC轉(zhuǎn)發(fā)技術(shù)。采用硬件方式,無須或盡量減少CPU的干預(yù),在ECC接口實(shí)現(xiàn)自動的HDLC數(shù)據(jù)轉(zhuǎn)發(fā)。

筆者的目的是將HDLC控制器和CPU的大部分功能用硬件實(shí)現(xiàn),在整個運(yùn)作過程中,不需要CPU實(shí)時協(xié)助,可實(shí)現(xiàn)全自動控制,CPU只需在開始進(jìn)行一些初始化和配置工作,同時為CPU提供一些統(tǒng)計信息,方便CPU了解模塊數(shù)據(jù)傳送的性能。

2 全自動硬件結(jié)構(gòu)設(shè)計

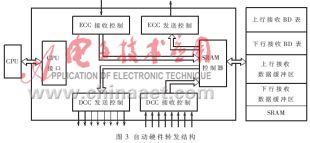

硬件結(jié)構(gòu)如圖3所示,可劃分為六大塊:ECC接口的發(fā)送模塊" title="發(fā)送模塊">發(fā)送模塊、ECC接口的接收模塊" title="接收模塊">接收模塊、DCC接口的發(fā)送模塊、DCC接口的接收模塊、SRAM控制器和CPU接口。

ECC_TX控制:

·仲裁DCC_RX發(fā)過來的數(shù)據(jù)申請;

·從SRAM內(nèi)讀取數(shù)據(jù)到內(nèi)部;

·按照要求添加前10個字節(jié)的信息;

·按照協(xié)議產(chǎn)生新的16位CRC;

·按照協(xié)議發(fā)送數(shù)據(jù);

·按照協(xié)議進(jìn)行重發(fā)操作;

·在操作正確完成后,更新BD和發(fā)送指針。

??? ECC_RX控制:

·實(shí)時監(jiān)控HDLC總線上的變化;

·解析正確的HDLC數(shù)據(jù)包,進(jìn)行CRC檢查;

·接收屬于本地址的數(shù)據(jù)包到SRAM內(nèi);

·在發(fā)生錯誤的情況下,放棄已經(jīng)存入SRAM內(nèi)的數(shù)據(jù);

·在數(shù)據(jù)包正確接收到SRAM之后,產(chǎn)生新BD并更新接收指針。

DCC_RX控制:

·接收的邏輯有8組,可同時接收;

·實(shí)時監(jiān)控HDLC點(diǎn)對點(diǎn)的數(shù)據(jù)變化;

·解析正確的HDLC數(shù)據(jù)包,進(jìn)行CRC檢查;

·接收數(shù)據(jù)包到SRAM內(nèi);

·在發(fā)生錯誤的情況下,放棄已經(jīng)存入SRAM內(nèi)的數(shù)據(jù);

·在數(shù)據(jù)包正確接收到SRAM之后,產(chǎn)生新BD并更新接收指針。

DCC_TX控制:

·發(fā)送是由自己控制,只需一套邏輯,8個通道輪流發(fā)送;

·判斷是否有新的數(shù)據(jù)要發(fā)送(判斷發(fā)送指針是否與接收指針一致);

·從SRAM內(nèi)讀取數(shù)據(jù)到內(nèi)部;

·分析前10個字節(jié)的信息,決定8個發(fā)送端口的其中1個發(fā)送;

·去除前10個字節(jié)的信息;

·按照協(xié)議產(chǎn)生新的16位CRC;

·按照協(xié)議發(fā)送數(shù)據(jù);

·在操作正確完成之后,更新BD和發(fā)送指針。

SRAM控制器:

·這一部分實(shí)現(xiàn)數(shù)據(jù)的存取,ECC接收和發(fā)送各1個,DCC接收8個,DCC發(fā)送1個,共有11個數(shù)據(jù)申請;

·考慮到數(shù)據(jù)流量,SRAM采用16位寬。

CPU接口:

·配置前10個字節(jié)的信息,設(shè)置源地址和目標(biāo)地址;

·復(fù)位通道;

·提供統(tǒng)計信息,供CPU分析運(yùn)作情況。

3 數(shù)據(jù)流

(1)上行數(shù)據(jù)流

如圖4所示,DCC接收到的數(shù)據(jù)(8個同時)→正確數(shù)據(jù)存放于SRAM內(nèi)→數(shù)據(jù)取出,添加10字節(jié),從ECC_TX發(fā)送出去。

(2)下行數(shù)據(jù)流

如圖5所示,HDLC總線的數(shù)據(jù)→地址匹配且正確的數(shù)據(jù)存到SRAM內(nèi)→數(shù)據(jù)取出,從DCC_TX的其中一個端口發(fā)送出去。

4 CPU干預(yù)程度分析和性能分析

(1) 系統(tǒng)使能后硬件即可正常工作,不需要CPU任何配置,相當(dāng)于一個自動的微引擎;

(2) 發(fā)送部分不受寄存器控制,始終在運(yùn)作,通過與接收的BD指針比較決定有沒有數(shù)據(jù)要發(fā)送;同理,接收部分通過BD指針的比較決定SRAM中還有沒有BD空間存放數(shù)據(jù),通過BUF指針比較決定要不要存放數(shù)據(jù);

(3) 接收部分和發(fā)送部分有一個共同的BD和BUF基準(zhǔn)地址,有一個各自初始值為0的指針,接收部分每接收一幀數(shù)據(jù),指針加2,發(fā)送部分可以看到這個指針的變化;

(4) 通過BD的結(jié)構(gòu),可以完成接收與發(fā)送部分關(guān)于數(shù)據(jù)幀的長度通知;接收部分收到一幀,將統(tǒng)計下來的幀長度存放在BD中,發(fā)送部分讀到BD中的幀長度,按該長度向SRAM申請數(shù)據(jù);

(5) 通過wrap設(shè)置,可以完成自動檢測空間和返回緩沖區(qū)起始地址,重用緩沖區(qū);

(6) 錯誤處理可以自動恢復(fù)和重發(fā),只有發(fā)生致命錯誤,如下溢時,才需要CPU對系統(tǒng)進(jìn)行復(fù)位;

(7) 如果考慮最差情況下的速率,最高速度是5MHz(ECC_HDLC接口),現(xiàn)在SRAM采用16位操作,并且FIFO只有一級,則訪問頻率為5MHz/16,一次SRAM訪問需要5個時鐘,此時最壞情況是其它9個接口也同時申請數(shù)據(jù)操作(共11個接口,ECC_HDLC占兩個接口,但在5MHz情況下這兩個接口只能有一個在運(yùn)作之中)。此時系統(tǒng)時鐘必須滿足以下條件才不會產(chǎn)生下溢錯誤: 5MHz/16<sys_clk/(9×5+5),其中(9×5+5)為9個其它設(shè)備的數(shù)據(jù)申請以及它自身數(shù)據(jù)操作需要的時間。此時得到的系統(tǒng)最小時鐘為:15.625MHz。這個速率對FPGA的硬件實(shí)現(xiàn)來說,是毫無困難的。

本系統(tǒng)實(shí)現(xiàn)SDH產(chǎn)品中ECC接口到開銷處的數(shù)據(jù)交換,以HDLC協(xié)議實(shí)現(xiàn)ECC和DCC兩邊的數(shù)據(jù)傳送,整個傳送過程不需要CPU實(shí)時控制。采用該設(shè)計,可不再使用多個HDLC控制器,CPU可由原來的高性能改為低檔CPU,極大地降低成本,同時可具有良好的擴(kuò)展性。該設(shè)計采用Xilinx的Spartan 600E實(shí)現(xiàn),已成功在產(chǎn)品中應(yīng)用。

參考文獻(xiàn)

1 ISO/IEC 3309,1993,Information technology—Telecommuni-cations and information exchange bet-ween systems—Highlevel data link con-trol(HDLC) procedures—Frame structure

2 文冠果. 一種可重用的SoC通訊微引擎結(jié)構(gòu)設(shè)計.微電子學(xué)與計算機(jī),2004;21(1)

3 文冠果. 一種新型的128路多通道HDLC引擎設(shè)計.微電子學(xué)與計算機(jī),2004;21(9)