王龍1,楊承志1,肖衛(wèi)華1,楊斌斌2

(1. 空軍航空大學(xué) 信息對抗系,吉林 長春 130022;2. 沈陽航空航天大學(xué) 電子信息學(xué)院,遼寧 沈陽 110136)

摘要:設(shè)計了一種基于現(xiàn)場可編程門陣列(Field Programmable Gate Array,FPGA)和射頻級數(shù)模轉(zhuǎn)換器(Radio Frequency Digital to Analog Converter,RF DAC)的寬帶高斯噪聲源。該噪聲源將優(yōu)先編碼器原理運用到非均勻分段擬合映射曲線中,通過并行偽碼產(chǎn)生結(jié)構(gòu)生成均勻分布的偽碼序列,接著利用非均勻折線擬合的方法將偽碼序列映射為高斯分布的高速數(shù)字高斯噪聲,然后通過RF DAC輸出寬帶高斯噪聲。在Xilinx Virtex7 XC7VX485T和ADI AD9129搭建的驗證平臺上的測試結(jié)果表明,該噪聲源能輸出±4σ(σ為標準差)的高斯噪聲,噪聲帶寬可達1.2 GHz,并且只消耗FPGA 約0.3%的資源。

關(guān)鍵詞:高斯噪聲;優(yōu)先編碼;非均勻劃分;FPGA

0引言

高斯噪聲在自然界中普遍存在,對雷達偵察和通信偵察具有非常重要的影響。為了測試和驗證偵察接收設(shè)備在低信噪比條件下的性能,通常需要在測試信號中加入功率可控的高斯噪聲。參考文獻[1 3]采用串行移位寄存器產(chǎn)生偽碼序列,然后將偽碼序列通過曲線映射的方式轉(zhuǎn)換為數(shù)字高斯噪聲,再通過DAC輸出模擬高斯噪聲。受限于FPGA的工作時鐘,目前采用串行反饋移位寄存器的方式輸出的高斯噪聲帶寬最高為250 MHz[1]。

隨著寬帶雷達技術(shù)的發(fā)展,雷達信號的帶寬達到百兆量級[4],通過串行反饋移位寄存器的方式無法輸出如此高的高斯噪聲。因此本文對串行移位寄存器作8路并行化處理,在原有系統(tǒng)時鐘頻率不變的情況下,產(chǎn)生8倍于系統(tǒng)時鐘頻率的偽碼序列。然后通過均勻到高斯分布的映射關(guān)系,將偽碼映射為數(shù)字高斯噪聲,并通過RF DAC 直接產(chǎn)生寬帶高斯噪聲。與參考文獻[1]提出的寬帶高斯噪聲源設(shè)計方法相比,只消耗了0.3%的 FPGA資源,輸出的噪聲帶寬可達1.2 GHz。1并行偽碼產(chǎn)生結(jié)構(gòu)

m序列(偽隨機序列)是由線性移位寄存器加特定反饋后形成的,其結(jié)構(gòu)如圖1所示。圖中dn-i(i=1,2,3,…,r)為移位寄存器中每位寄存器的狀態(tài);ci(i=0,1,2,…,r)為第i位寄存器的反饋系數(shù),當ci等于0時,反饋線斷開,表示無反饋;ci=1時,反饋線連通,表示存在反饋;除c0以外的反饋線進行異或運算,得到的結(jié)果作為線性移位寄存器的輸入值。在此結(jié)構(gòu)中 c0=cr=1,c0不能為0,因為 c0=0意味著無反饋,就不能構(gòu)成周期性的序列,將轉(zhuǎn)變?yōu)殪o態(tài)移位寄存器。cr也不能為 0,即第 r位寄存器一定要參加反饋,否則r級的反饋移位寄存器將減化為r-1級的或更低的反饋移位寄存器。不同的反饋邏輯,即ci(i=0,1,2,…,r)取不同的值,將產(chǎn)生不同的移位寄存器。

在FPGA中實現(xiàn)這種結(jié)構(gòu),每個時鐘只能輸出一個PN碼,受限于當前FPGA的工藝水平,輸出噪聲頻率無法達到系統(tǒng)要求。為此需要對串行反饋移位寄存器作并行化處理,使之能在一個時鐘周期內(nèi)產(chǎn)生多個PN碼。以4路并行化為例,設(shè)串行反饋移位寄存器的反饋值依次為dn、dn+1、dn+2、dn+3…,則前4個反饋值可用下式表示:

移位寄存器中的值向右移動等效為異或單元向左移動一個位置。為了在一個時鐘內(nèi)得到dn、dn+1、dn+2、dn+3 4個值,可以設(shè)置4個異或單元且依次相鄰排列,在下一個時鐘移位寄存器的值向右移動4位即可。八階串行反饋移位寄存器(反饋系數(shù)用十六進制表示為(153)16)作4路并行化得到的并行偽碼產(chǎn)生結(jié)構(gòu)如圖2所示。

在每個時鐘的上升沿或下降沿,寄存器dr的值向前推入寄存器dr-4(r=4,5,...,11)中;4個異或單元輸出的值Ni(i=0,1,2,3)被送入高四位寄存器中;末四位寄存器的值作為四位并行偽碼同時輸出。

2高斯噪聲產(chǎn)生結(jié)構(gòu)

高斯白噪聲是一種均值為零、瞬時值服從正態(tài)分布、功率在一定帶寬內(nèi)恒定的隨機信號,它的方差反映了噪聲功率。在工程實踐中,為了獲得高斯白噪聲,人們通常采用某種方式將易于產(chǎn)生的噪聲映射為高斯白噪聲。映射往往采用噪聲概率相等的準則進行。均勻分布到高斯分布的映射關(guān)系可用下式表示:

式中,x為均勻隨機變量,y為高斯隨機變量。可見,均勻分布到高斯分布的映射關(guān)系即為高斯概率分布函數(shù)的反函數(shù)。y的絕對值越大,對應(yīng)點的斜率也越大。

使用并行偽碼結(jié)構(gòu)產(chǎn)生的偽碼序列服從均勻分布,而實際環(huán)境中的噪聲多為高斯分布,故產(chǎn)生的偽碼不能直接輸出,需要將均勻分布的偽碼序列轉(zhuǎn)換為高斯噪聲序列。轉(zhuǎn)換方法主要有函數(shù)變換法、中心極限法、查找表法 3 種[5]。其中,函數(shù)變換法和中心極限法需要使用復(fù)雜的數(shù)學(xué)運算,需要占用大量的FPGA內(nèi)部的DSP資源。查找表法需要建立均勻分布到高斯分布的映射關(guān)系,需要占用大量的FPGA內(nèi)部的存儲資源。

本文引入優(yōu)先編碼器的思想,將整個地址區(qū)間分成18段。對于最高位為0的數(shù)值(取值范圍為0~0.5)而言,從左向右第一個出現(xiàn)1的位置相同的所有數(shù)值屬于同一個區(qū)段;對于最高位為1的數(shù)值(取值范圍為0.5~1)而言,從左向右第一個出現(xiàn)0的位置相同的所有數(shù)值屬于一個區(qū)段。使用這種劃分方法的好處是除了兩端的兩個區(qū)段外,靠外的區(qū)段寬度是相鄰里側(cè)區(qū)段寬度的1/2,能夠滿足斜率小的地方使用較少的折線逼近,斜率大的地方使用較多的折線逼近的原則。優(yōu)先編碼器的輸入輸出關(guān)系如表1所示。其中Q_OUT為優(yōu)先編碼器的輸出值,代表所屬區(qū)段;A_IN為優(yōu)先編碼器的輸入值,取自并行偽碼序列的高9位,用二進制數(shù)表示,“x”代表任意(“0”或“1”)。

參考文獻[6]采取的尋址結(jié)構(gòu)組合邏輯層次過多,且需要用到加法器,不適用于高速電路的設(shè)計。在FPGA上的實現(xiàn)結(jié)果表明,使用輸入位寬為9 bit的優(yōu)先編碼器僅需要4片SLICE,占用資源不超過可配置邏輯塊(CLB)資源的萬分之一,工作時鐘可達400 MHz以上。

3基于FPGA的硬件實現(xiàn)

本文采用Xilinx Virtex-7 XC7VX485T芯片[7]實現(xiàn)數(shù)字高斯噪聲的產(chǎn)生,然后送入AD9129 DAC芯片[8]進行模數(shù)轉(zhuǎn)換。AD9129為14位的射頻級數(shù)模轉(zhuǎn)換器,可以直接合成射頻信號,DAC更新速率最高可達5.7 GS/s。系統(tǒng)的整體框圖如圖3所示。

并行偽碼產(chǎn)生結(jié)構(gòu)采用8路并行化處理,系統(tǒng)工作在300 MHz的時鐘頻率下,輸入到AD9129的數(shù)據(jù)率為2.4 GS/s(每秒2.4 G個采樣點)。為了能夠工作在如此之高的時鐘頻率下,高斯噪聲產(chǎn)生結(jié)構(gòu)中的乘加運算通過一個DSP核完成。該系統(tǒng)使用Verilog語言進行編程,可移植性強,在XC7VX485T上布局布線,能夠滿足時序要求。設(shè)計占用了112個SLICE(不到總資源的0.01%)和8個DSP核(約占總DSP核資源的0.26%),消耗的資源極少。

4仿真與測試結(jié)果

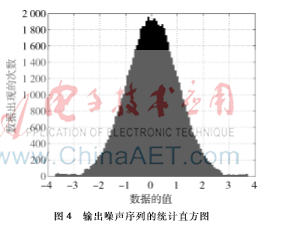

通過在Vivado 集成開發(fā)環(huán)境中進行功能仿真得到仿真數(shù)據(jù),然后取出65 536個數(shù)據(jù)值導(dǎo)入到MATLAB軟件進行統(tǒng)計,得到的統(tǒng)計分布直方圖如圖4所示。從圖中可以看出,系統(tǒng)仿真結(jié)果的統(tǒng)計分布在±4σ(σ為標準差)的范圍內(nèi)符合高斯分布。

5結(jié)論

高斯噪聲作為一種常見的噪聲,在工程實踐和科學(xué)實驗中被廣泛應(yīng)用。本文研究了一種并行偽碼產(chǎn)生結(jié)構(gòu),并首次將優(yōu)先編碼器原理應(yīng)用到均勻分布到高斯分布的非均勻折線擬合當中。仿真和測試結(jié)果表明,本文設(shè)計的基于FPGA的寬帶高斯噪聲源具有占用資源少、精度高、可移植性強等優(yōu)點,能夠輸出帶寬可達1.2 GHz的基帶噪聲。

參考文獻

[1] 吳帆, 李會方. 高斯噪聲源電路的設(shè)計與實現(xiàn)[J]. 電子設(shè)計工程,2012,20(16):161 163.

[2] 付俊, 李光燦. 一種高斯白噪聲信號發(fā)生器的設(shè)計與實現(xiàn)[J]. 計算機測量與工程, 2012,20(5):1436 1438.

[3] COEIHO R F. Design and implementation of an optical gaussian noise generator[J]. Optical Engineering,2009,48(8):771 777.

[4] 李海英, 楊汝良. 超寬帶雷達的發(fā)展、現(xiàn)狀及應(yīng)用[J]. 遙感技術(shù)與應(yīng)用, 2001(3):178 183.

[5] GUTIERREZ R, TORRES V, VALLS J. Hardware architecture of a gaussian noise generator based on the inversion method[J]. IEEE Transactions on Circuits and Systems, 2012,59(8): 501 505.

[6] 魏恒, 金松坡. 寬帶高斯噪聲源的設(shè)計與實現(xiàn)[J]. 中國集成電路, 2015,24(4):34 37.

[7] Xilinx Corporation. 7 series FPGAs overview[Z].(2014-03-18)[2016-03-20]. http://www.xilinx.com/support/documentation /data_sheets/ds180_7Series_Overview.pdf.

[8] ADI Corporation. AD9129 data sheet[Z]. (2013-08-11)[2016-03-20]. http://www.analog.com/media/en/technicaldocumentation/datasheets/AD9119_9129.pdf.