摘 要:介紹了用Multisim 仿真軟件測(cè)試門電路延遲時(shí)間的方法,提出了三種測(cè)試方案,即將奇數(shù)個(gè)門首尾相接構(gòu)成環(huán)形振蕩電路,用虛擬示波器測(cè)試所產(chǎn)生振蕩信號(hào)的周期,計(jì)算門的傳輸延遲時(shí)間;奇數(shù)個(gè)門首尾相接構(gòu)成環(huán)形振蕩電路,用虛擬示波器測(cè)試其中一個(gè)門的輸入信號(hào)、輸出信號(hào)波形及延遲時(shí)間;在一個(gè)門的輸入端加入矩形脈沖信號(hào),測(cè)試一個(gè)門的輸入信號(hào)、輸出信號(hào)波形及延遲時(shí)間。所述方法的創(chuàng)新點(diǎn)是,解決了受示波器上限頻率限制實(shí)際硬件測(cè)試效果不明顯的問題,并給出Multisim 軟件將門的初始輸出狀態(tài)設(shè)置為0 時(shí),使測(cè)試電路不能正常工作的解決方法。

0 引 言

門電路的傳輸延遲時(shí)間tpd 是表示工作速度的指標(biāo),實(shí)驗(yàn)室硬件測(cè)量的一般方法是,將N 個(gè)門( N為奇數(shù)) 首尾相接構(gòu)成振蕩周期為T = 2N tpd的環(huán)形振蕩電路,用示波器通過顯示的波形測(cè)量出振蕩周期T后,再計(jì)算出傳輸延遲時(shí)間tpd。

由于門的傳輸延遲時(shí)間tpd 很短,測(cè)量時(shí)受示波器上限頻率限制,測(cè)量效果較差,而用Mult isim 軟件仿真測(cè)試,可獲得理想的實(shí)驗(yàn)效果。

以下分析用Mult isim 2001版本,所得結(jié)論也適于其他版本。

1 Multisim仿真測(cè)試方案

1. 1 測(cè)試方案1

將奇數(shù)個(gè)門首尾相接構(gòu)成環(huán)形振蕩電路,用虛擬示波器測(cè)試所產(chǎn)生振蕩信號(hào)的周期,計(jì)算門的傳輸延遲時(shí)間。

設(shè)所用門的個(gè)數(shù)為N ,振蕩信號(hào)的周期為T ,則傳輸延遲時(shí)間為:

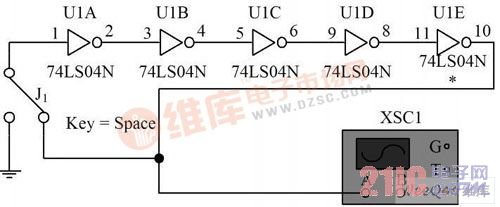

以反相器74LS04N 作為仿真實(shí)驗(yàn)器件,構(gòu)建仿真實(shí)驗(yàn)電路如圖1 所示。

圖1 測(cè)試方案1 的仿真實(shí)驗(yàn)電路

由于Mult isim 軟件將每個(gè)門的初始輸出狀態(tài)設(shè)置為0,直接用奇數(shù)個(gè)門首尾相接構(gòu)成環(huán)形振蕩電路進(jìn)行仿真時(shí),出現(xiàn) " nable to determine the simulatiONtimeSTep automatically" 的提示,無法同步仿真模擬。

解決的方法是在左邊第一個(gè)門U1A 的輸入端接入轉(zhuǎn)換開關(guān)J1 ,仿真時(shí)先將開關(guān)J1 置于接地狀態(tài),電路對(duì)輸入的0 信號(hào)進(jìn)行處理后便脫離設(shè)置的初始輸出狀態(tài),再將轉(zhuǎn)換開關(guān)J1 置于接輸出端構(gòu)成環(huán)形振蕩電路。

仿真前,可對(duì)74LS04N 的上升延遲時(shí)間及下降延遲時(shí)間進(jìn)行設(shè)置,如設(shè)置r ise delay= 10 ns,fall delay=10 ns。

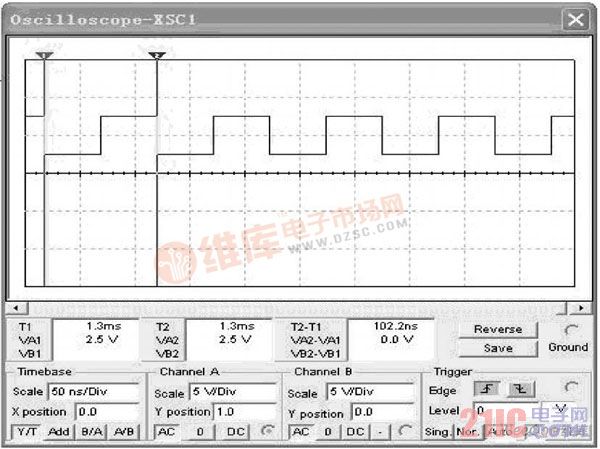

仿真時(shí)示波器顯示的波形及振蕩周期測(cè)試如圖2所示。

測(cè)試的振蕩周期T = 102. 2 ns,則傳輸延遲時(shí)間tpd= T/ ( 2N ) = 102. 2/ 10= 10. 22 ns,結(jié)果與設(shè)定值基本一致。

圖2 圖1 電路輸出波形及振蕩周期測(cè)試

1. 2 測(cè)試方案2

將奇數(shù)個(gè)門首尾相接構(gòu)成環(huán)形振蕩電路,用虛擬示波器測(cè)試其中一個(gè)門的輸入信號(hào)、輸出信號(hào)波形及延遲時(shí)間。

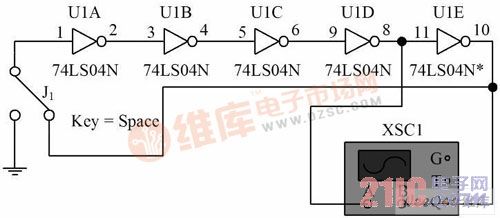

以反相器74LS04N 作為仿真實(shí)驗(yàn)器件,構(gòu)建仿真實(shí)驗(yàn)電路如圖3 所示。

圖3 測(cè)試方案2 的仿真實(shí)驗(yàn)電路

仿真前,可對(duì)74LS04N 的上升延遲時(shí)間及下降延遲時(shí)間進(jìn)行設(shè)置,如設(shè)置r ise delay= 10 ns,fall delay=10 ns。

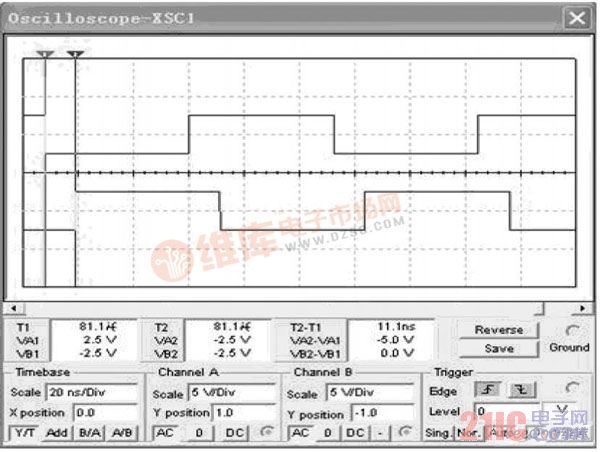

仿真時(shí)示波器顯示的輸入信號(hào)、輸出信號(hào)波形及延遲時(shí)間測(cè)試如圖4 所示。

圖4 圖3 電路輸入、輸出波形及延遲時(shí)間測(cè)試

測(cè)試的傳輸延遲時(shí)間tpd = 11. 1 ns,測(cè)量結(jié)果與設(shè)定值基本一致。

1. 3 測(cè)試方案3

在一個(gè)門的輸入端加入矩形脈沖信號(hào),測(cè)試一個(gè)門的輸入信號(hào)、輸出信號(hào)波形及延遲時(shí)間。外加信號(hào)的周期T = 2N tpd ,以保證門的工作頻率和前述其他測(cè)試方法相同。

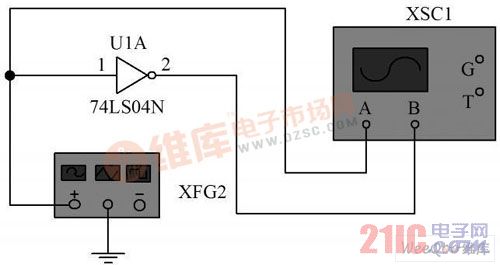

以反相器74LS04N 作為仿真實(shí)驗(yàn)器件,構(gòu)建仿真實(shí)驗(yàn)電路如圖5 所示,信號(hào)發(fā)生器輸出矩形脈沖的頻率選為10 MHz。

圖5 測(cè)試方案3 的仿真實(shí)驗(yàn)電路

仿真前,可對(duì)74LS04N 的上升延遲時(shí)間及下降延遲時(shí)間進(jìn)行設(shè)置,如設(shè)置rise delay= 10 ns,fall delay=10 ns。

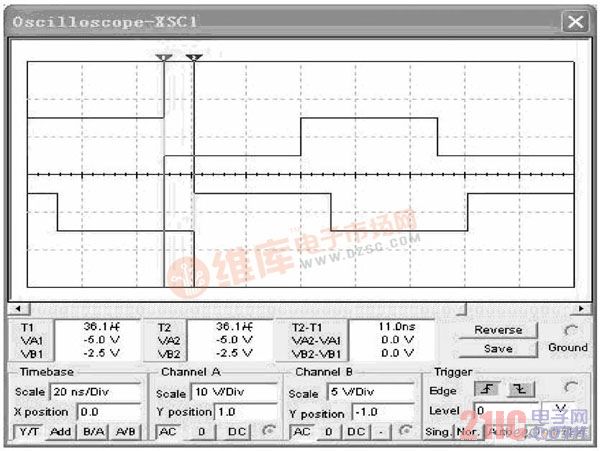

仿真時(shí)示波器顯示的輸入信號(hào)、輸出信號(hào)波形及延遲時(shí)間測(cè)試如圖6 所示。

圖6 圖5 電路輸入、輸出波形及延遲時(shí)間測(cè)試

測(cè)試的傳輸延遲時(shí)間tpd = 11. 0 ns,測(cè)量結(jié)果與設(shè)定值基本一致。

2 誤差分析

上述三種測(cè)試方案的測(cè)試結(jié)果表明存在誤差,原因是組成測(cè)試電路時(shí)門的輸入端、輸出端接入測(cè)試儀器,使門的輸入端、輸出端存在負(fù)載效應(yīng),從而使延遲時(shí)間略大于設(shè)定值。

在測(cè)試方案1 中,示波器接至一個(gè)門的輸出端,僅對(duì)門的輸出端產(chǎn)生影響;測(cè)試方案2、3 中,示波器接至一個(gè)門的輸入端、輸出端,對(duì)門的輸入端、輸出端均產(chǎn)生影響。所以測(cè)試方案1 測(cè)試的延遲時(shí)間小于測(cè)試方案2、3;測(cè)試方案2、3 測(cè)試的延遲時(shí)間基本相同。

3 結(jié) 語(yǔ)

Multisim 軟件仿真具有豐富的仿真分析能力,但也存在一些問題及不足,使用時(shí)必須認(rèn)真分析思考軟件的設(shè)置條件,改進(jìn)仿真實(shí)驗(yàn)方法,才能達(dá)到預(yù)期的實(shí)驗(yàn)效果。

所述方法具有實(shí)際應(yīng)用意義,這些方法亦可用于其他功能邏輯門傳輸時(shí)間的仿真測(cè)試。