摘要: 給出了一種基于FPGA的數(shù)字濾波器的設(shè)計(jì)方法。該方法先通過MATLAB設(shè)計(jì)出一個具有具體指標(biāo)的FIR濾波器, 再對濾波器系數(shù)進(jìn)行處理, 使之便于在FPGA中實(shí)現(xiàn), 然后采用基于分布式算法和CSD編碼的濾波器結(jié)構(gòu)進(jìn)行設(shè)計(jì), 從而避免了乘法運(yùn)算, 節(jié)約了硬件資源,其流水線的設(shè)計(jì)方式也提高了運(yùn)行速度。Matlab和Modelsim仿真表明, 該設(shè)計(jì)功能正確, 能實(shí)現(xiàn)快速濾波。

0 引言

數(shù)字濾波器在語音與圖像處理、模式識別、雷達(dá)信號處理、頻譜分析等應(yīng)用中都具有重要作用。它能避免模擬濾波器所無法克服的溫漂和噪聲等問題, 同時比模擬濾波器精度高、穩(wěn)定性好、體積小、更加靈活, 因而得到廣泛應(yīng)用。在聲波測井中, 通常需要對信號進(jìn)行精確的濾波,并且對濾波器具有嚴(yán)格的實(shí)時性要求。本文利用輔助Matlab設(shè)計(jì)工具, 設(shè)計(jì)了一種基于FPGA且可滿足測井需求的高階快速數(shù)字濾波器。

1 線性相位FIR濾波器結(jié)構(gòu)

數(shù)字濾波器的種類很多, 分類的方法也不盡相同。從數(shù)字濾波器的單位沖擊響應(yīng)來看, 數(shù)字濾波器分為有限沖激響應(yīng)數(shù)字濾波器(FIR) 和無限沖激響應(yīng)數(shù)字濾波器(IIR)。相對于IIR濾波器,F(xiàn)IR濾波器可以進(jìn)行準(zhǔn)確的線性相位設(shè)計(jì), 而且其結(jié)構(gòu)具有穩(wěn)定的量化濾波器系數(shù)。針對于聲波測井處理具有線性相位要求的聲波信號, FIR濾波器是首選。

在時域中, FIR濾波器的輸入輸出過程是一個輸入信號與單位脈沖響應(yīng)進(jìn)行線性卷積的過程, 其差分方程表達(dá)式為:

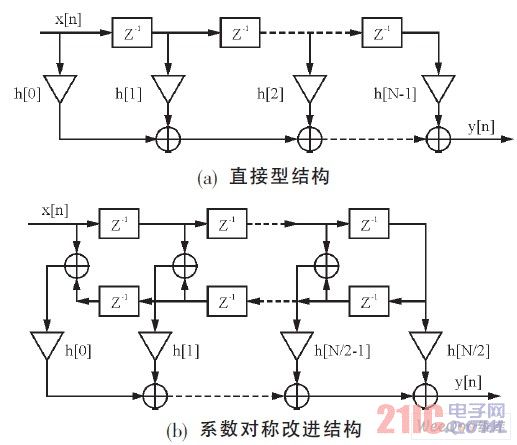

其中, y (n) 為濾波輸出, x (n) 為采樣數(shù)據(jù), h (n) 為濾波器抽頭系數(shù)。其結(jié)構(gòu)如圖1 (a)所示, 圖中, N-1階FIR濾波器要用N個系數(shù)描述, 通常, 需要N個乘法器和N-1個兩輸入加法器才能實(shí)現(xiàn)。不難發(fā)現(xiàn), 乘法器的系數(shù)正好是傳輸函數(shù)的系數(shù), 因此, 該結(jié)構(gòu)且稱為直接型結(jié)構(gòu)。

對于系數(shù)對稱的FIR線性相位濾波器, 可將式(1) 寫成如下形式:

系數(shù)對稱的改進(jìn)型FIR濾波器的結(jié)構(gòu)如圖1(b) 所示。該結(jié)構(gòu)把系數(shù)對稱(相同或相反) 的抽頭合并之后再作乘法, 這樣可使乘法器數(shù)量降為原有的一半, 但也增加了額外的加法器。

圖1 FIR濾波器結(jié)構(gòu)

2 設(shè)計(jì)方法與指標(biāo)

FDATool是Matlab信號處理工具箱里專用的濾波器設(shè)計(jì)分析工具, 該工具的主要作用是按照設(shè)計(jì)指標(biāo)提取濾波器系數(shù)。用FDATool設(shè)計(jì)數(shù)字濾波器的關(guān)鍵在于濾波器類型、窗函數(shù)、濾波器階數(shù)、截止頻率等參數(shù)的選擇。其中窗函數(shù)用于決定阻帶衰減和過渡帶帶寬, 常用的窗函數(shù)有矩形窗、漢寧窗、海明窗和布萊克曼窗。矩形窗和漢寧窗阻帶衰減較小, 而布萊克曼窗過渡帶較大, 相對來說, 海明窗更符合設(shè)計(jì)要求, 它的最小阻帶可以達(dá)到54.5dB, 歸一化過渡帶帶寬為3.11π/M (濾波器階數(shù)N=2M+1)。針對聲波測井信號, 設(shè)計(jì)時應(yīng)進(jìn)行表1所列的參數(shù)設(shè)置。

表1 濾波器參數(shù)選擇

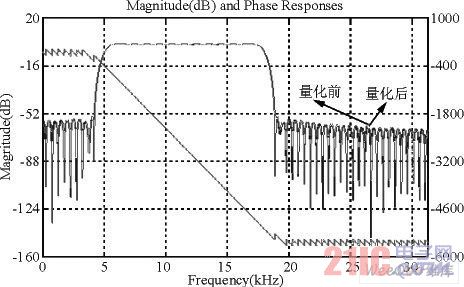

圖2所示是該濾波器的幅頻和相頻響應(yīng)曲線,該曲線在通帶內(nèi)保持線性相位, 阻帶衰減大于52dB, 過渡帶帶寬為1.65kHz。抽頭系數(shù)可以在工具箱中量化為定點(diǎn)整型數(shù)據(jù), 以便在FPGA實(shí)現(xiàn)階數(shù)為127的濾波器, 該濾波器一共有128個系數(shù)。對于階數(shù)較大的濾波器來說, 其量化對阻帶衰減和過渡帶的影響極小。

圖2 濾波器幅頻和相頻響應(yīng)特性曲線

3 基于FPGA的濾波器設(shè)計(jì)

用FPGA設(shè)計(jì)FIR濾波器的關(guān)鍵在于如何處理占用大量資源的乘法單元。分布式算法(DA) 的提出可將乘法運(yùn)算轉(zhuǎn)換為移位相加運(yùn)算, 從而節(jié)約硬件資源。若令Hk為濾波器系數(shù), xk (n) 為n時刻的采樣輸入, y (n) 為n時刻的系統(tǒng)響應(yīng), 那么, 式(1) 就可以等效于下式:

把數(shù)據(jù)的源數(shù)據(jù)格式規(guī)定為2的補(bǔ)碼形式,則有:

式中, xkb (n) 為二進(jìn)制數(shù), 可取值為0或1;xk0 (n) 為符號位, 為1表示數(shù)據(jù)為負(fù), 為0表示數(shù)據(jù)為正。因此, 將(4) 式代入(3) 式可得:

式(5) 的形式被稱為分布式算法。可以看出, 方括號內(nèi)表示輸入變量的一個數(shù)據(jù)位和所有濾波器抽頭系數(shù)H0~HN的每一位進(jìn)行“與” 運(yùn)算并求和。而指數(shù)部分則說明了求和結(jié)果的位權(quán),整數(shù)乘以2b就是左移b位, 對此可以通過硬件連線來實(shí)現(xiàn), 而不占用邏輯資源。這樣就可以通過建立查找表來實(shí)現(xiàn)方括號中的運(yùn)算。查找表可用所有輸入變量的同一位進(jìn)行尋址, 這便是基于查找表的分布式算法(LUT-DA)。

LUT-DA算法的查找表大小為B·2N bits, 其中B為輸入數(shù)據(jù)的位寬, N為濾波器階數(shù)。隨著濾波器階數(shù)的增加, 查找表大小是2的指數(shù)增長;當(dāng)B為16, N為128時, 查找表的大小已經(jīng)不可想象。故將查找表分割成多個子表, 可以有效解決這個問題, 這也衍生了比較有效的串行LUT-DA算法和并行LUT-DA算法, 但兩者都有不足的地方。對于串行結(jié)構(gòu), 要完成一次輸出, 需要大于B的多個時鐘周期; 而對于并行結(jié)構(gòu), 雖然可以一個時鐘周期完成一次輸出, 但需要復(fù)制B個完全相同的LUT表, 而這會增加硬件資源的開銷。

為了兼顧速度和面積, 本文設(shè)計(jì)了一種基于DA算法原理的CSD-DA算法。首先, 將系數(shù)式(3) 中的固定系數(shù)Hk按2的冪展開后可得:

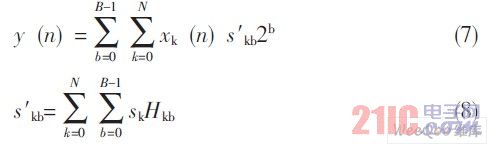

然后交換移位和累加順序, 則可得到下式:

式中, Hkb是值為0或者1的權(quán)重系數(shù); Sk為1表示Hk為正, 為-1則表示Hk為負(fù); s′kb的值可取0、-1或者1。經(jīng)過(4) 式的展開, 乘法運(yùn)算將被全部轉(zhuǎn)換為移位相加運(yùn)算, 其中權(quán)重為0的部分可以剔除而不進(jìn)行計(jì)算。為了更進(jìn)一步減少Hkb陣列中的非零項(xiàng), 可將Hk編碼為CSD碼, 即從二進(jìn)制編碼最低的有效位開始, 用10···01來取代所有大于或等于2的1序列, 1表示該位為-1。由于CSD表示其中任何相鄰的兩位中, 必包含一個0,故1的數(shù)量最多不會超過N/2。平均來說, CSD表示其中大約有1/3的位為非零值, 這比補(bǔ)碼表示少大約1/3的非零位。假設(shè)h= (15) 10= (01111) 2,y=hx=x (23+22+21+20), 而如果將(15) 10編碼為(10001) csd, 那么, Y=x· (24-20)。采用二進(jìn)制編碼方式, 將用到3個加法器, 而用CSD編碼, 則只用了一個減法器, 可見, CSD編碼可以從本質(zhì)上減少硬件資源開銷。經(jīng)過CSD編碼優(yōu)化后, s′kb非零值的個數(shù)會遠(yuǎn)小于Hkb的非零值個數(shù)。

對于線性相位系數(shù)對稱的FIR濾波器, 為了減少乘法單元, 可選擇圖3所示的結(jié)構(gòu)。由于所有的乘法運(yùn)算都可轉(zhuǎn)化為大量的加法和減法運(yùn)算, 故將導(dǎo)致關(guān)鍵路徑過長, 系統(tǒng)運(yùn)行速度較低。而加入流水線寄存器, 則可減少關(guān)鍵路徑長度, 從而提高系統(tǒng)的最大工作頻率。在b為定值時, s′kb的非零值個數(shù)存在不確定性, 故在進(jìn)行流水線設(shè)計(jì)的時候, 可根據(jù)s′kb進(jìn)行靈活的分割, 路徑越長, 加入的流水線寄存器越多。為了防止中間結(jié)果的溢出, 寄存器的位寬要有冗余設(shè)計(jì), 對于有符號的數(shù), 其位寬取值為M+log2N-1, M為上級累加器位寬, N為濾波器階數(shù)。

圖3 流水線CSD-DA算法局部結(jié)構(gòu)

從圖3的流水優(yōu)化CSD-DA算法結(jié)構(gòu)可見, 所有乘法都會轉(zhuǎn)換為移位加法, 移位運(yùn)算可用硬件連線實(shí)現(xiàn), 整個結(jié)構(gòu)經(jīng)過了合理的流水線分割。

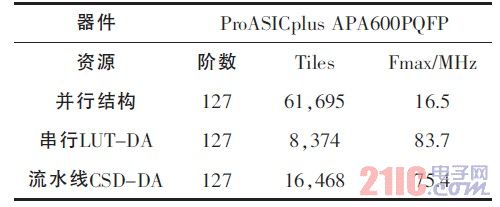

表2所列是不同結(jié)構(gòu)濾波器的綜合結(jié)果。其中并行結(jié)構(gòu)是最差的一種結(jié)構(gòu), 它占用資源多、速度慢; 串行LUT-DA結(jié)構(gòu), 雖然占用資源少,最大工作頻率高, 但畢竟是串行結(jié)構(gòu), 不能在一個時鐘節(jié)拍完成對一個采樣點(diǎn)的濾波運(yùn)算; 而流水線CSD-DA結(jié)構(gòu)則無論在速度, 還是面積上,都具有比較明顯的優(yōu)勢。如果工作時鐘為75MHz, 那么, 一個時鐘節(jié)拍便可以完成一次輸出, 處理330個采樣點(diǎn)的單通道信號僅需4.4μs,可以滿足測井實(shí)時性要求。

表2 濾波器的綜合結(jié)果

4 結(jié)果分析

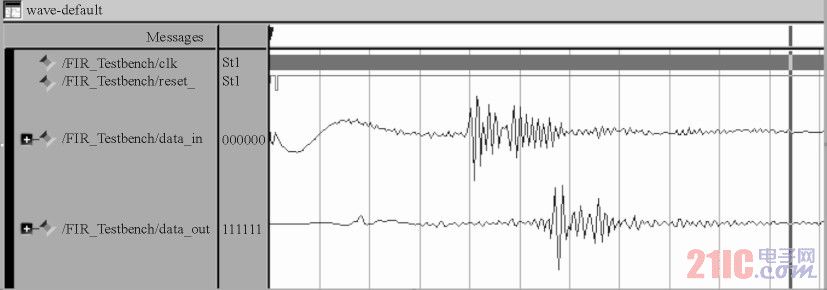

為了驗(yàn)證濾波器的功能是否正確, 可對本設(shè)計(jì)在Modelsim中進(jìn)行仿真。若原始波形為帶噪聲的聲波信號, 那么, 其濾波的結(jié)果如圖4所示。

圖4 濾波器在Modelsim中的仿真結(jié)果

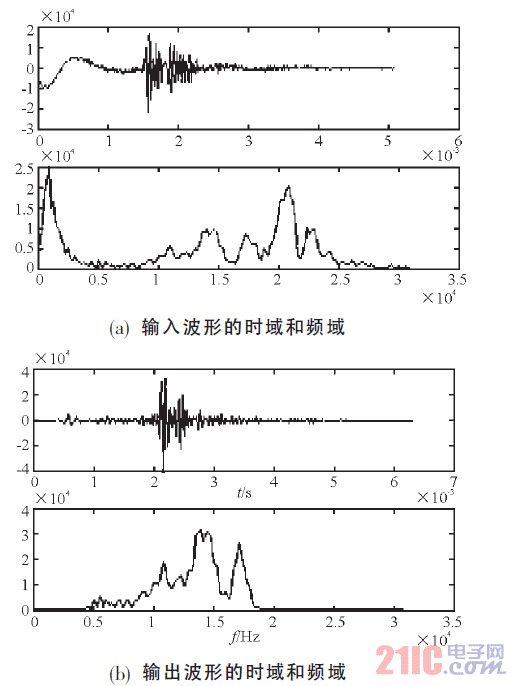

圖5所示是濾波器在Matlab中的仿真結(jié)果, 可以看出, Modelsim和Matlab的仿真結(jié)果一致。在頻域上, 對比圖5 (a) 和圖5 (b) 可以看到, 其濾波后的波形只保留了5kHz~18kHz的頻譜部分, 這說明流水線CSD-DA結(jié)構(gòu)的數(shù)字濾波器設(shè)計(jì)正確。

圖5 濾波器在Matlab中的仿真結(jié)果

5 結(jié)束語

本文詳細(xì)講述了通過Matlab工具設(shè)計(jì)FIR線性相位濾波器的方法, 并針對聲波信號設(shè)計(jì)了優(yōu)于傳統(tǒng)結(jié)構(gòu)的流水線CSD-DA結(jié)構(gòu), 該結(jié)構(gòu)具有較明顯的速度和面積優(yōu)勢。文中也通過仿真實(shí)驗(yàn)證實(shí)了設(shè)計(jì)的合理性和正確性。但值得指出的是, 該結(jié)構(gòu)只適合固定濾波器系數(shù)的場合, 而如果要進(jìn)行修改, 則需要重新對系數(shù)進(jìn)行CSD編碼和流水線分割。