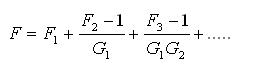

低噪聲放大器(LNA)正如它的名字含義那樣,通過減小系統(tǒng)噪聲系數(shù)來提高接收機(jī)的靈敏度。Friss公式表明,接收機(jī)第1級(jí)電路的噪聲系數(shù)(F1)占主導(dǎo)作用,后級(jí)電路(即F2,F3...)的影響則逐漸減小。

(公式2)

(公式2)其中,Gn代表接收鏈路中第n級(jí)電路的增益。

發(fā)射機(jī)和接收機(jī)通過選頻雙工器,或者頻域雙工或時(shí)域雙工(TDD)的射頻開關(guān),共用一根天線。另外,在LNA之前可能會(huì)插入一個(gè)帶通濾波器,用于防止被強(qiáng)大的帶外干擾所阻塞或減敏。遺憾的是,雙工器和濾波器都是無源器件,都存在一定的射頻損耗。因?yàn)檫@些損耗發(fā)生在LNA之前,所以它們對(duì)總的靈敏度有很大的影響。因此,如果LNA噪聲系數(shù)具有一定的設(shè)計(jì)余量,那么雙工器和濾波器的損耗指標(biāo)也許就不那么重要了。

除了低噪聲外,其它重要的性能參數(shù)還包括增益和線性度。無線基礎(chǔ)設(shè)施通常包含一個(gè)塔頂安裝的LNA,這個(gè)LNA需要通過一根長電纜連接到地面的無線電小屋,因此,為了克服電纜損耗,最好具有較高的增益。線性度之所以重要,是因?yàn)樵谒車纳漕l頻譜非常擁擠,因?yàn)橐c其它無線服務(wù)共享基站。

本文的目的是要表明,從性能和成本角度考慮,單級(jí)GaAs PHEMT微波單片集成電路(MMIC)是實(shí)現(xiàn)無線基礎(chǔ)設(shè)施使用的3.5GHz LNA的最佳解決方案。

MMIC器件

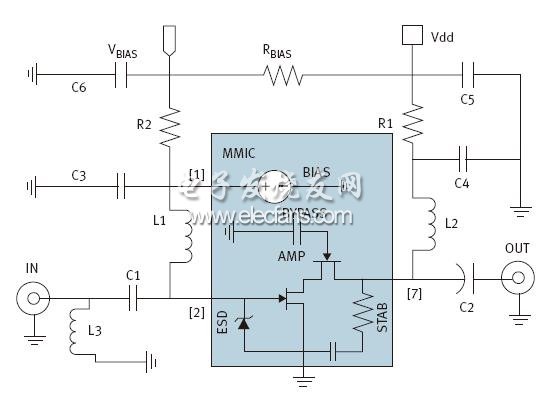

圖1顯示了安華高公司MGA-635P8 MMIC的內(nèi)部和外部電路。內(nèi)部電路由制造在同一裸片上的一個(gè)共源共柵放大器(AMP)和一個(gè)有源偏置調(diào)節(jié)器(BIAS)組成。共源共柵拓?fù)浣Y(jié)構(gòu)主要是根據(jù)3.5GHz時(shí)大于15dB增益這個(gè)要求設(shè)計(jì)的,因?yàn)橐郧安捎孟嗤腉aAs增強(qiáng)型偽形態(tài)高電子遷移率晶體管(ePHEMT)工藝的共源(CS)設(shè)計(jì)只能達(dá)到約13dB的增益。雖然兩級(jí)共源電路可以通過級(jí)聯(lián)達(dá)到期望的增益,但共源共柵拓?fù)浣Y(jié)構(gòu)具有電流再使用的額外優(yōu)勢,即同一電流流經(jīng)兩級(jí)電路。

圖1:(a)LNA電路和(b)PCB和元件。

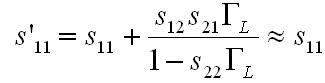

在一些接收機(jī)實(shí)現(xiàn)中,當(dāng)輸入信號(hào)很強(qiáng)時(shí),LNA之后的增益級(jí)電路將被射頻開關(guān)旁路掉。開關(guān)切換引起的LNA負(fù)載匹配(ΓL)的變化將被傳回到輸入匹配(S11),因?yàn)樵撈骷榉菃蜗蛐?即S12≠0)。天線和輸入濾波器都是對(duì)端接非常敏感的器件,它們可能因S11變化而失諧。當(dāng)S12接近于零時(shí),S11對(duì)負(fù)載變化的敏感度會(huì)降低,(公式21) (當(dāng)s12→0)。

共源共柵拓?fù)涞姆聪蚋綦x是共源拓?fù)涞?/200至1/2000,這是選擇共源共柵拓?fù)涞牡诙€(gè)原因。由于直接轉(zhuǎn)換接收器對(duì)本地振蕩器的自混頻較靈敏,所以此器件同樣能從較好的隔離中受益。

共源共柵拓?fù)渲械拿總€(gè)FET都只能得到總供電電壓Vdd的一半。因此,在低電壓工作時(shí),共源共柵拓?fù)涞脑鲆婧途€性度可能要比共源拓?fù)涞汀PHEMT是實(shí)現(xiàn)共源共柵的理想選擇,因?yàn)槠湓鲆婧途€性度在Vds≥2V時(shí)非常穩(wěn)定。共源共柵輸出要與串聯(lián)RC網(wǎng)絡(luò)級(jí)聯(lián)起來,以便提高工作頻率以上的穩(wěn)定性。

MMIC采用了成熟且極具成本效益的0.25μm工藝制造,其增益帶寬乘積fT超過30GHz。除了盡量減少達(dá)到目標(biāo)增益所要求的電路級(jí)數(shù)外,較高的fT也有利于實(shí)現(xiàn)低噪聲系數(shù)。另外,通過加倍金屬厚度,可以最大限度地減小電路互連中產(chǎn)生的Johnson噪聲。這種0.64x0.64mm芯片安裝在8引腳的方形扁平無引腳(QFN,2x2x0.75mm)塑料封裝內(nèi)。

內(nèi)部偏置調(diào)節(jié)器允許通過RBIAS或外部施加的偏置電壓VBIAS控制LNA靜態(tài)電流(Ids)。調(diào)節(jié)器的低電流驅(qū)動(dòng)要求(IBIAS≤1mA)與大多數(shù)CMOS器件兼容,并且可以在時(shí)域雙工(TDD)應(yīng)用中使用5V邏輯切換LNA(斷開LNA可以防止發(fā)射期間由于柵極電流增加引起的金屬遷移)。器件閾值電壓(VT)、前向跨導(dǎo)(gm)和RDS(導(dǎo)通)會(huì)隨溫度變化以及晶圓不同而改變,進(jìn)而逆向改變工作點(diǎn)。在此設(shè)計(jì)中,在一顆芯片上集成偏置調(diào)節(jié)器和LNA有助于穩(wěn)定工作點(diǎn),因?yàn)閂BIAS和VGS電壓可以通過相互"鏡像"來補(bǔ)償熱漂移和不同晶圓批次之間的gm變化。

片外電路

匹配、射頻去耦和偏置功能總共需要12個(gè)片外元件,因?yàn)檫@些功能無法集成在芯片上(表1)。

表1:LNA評(píng)估電路的物料清單。

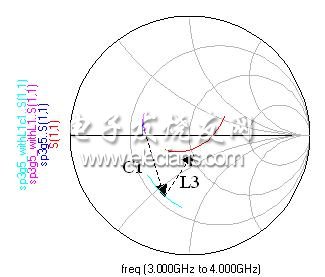

C3、C6和L1提供柵極偏置的射頻去耦。C1-L3 L網(wǎng)絡(luò)將器件S11轉(zhuǎn)換為Z0,如圖2所示。輸入的中頻帶有意偏移完美的匹配狀態(tài),以便能夠"環(huán)繞"Smith圖中心以獲得更寬帶寬。高通拓?fù)浣Y(jié)構(gòu)可以復(fù)現(xiàn)低頻(LF)工作。

圖2:仿真得到的輸入匹配軌跡。

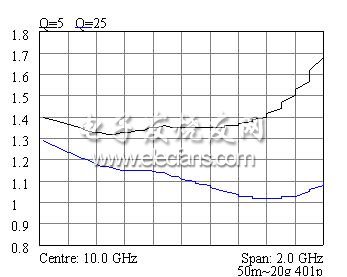

器件ZOUT在f0時(shí)已經(jīng)接近50Ω,因此不需要進(jìn)一步匹配。C2和L2則分別用作隔直器和扼流圈。它們還隱含有高通特性,可進(jìn)一步增強(qiáng)LF穩(wěn)定性。在第一次設(shè)計(jì)迭代過程中,L2用的是一個(gè)0402繞線電感,這將在最低頻點(diǎn)(11GHz)形成0.94的Rollett穩(wěn)定系數(shù)(k)。當(dāng)L2在后來的原型中用多層0402電感代替時(shí),這個(gè)最低系數(shù)k在10GHz可輕松的提高到1.2(見圖3)。我們認(rèn)為這個(gè)多層電感在10GHz點(diǎn)具有更低的Q(品質(zhì)因數(shù))是穩(wěn)定性提高的根本原因。圖3中的仿真結(jié)果支持這一推測,即通過選擇更低Q值的L2可以提高穩(wěn)定系數(shù)k。

圖3:仿真得到的k與頻率的關(guān)系:L2降低Q值的函數(shù)。10GHz時(shí),將QUL從25降低至5可以提高穩(wěn)定系數(shù)k。

為L1-L3選擇的芯片電感應(yīng)具有比f0更高的自諧振頻率(SRF)。如此謹(jǐn)慎的做法可以確保3.5GHz處電感的運(yùn)轉(zhuǎn)狀態(tài)具有可預(yù)測性。

由于輸出和輸入引腳的偏置電壓來自同一電源(Vdd),因此,一部分輸出信號(hào)可能通過傳導(dǎo)的方式沿著公共的直流通路返回到輸入端。輸出和輸入信號(hào)的相量疊加可能形成增益紋波,甚至低于f0的振蕩。為了避免電源上發(fā)生意外的輸出至輸入反饋,需要使用去耦電容C3-C6將交流信號(hào)旁路到地。小電容和大電容的組合使用可以在更寬的頻譜上實(shí)現(xiàn)有害信號(hào)的抑制。

盡管輸入匹配電路具有高通響應(yīng)特性,但其有限的帶外抑制允許一定程度的低頻信號(hào)滲入。由于FET柵極在低頻時(shí)接近開路,所以信號(hào)將被反射回源極。由于入射和反射的輸入信號(hào)在頻率范圍內(nèi)存在相位變化,因此它們的矢量疊加將在輸入反射系數(shù)(ΓIN)上產(chǎn)生紋波,如圖4所示。在紋波尖峰超過單位1的頻率點(diǎn),放大器可能會(huì)變得不穩(wěn)定。由此可以知道,穩(wěn)定性判據(jù)k在受影響的頻率處也將小于1。由R2和C6組成的解決方案給反射信號(hào)提供了電阻端接,因此可以降低f0以下的紋波。

圖4:在增加R2-C6低頻端接網(wǎng)絡(luò)之前和之后測得的輸入反射系數(shù)。

為了在時(shí)域雙工(TDD)模式下切換LNA,RBIAS的Vdd端可以被重新連接到0/5V控制邏輯。切換時(shí)間受RBIAS和C6的大時(shí)間常數(shù)(τ=RBIAS·C6)限制。為了實(shí)現(xiàn)更快的導(dǎo)通,C6可以減小到與C3相同的值。在此評(píng)估板上,C6值為10pF時(shí),測得的導(dǎo)通時(shí)間約為0.6μs。

面積為21.5x18mm2的PCB在10mil的Rogers RO4350材料上使用了帶共面地的微帶線。這種價(jià)格適中的基板具有適度的射頻性能,并且與FR4制造工藝兼容。由于RO4350 PCB本身較薄而太柔軟,因此需要在其地平面?zhèn)日迟N一塊1.2mm厚的FR4附加層進(jìn)行加固,使PCB疊層足夠厚(1.45mm),以適合使用標(biāo)準(zhǔn)邊緣安裝(edge-launch)射頻連接器的滑合座。

MMIC底部的中央板和引腳4必須使用盡可能短的路線連接到射頻地,以盡量減小有害的寄生效應(yīng)。如果在MMIC和PCB地平面之間存在明顯的寄生電感,可能出現(xiàn)包括增益下降和頻率大于10GHz的振蕩等問題。在MMIC下方直接放置4個(gè)過孔就可以實(shí)現(xiàn)到底部地平面的連接。根據(jù)良好的射頻使用習(xí)慣,所有未用的MMIC引腳也都連接到地。

元件和PCB建模

為了盡量減少甚至避免實(shí)際的調(diào)整,在建立原型之前需要通過仿真設(shè)計(jì)片外電路。預(yù)測潛在問題(如帶外不穩(wěn)定性)還有助于避免將錯(cuò)誤的PCB版圖提交給制造部門。

為了便于匹配電路的設(shè)計(jì),需要通過測量處于典型偏置條件下的定制設(shè)計(jì)夾具上的物理器件獲得MMIC散射參數(shù)(s2p)。這種特征化夾具使用與原型LNA相同的PCB材料(10mil RO4350)。在利用穿透反射線(RTL)技術(shù)從原始數(shù)據(jù)中除去夾具效應(yīng)后,生成的s2p數(shù)據(jù)就反映了器件及其PCB封裝外形(即器件下方的安裝焊盤和基板)。然后把s2p文件導(dǎo)入安杰倫科技的ADS2006A軟件用于電路仿真。

在第一次仿真迭代過程中,可以采用簡化的等效電路對(duì)片外元件進(jìn)行建模。雖然制造商提供的s2p文件可以用于構(gòu)建這些RLC無源器件的模型,但它們?nèi)狈﹄S時(shí)修改元件值的便利性,可能減慢仿真器中的調(diào)諧過程。另外,電容制造商提供的s2p數(shù)據(jù)在有效性方面有嚴(yán)格的限制,因?yàn)樗刂酒L軸只有一個(gè)參考面,所以其只對(duì)于并聯(lián)電容才是準(zhǔn)確的。因?yàn)榇?lián)在射頻通路中的電容是真正的雙端口器件,需要兩個(gè)參考平面,即一個(gè)端子需要一個(gè)參考平面,所以這種數(shù)據(jù)無法準(zhǔn)確地表述這種電容。

通過直觀地選擇最重要的寄生元件,可以創(chuàng)建簡化的RLC元件等效電路,正如Rhea描述的那樣。由2個(gè)或3個(gè)元件的等效電路組成的這些元件模型只能解決基頻諧振,而現(xiàn)實(shí)世界的無源元件具有多種更高的諧振頻率。更精確的建模技術(shù)(如基于測量的模型)可以覆蓋多種更高的諧振頻率,但是要求額外的測量和計(jì)算機(jī)優(yōu)化來開發(fā)。為了設(shè)計(jì)LNA阻抗匹配電路,可以容忍簡單模型的頻率限制,因?yàn)槲覀冎饕菍?duì)f0周圍的頻率范圍感興趣。值得注意的是,制造商提供的許多s2p文件也是頻率受限的。

電感模型使用了最接近f0的頻率點(diǎn)(通常是1.7GHz或1.8GHz,具體取決于制造商,這在數(shù)據(jù)手冊(cè)中可以找到)規(guī)定的QUL典型值,然后可以使用Q∝√f關(guān)系外推到3.5GHz以上。電感的寄生電容(Cpst)從公布的SRF典型值計(jì)算得到,但需要增加額外的0.1pF,以代表與PCB焊盤有關(guān)的寄生電容。電容模型中的寄生電感(Lpst)遵循供應(yīng)商軟件中提供的值。

結(jié)果與討論

原型在以下條件下進(jìn)行評(píng)估:5V供電電壓,3.5GHz中心頻率和室溫。通過使用3.3kΩ的RBIAS值將器件電流Idd設(shè)置為60±5mA。

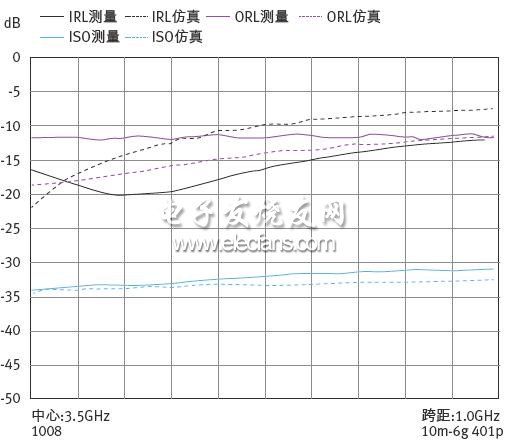

最首要的設(shè)計(jì)目標(biāo)是同時(shí)達(dá)到良好的反射損耗(IRL<-15dB)和低噪聲水平(F<1dB)。這個(gè)要求最初來自雙工器或?yàn)V波器對(duì)端接敏感的基站(BTS)市場部分。較老的基站實(shí)現(xiàn)通常依賴位于平衡LNA輸入端的隔離器或積分耦合器同時(shí)實(shí)現(xiàn)低反射損耗和噪聲系數(shù)。但是,鑒于成本和空間的考慮,較新的實(shí)現(xiàn)設(shè)法取消了隔離器或積分耦合器。在圖5中,在3.5GHz處測得的性能是:IRL=-16dB,ORL=-12dB和ISO=-32dB。在約300MHz處產(chǎn)生的最小反射損耗低于目標(biāo)要求,然而并不需要重新調(diào)諧輸入匹配電路,因?yàn)槠渌笠呀?jīng)滿足。除此之外,還需要有比普通E12更高粒度的LC值,將中頻帶搬移到準(zhǔn)確的3.5GHz。測量得到的ISO要比同樣尺寸的單個(gè)EPHEMT好13dB左右。

圖5:測量和仿真得到的輸入反射損耗(IRL)、輸出反射損耗(ORL)和反向隔離(ISO)與頻率的關(guān)系。

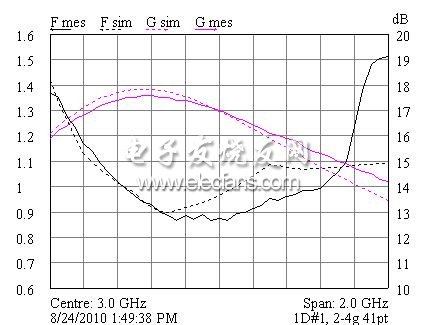

在3.5GHz測得的噪聲系數(shù)稍低于1dB。由于前述的輸入匹配誤差,最小值被偏移到3GHz。最小的F要比單個(gè)PHEMT參考約低0.1dB。最大增益17.6dB發(fā)生在2.6GHz,但保持了15.6dB的足夠增益。

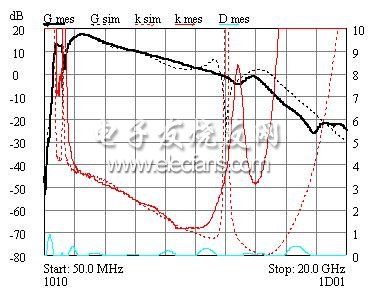

對(duì)最終的LNA潛在的不穩(wěn)定性進(jìn)行了徹底研究,結(jié)果見圖6所示的圖形。在通帶之外,增益單調(diào)地下降,其較小的拐點(diǎn)位于14GHz和18GHz。造成峰值的可能原因是元件諧振和輸入輸出耦合,但當(dāng)這些峰值低于單位增益時(shí),在尺寸不合適的金屬外殼中空腔共振風(fēng)險(xiǎn)很小。從圖7還可以看出Rollett穩(wěn)定系數(shù)(公式31),穩(wěn)定性指標(biāo)D=|S11S22-S12S21|。這兩個(gè)指標(biāo)都是根據(jù)測量到的板級(jí)s2p計(jì)算出來的。由于測量表明在整個(gè)評(píng)估的頻率范圍內(nèi)k>1和D<1,因此,能夠保證帶正實(shí)數(shù)部分的任何端接都具有絕對(duì)穩(wěn)定性。

圖6:測量和仿真得到的噪聲系數(shù)(F)和增益(G)與頻率的關(guān)系。

圖7:測量和仿真得到的增益(G)、Rollett穩(wěn)定系數(shù)(k)和穩(wěn)定性指標(biāo)(D)與頻率的關(guān)系。

由于接收機(jī)元件具有非線性,相鄰?fù)ǖ佬盘?hào)可能形成三階互調(diào)失真(IMD3)。由2f1-f2或2f2-f1關(guān)系確定的非線性不可能被濾除,因?yàn)樗鼈兎浅=咏杏眯盘?hào)。線性度的一個(gè)關(guān)鍵指標(biāo)三階交點(diǎn)OIP3被定義為基頻信號(hào)功率(Pfund)和IMD3功率理論上的交叉點(diǎn)。在線性區(qū)域,OIP3可以利用公式3從IMD3幅度計(jì)算得到:

(公式3)

(公式3)其中,ΔIM是基頻信號(hào)功率和互調(diào)產(chǎn)物功率之間的差值(單位dB)。

評(píng)估這個(gè)設(shè)計(jì)時(shí)使用了位于3500MHz和3501MHz的兩個(gè)輸入聲調(diào)。然而,不希望有其它頻率間距去明顯改變結(jié)果。如圖8所示,在由Pi<-4dBm包圍的線性工作區(qū)域內(nèi),OIP3≥35dBm。這要比單個(gè)PHEMT低1dB,這個(gè)值非常顯著,因?yàn)閂DS在共源共柵拓?fù)渲兄挥幸话搿MD中的零點(diǎn)或最佳點(diǎn)位于-6dBm輸入驅(qū)動(dòng)點(diǎn),表明這是AB類操作。形成零點(diǎn)的原因是小信號(hào)IMD和大信號(hào)IMD在飽和開始時(shí)處于異相狀態(tài)。

圖8:測量得到的輸出功率(Po)、三階互調(diào)功率(IMD3)和三階交點(diǎn)(OIP3)與頻率的關(guān)系。

通過降低G和增加F使接收機(jī)減敏的阻塞現(xiàn)象可以由異步干擾源(如共享同一鐵塔的強(qiáng)大的發(fā)射機(jī))或同步源(如經(jīng)過同時(shí)具有收發(fā)功能的收發(fā)器中的循環(huán)器或雙工器泄漏的信號(hào)傳輸)造成。因此,具有高增益抑制閾值的元件可以更加有效地抵抗阻塞。增益抑制主要是由放大器中的非線性轉(zhuǎn)移特性造成的,隨著作為次要因素的散熱漸增,放大器將被驅(qū)動(dòng)到線性范圍之外。

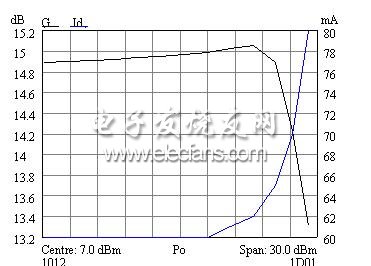

圖9顯示了+19dBm的輸出1dB壓縮點(diǎn)(P1dB),其類似于參考的單個(gè)EPHEMT。盡管共源共柵拓?fù)浣Y(jié)構(gòu)具有更低的VDS,還是獲得了很高的P1dB,因?yàn)镚aAs更低的體積電導(dǎo)率具有更少的熱量損失,以及ePHEMT低膝點(diǎn)電壓(0.3V)在鉗位之前允許更大的電壓擺幅。允許電流Id像AB類功放那樣與功率的平方成正比(即Id∝Po2),也導(dǎo)致了更高的P1dB,在類似的設(shè)計(jì)中顯示了在2.4GHz處有4dB的改善。

圖9:測量到的G和Id與輸出功率(Po)的關(guān)系。

本文小結(jié)

至此,已經(jīng)用低成本、QFN2x2封裝的MMIC成功設(shè)計(jì)出了具有優(yōu)良噪聲系數(shù)、增益和線性性能的3.5GHz LNA。結(jié)合芯片級(jí)的偏置調(diào)節(jié)器、ESD保護(hù)和穩(wěn)定性網(wǎng)絡(luò),可以將外部元件數(shù)量減少到12個(gè)。安華高的GaAs EPHEMT專有工藝可以在不降低增益、功率和線性度的條件下用單級(jí)電路實(shí)現(xiàn)+15dB的增益,這是因?yàn)楣苍垂矕啪w管僅工作在VDD的一半。在3.5GHz頻率點(diǎn),共源共柵拓?fù)浣Y(jié)構(gòu)與相同柵極寬度的單個(gè)EPHEMT相比,具有可觀的增益和隔離優(yōu)勢。未來的工作將專注于輸入匹配誤差的校正,和在較寬電源電壓范圍內(nèi)進(jìn)行定性分析。