將DDS和PLL技術(shù)結(jié)合起來,采用DDS直接激勵PLL的混合頻率合成方案完成了X波段微波變頻信號源的設(shè)計,一定程度上解決了頻率分辨率、頻率轉(zhuǎn)換速度和相位噪聲的問題,并完成了實(shí)機(jī)研制、系統(tǒng)聯(lián)調(diào)試驗(yàn)和測試。結(jié)果表明,輸出信號的頻譜和相噪特性良好,達(dá)到了預(yù)期的要求。

關(guān)鍵詞:頻率合成;直接數(shù)字頻率合成;鎖相環(huán);相位噪聲

0 引言

在雷達(dá)型制導(dǎo)導(dǎo)彈的研制和生產(chǎn)過程中,對微波接收機(jī)的性能指標(biāo)進(jìn)行調(diào)試和檢測是一個重要環(huán)節(jié)。為了實(shí)現(xiàn)某型雷達(dá)制導(dǎo)導(dǎo)彈微波接收機(jī)的自動測試,需要一種專用測試系統(tǒng)。X波段微波變頻源是該系統(tǒng)的重要組成部分,是決定測試系統(tǒng)性能的關(guān)鍵設(shè)備之一。該頻率源要能夠提供相干的信號源、本振源和鏡頻源,用來模擬空中目標(biāo)回波信號,為雷達(dá)導(dǎo)引頭中微波接收機(jī)的技術(shù)指標(biāo)測試以及性能研制提供必要條件。

隨著現(xiàn)代電子技術(shù)的迅猛發(fā)展,低相位噪聲、高頻譜純度、高捷變速率和高頻率分辨率的頻率合成器已經(jīng)成為頻率合成技術(shù)發(fā)展的主要趨勢,直接數(shù)字頻率合成(DDS)和鎖相環(huán)頻率合成(PLL)技術(shù)已成為頻率合成技術(shù)發(fā)展的主流方向。本文提出一種以DDS激勵PLL方式實(shí)現(xiàn)X波段微波變頻源的方案,具有高度的集成性,降低了硬件的復(fù)雜程度,提高了系統(tǒng)的整機(jī)性能,滿足了測試系統(tǒng)的需求。

1 功能和設(shè)計要求

1.1 微波源的主要功能

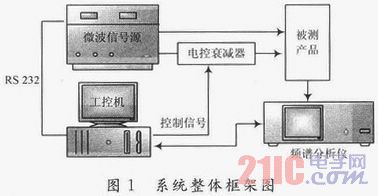

X波段專用微波源主要模擬空中目標(biāo)回波信號即探測信號、鏡頻信號和導(dǎo)彈發(fā)射機(jī)本振信號,能夠在控制計算機(jī)的控制下,在1 GHz通帶內(nèi)選擇201個點(diǎn)頻進(jìn)行變頻,微波信號源在測試系統(tǒng)中的構(gòu)成見圖1。

1.2 輸出信號要求

微波信號源提供X波段主通道微波前端組件測試所需的相干本振信號、探測信號、鏡頻信號,每種信號在300 MHz通帶內(nèi)頻率可變,具體指標(biāo):

頻率及帶寬相關(guān)參數(shù):

(1)信號FS1:f0-fI±150 MHz;

(2)本振fL:f0±150 MHz;

(3)鏡頻FS2:f0+fI±150 MHz;

(4)中頻fI:(28±0.5)MHz;

(5)信號源、本振源、鏡頻源頻率準(zhǔn)確度:≤±5 MHz;

(6)信號源、本振源、鏡頻源頻率漂移:≤±5 MHz/4h;

相位噪聲:≤-80 dBc/Hz/10 kHz;

雜波抑制:≤-60dB/(300 MHz帶寬內(nèi));

輸出功率:18~22 dBm。

2 設(shè)計思路和具體方案

頻率合成的實(shí)現(xiàn)方法主要有3種,即直接頻率合成(DFS)、鎖相環(huán)頻率合成(PLL)和直接數(shù)字頻率合成(DDS)。其中,DFS技術(shù)以其結(jié)構(gòu)復(fù)雜,成本高,體積大,而很少使用。DDS具備頻率分辨率高,可編程控制特性,并且頻率切換速度快,相位噪聲低,但是由于其全數(shù)字結(jié)構(gòu),輸出頻譜質(zhì)量差,輸出頻率也較低。PLL具有輸出頻率高,寄生噪聲和雜波低的特點(diǎn),但是其頻率切換速度慢,而且頻率分辨率低。為了克服兩者的缺點(diǎn),人們將兩種技術(shù)結(jié)合起來,提出多種DDS和PLL相結(jié)合的混合頻率合成方案。其中,DDS直接激勵PLL方案是最基本的混合頻率合成方案,其結(jié)構(gòu)簡單,容易實(shí)現(xiàn)。所以X波段微波信號源采用了DDS+PLL混合式頻率合成方案。

該方案的工作模式是把DDS的輸出頻率作為PLL的參考頻率,通過控制改變DDS的頻率控制字或PLL中可編程分頻器的分頻比,達(dá)到系統(tǒng)跳頻的目的。它利用高的鑒相頻率提高PLL的頻率切換速度,并且利用DDS的高頻分辨率來保證頻率間隔,同時PLL的帶通作用可以很好地抑制DDS輸出頻譜中的部分雜散,實(shí)現(xiàn)了DDS和PLL的優(yōu)勢互補(bǔ)。

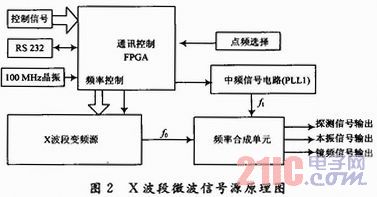

X波段微波信號源包括通信控制單元、中頻信號電路、X波段變頻源、頻率合成單元、供電電源等,微波信號源通過RS 232與工控機(jī)通信,信號點(diǎn)頻既能手動選擇,也能自動控制。X波段微波信號源原理如圖2所示。

2.1 通信控制單元

通信控制單元采用現(xiàn)場可編程門陣列(FPGA)編程實(shí)現(xiàn)。FPGA具有集成度高,數(shù)據(jù)處理速度快,系統(tǒng)結(jié)構(gòu)設(shè)計靈活等特點(diǎn),可以根據(jù)需要通過布局布線工具對其內(nèi)部進(jìn)行編程,將電路集成在一個芯片上,在最短的時間內(nèi)設(shè)計出專用系統(tǒng)。

FPGA通過RS 232與上位機(jī)通信,通信接口采用MAX 232實(shí)現(xiàn)電平轉(zhuǎn)換,在數(shù)據(jù)接收端將±10 V電平信號轉(zhuǎn)換為FPGA兼容的TTL電平,在數(shù)據(jù)發(fā)送端將TTL電平轉(zhuǎn)換為±10 V電平信號,滿足標(biāo)準(zhǔn)RS 232接口的電平要求。

2.2 中頻信號電路

中頻信號電路采用數(shù)字鎖相環(huán)實(shí)現(xiàn),100 MHz晶振經(jīng)過FPGA分頻電路生成4 MHz的基準(zhǔn)頻率作為PLL1的參考頻率fPD1,鎖相環(huán)PLL1的分頻比N=7,輸出信號濾波后產(chǎn)生項目要求的28 MHz中頻。中頻信號電路原理如圖3所示。

2.3 X波段變頻源

X波段變頻源采用DDS驅(qū)動PLL結(jié)構(gòu)的寬帶頻率源設(shè)計,電路原理如圖4所示。

DDS選用AD9854芯片,內(nèi)置48位相位累加器,并且具有兩個內(nèi)部的高速高性能D/A轉(zhuǎn)換器,通過對外部參考時鐘倍頻,其內(nèi)部時鐘可達(dá)到300 MHz,可以很方便地產(chǎn)生低頻的參考信號,并且具有較好的動態(tài)性能。

DDS的各種讀/寫及控制信號由FPGA提供,為了使DDS和FPGA之間的系統(tǒng)時鐘同步,它們的外部參考時鐘fref由同一個100 MHz的溫補(bǔ)晶振提供。DDS輸出的信號頻率fDDS由FPGA寫入的頻率控制字控制,鎖相環(huán)PLL的參考信號由DDS的輸出信號驅(qū)動,VCO的輸出頻率由PLL芯片的電荷泵CP輸出端控制,通過對VCO輸出的信號進(jìn)行倍頻得到X波段f0輸出信號。

PLL模塊選用ADF4106寬帶數(shù)字鎖相環(huán)芯片,ADF4106由低噪聲鑒頻鑒相器、高精度電荷泵、可編程參考時鐘分頻器、可編程雙模預(yù)分頻器構(gòu)成,其帶寬可以達(dá)到6 GHz,具有較短的頻率建立時間和較低的相位噪聲,選擇低相位噪聲的數(shù)字鎖相環(huán)有助于保證整機(jī)的低相噪性能。

采用的PLL芯片具有一個雙模預(yù)置分頻器,可產(chǎn)生大分頻比,這就使頻率綜合器在輸出較高頻率信號的同時仍保持較高的頻率分辨率。

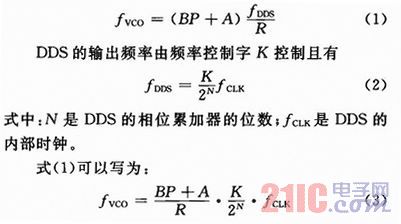

VCO輸出信號的頻率和DDS輸出信號的頻率間的關(guān)系為:

從式(3)可以看出,采用DDS模塊后的輸出信號具有比傳統(tǒng)結(jié)構(gòu)更高的頻率分辨率。

環(huán)路濾波器選用AD820運(yùn)算放大器進(jìn)行環(huán)路濾波器的設(shè)計與實(shí)現(xiàn),使用ADISimPLL軟件計算環(huán)路濾波器各元器件的參數(shù)。

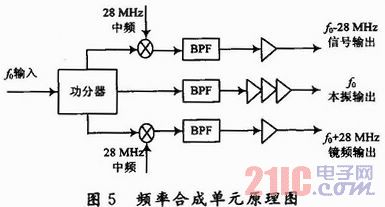

2.4 頻率合成單元

X波段變頻源輸出的f0信號分為3路,一路經(jīng)濾波、功率放大后生成本振信號輸出,另外兩路與PLL1鎖相器輸出的28 MHz中頻信號混頻,上變頻輸出經(jīng)濾波、功率放大后生成鏡頻信號,下變頻輸出經(jīng)濾波、功率放大后生成探測信號。頻率合成單元的X波段功分器、混頻器、功率放大器等均采用成熟技術(shù),確保系統(tǒng)穩(wěn)定可靠地工作,本振、鏡頻、探測3路輸出設(shè)計為3個獨(dú)立的支路,減小信號之間的串?dāng)_,采取良好的屏蔽、接地和濾波等措施,以實(shí)現(xiàn)高頻譜純度源信號。本振、鏡頻、探測信號的頻率穩(wěn)定度和頻率準(zhǔn)確度取決于參考晶振,優(yōu)于技術(shù)指標(biāo)的要求。頻率合成電路原理如圖5所示。

2.5 點(diǎn)頻選擇

微波源頻段落在X波段內(nèi),提供主通道微波前端組件測試所需的相干本振信號、探測信號、鏡頻信號,每種信號在1 GHz通帶內(nèi)有201個點(diǎn)頻可供選擇。所有測試頻點(diǎn)參數(shù)均由工控機(jī)轉(zhuǎn)換為DDS頻率控制字通過RS 232下載到FPGA,并存儲在FPGA片內(nèi)RAM的對應(yīng)地址單元,根據(jù)選定的點(diǎn)頻,F(xiàn)PGA讀取對應(yīng)的代碼,控制DDS輸出對應(yīng)頻率的信號。信號點(diǎn)頻既能手動選擇,也能自動控制。

3 測試結(jié)果和分析

根據(jù)前面介紹的方案,最終實(shí)現(xiàn)了該X波段變頻源,圖6,圖7為該變頻源的外觀圖。

為了測試變頻源輸出頻譜的質(zhì)量,使用E4440A頻譜分析儀測試其輸出頻譜和相位噪聲,頻譜和相位噪聲測試曲線如圖8,圖9所示,主要測試指標(biāo)如下:相位噪聲為-86.87 dBc/Hz/10 kHz;雜波抑制小于等于65 dB/(300 MHz帶寬內(nèi));輸出功率為19.05dBm。

測試結(jié)果表明,該變頻源輸出頻譜質(zhì)量優(yōu)異,完全能滿足研制要求的需要。

4 結(jié)語

采用本文提出的方案研制出的X波段變頻源,體積小,成本低,可靠性高,實(shí)現(xiàn)了系統(tǒng)信號的全相參和變頻要求,同時輸出信號具有低相位噪聲、高頻譜純度、高捷變速率的特點(diǎn),滿足了測試系統(tǒng)的需求。