工作內(nèi)容:

1、設(shè)計一個多路選擇器,利用ModelSim" title="ModelSim">ModelSimSE做功能仿真;

2、利用Synplify" title="Synplify">Synplify Pro進(jìn)行綜合,生成xxx.vqm文件;

3、利用Quartus" title="Quartus">Quartus II導(dǎo)入xxx.vqm進(jìn)行自動布局布線,并生成xxx.vo(Verilog

4、利用ModelSimSE做后仿真,看是否滿足要求。

注:

1. 仿真器(Simulator)是用來仿真電路的波形。

2. 綜合工具(Synthesizer)的功能是將HDL轉(zhuǎn)換成由電路所組成的Netlist。

3. 一般而言,在電路設(shè)計的仿真上可分為Pre-Sim 和Post-Sim。Pre-Sim 是針而Post-Sim則是針對綜合過且做完成了Auto Place and Route(APR)的電路進(jìn)行仿真,以確保所設(shè)計的電路實現(xiàn)在FPGA" title="FPGA">FPGA上時,與Pre-Sim 的功能一樣。

1、前仿真(Pre-Sim)

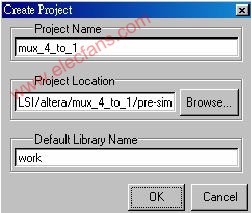

步驟一:打開ModelSimSE,然后建立一個Project;

※建立Project的方式為點選File → New → Project…;

※設(shè)定Project Name 與Project location,按OK 即可建立Project。

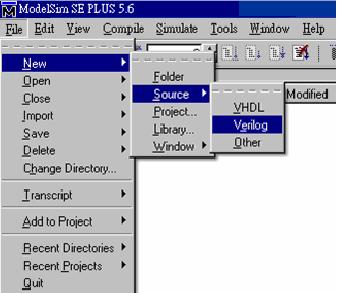

步驟二:新增設(shè)計文檔或加入文檔。

※新增文檔的方式為點選File → New → Source → Verilog,然后對文檔進(jìn)行編輯并儲存為xxx.v;

※ 加入文檔的方式為點選File → Add to Project → File...,然后點選xxx.v;

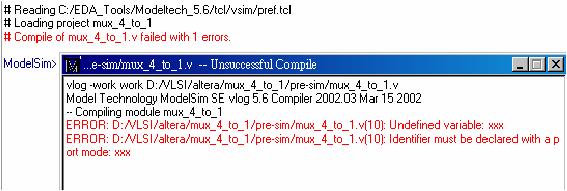

步驟三:編譯(Compile)。

※編譯文檔的方式為點選Compile → Compile All,即可編譯所有的文檔。

※如果編譯時發(fā)生錯誤,在顯示錯誤的地方(紅字)點兩下,即可跳到錯誤。

步驟四:新增或加入測試平臺(Testbench)。

※當(dāng)設(shè)計完電路后,為了確定所設(shè)計的電路是否符合要求,我們會寫一個測 試平臺(Testbench);

※ 新增或加入測試平臺,然后編譯它。

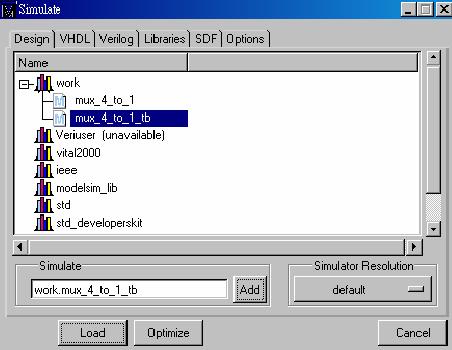

步驟五:仿真(Simulate)。

※仿真的方式為點選Simulate → Simulate…;

※打開Design里面的work,然后點選mux_4_to_1_tb 并Add 它,最后按Load 即可跳到仿真窗口。

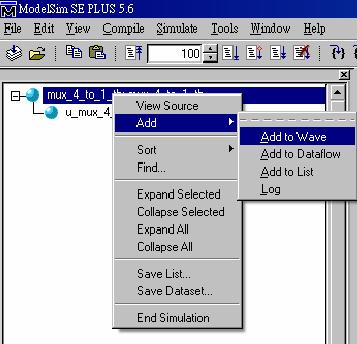

步驟六:加入信號線。

※ 在窗口上按右鍵,然后點選Add → Add to Wave;

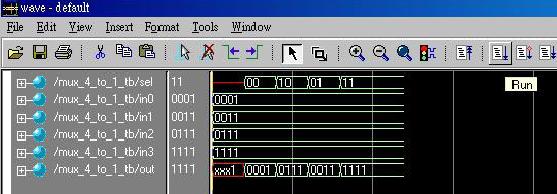

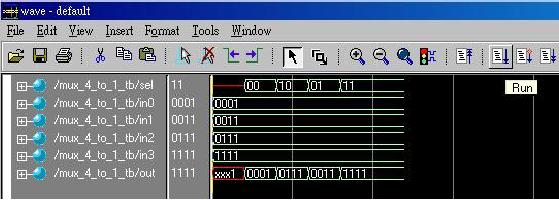

步驟七:看波形。

※在工具列上按Run,然后就會顯示波形;

※慢慢看波形吧,沒有波形就沒有真相!

以上就是使用ModelSim做Pre-Sim的基本流程,在此要特別強(qiáng)調(diào)的是,ModelSim所有的功能并不僅僅于此,如果你想要了解更多的話,一切都要靠自己花時間去問去試,只有努力的人才能有豐富的收獲,加油!

2、綜合(Synthesis)

步驟一:打開Synplify Pro,然后建立一個Project。

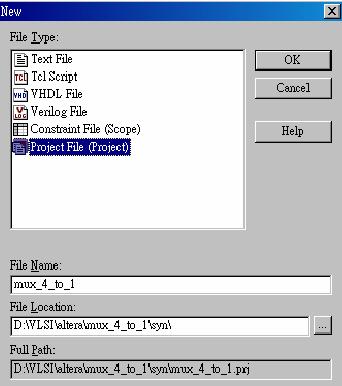

※先點選File,再點選New;

※選擇Project File,并設(shè)定File Name與File Location;

步驟二:加入設(shè)計文件。

※ 點選欲加入的xxx.v,然后按Add,再按OK后就可以將檔案加入。

步驟三:選擇FPGA的Device 與其它相關(guān)設(shè)定。

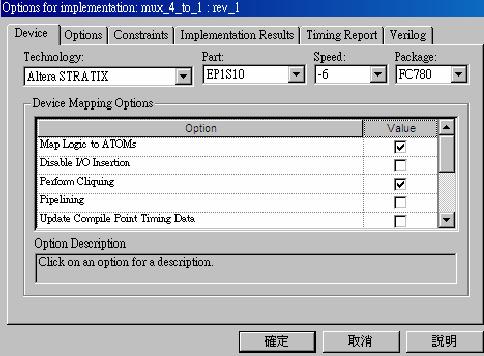

※先點選Project,再點選Implementation Options。

※在Device 的設(shè)定如下:Technology為Altera Stratix,Part為EP1S10,Speed 為-6,Package 為FC780。

※在Options 的設(shè)定是將FSM Compiler與Resource Sharing打勾。

※在Constraints的設(shè)定是將Frequency設(shè)定至100Mhz。

※在Implementation Results的設(shè)定是將Result File Name填入與電路模塊相同的名稱,而xxx.vgm這個文件會在QuartusII做APR時被使用。然后將下列兩個選項打勾(Write Vendor Constraint File與Write Mapped Verilog Netlist)。

※在Timing Report的設(shè)定是將Number of Critical Paths與Number of Start/End Points都設(shè)為11。

※在Verilog里是將TOP Level Module填入與電路模塊相同的名稱,然后將 Use Verilog 2001打勾。

步驟四:綜合(Synthesis)。

※點選RUN → Synthesize,最后出現(xiàn)Done!就是已經(jīng)綜合完畢。

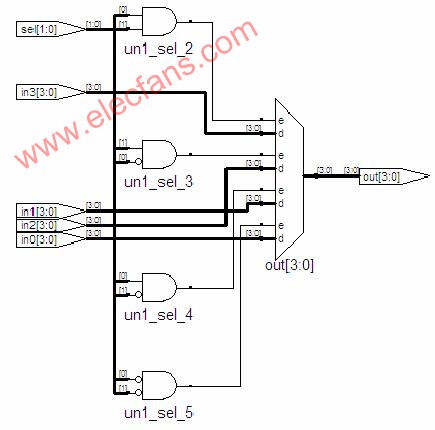

步驟五:檢查綜合后的電路。

※先點選HDL Analyst,再點選RTL,最后點選Hierarchal View,畫面會出現(xiàn)綜合后的電路Netlist。

以上就是使用Synplify將HDL程序合成為電路Netlist的基本流程,值得注意的是,當(dāng)你針對不同要求而設(shè)定的Constraints不同時,你就會得到不同的電路Netlist,所要付出的硬件代價也不同,這就需要大家多花點心思來了解其中的奧妙之處。

3、自動布局布線(APR)

步驟一:開啟Quartus II,然后建立一個Project。

※先點選File,再點選New Project Wizard…。

※設(shè)定Work Directory,Project Name與Top-Level Entity Name,再按Next。

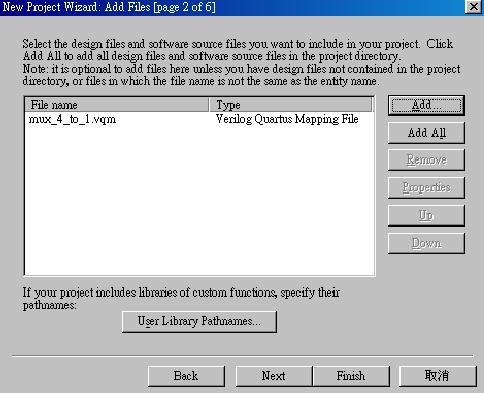

步驟二:加入設(shè)計文件。

※ 點選Add…,將Synplify合成出來的xxx.vqm加入,再按Next。

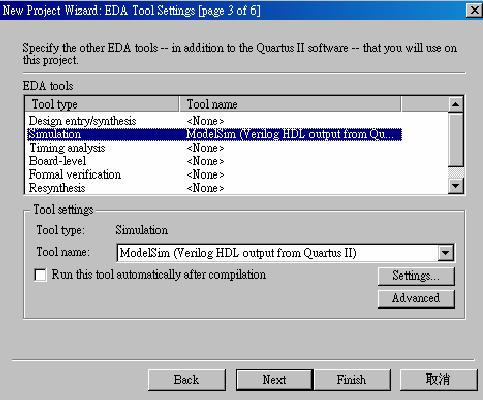

步驟三:設(shè)定相關(guān)的EDA Tools。

※在Tool Type點選Simulation,Tool Name點選ModelSim。

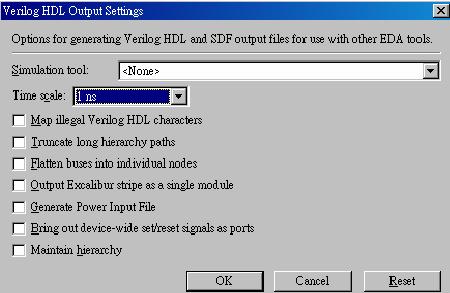

※ 點選Settings,將Time Scale設(shè)定為1 ns。

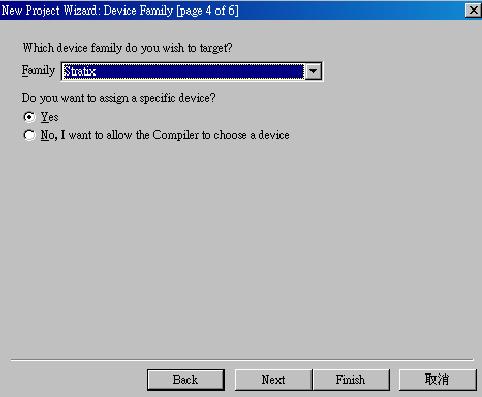

步驟四:設(shè)定Family。

※ 設(shè)定Family為Stratix,再按Next。

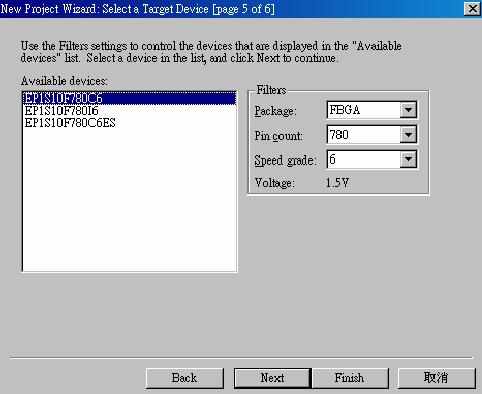

步驟五:設(shè)定Device。

※ 設(shè)定Device 為EP1S10F780C6,再按Finish,即可完成Project的設(shè)定。

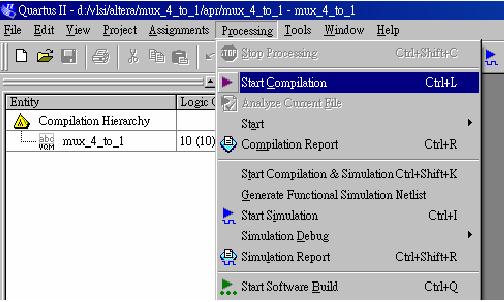

步驟六:編譯。

※ 點選Processing → Start Compilation,即可開始編譯。

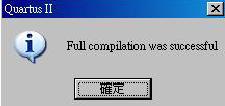

步驟七:完成編譯。

※ 彈出下面窗口即代表編譯完畢。

以上就是使用Quartus II對電路Netlist做APR的基本流程,并且利用設(shè)定仿真工具所產(chǎn)生的xxx.vo(Verilog Output File)與xxx.sdo(Standard Delay Output File)做后仿真。

4、后仿真(Post-Sim)

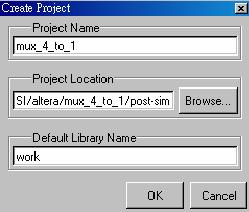

步驟一:啟動ModelSim,然后建立一個Project。

※建立Project的方式為點選File → New → Project…。

※設(shè)定Project Name與Project location,按OK即可建立Project。

步驟二:加入設(shè)計文檔。

※將xxx.vo更改為xxx.v,然后加入。

步驟三:加入組件庫文件。

※由于我們是采用Altera的Cell Library來合成電路,所以合成后的電Netlist里所包括的那些Logic Gates與Flip-Flop 都是出自于Cell Library,所以模擬時要將此Cell Library加入。

※我們所選用的Family是Stratix,所以到QuartusIIedasim_lib 里將Stratix的Cell Library(stratix_atoms.v)加入。

步驟四:加入測試平臺。

※加入Pre-Sim的測試平臺,并在測試平臺里加上`timescale 1ns/100ps。

步驟五:編譯。

※編譯檔案的方式為點選Compile → Compile All,即可編譯所有的檔案。

※如果編譯時發(fā)生錯誤,在顯示錯誤的地方(紅字)點兩下,即可跳到錯誤。

步驟六:仿真。

※仿真文件的方式為點選Simulate → Simulate…。

步驟七:加入要觀察的信號。

※在窗口上按右鍵,然后點選Add → Add to Wave。

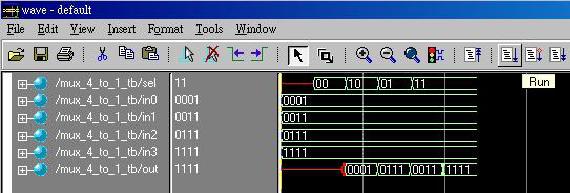

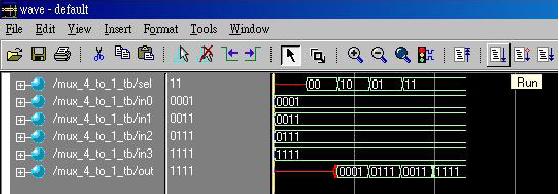

步驟八:觀察波形。

※慢慢看波形吧,沒有波形就沒有真相!

步驟九:比對Pre-Sim 與Post-Sim。

※ 很明顯地,Post-Sim 的輸出有不穩(wěn)定的信號,并且受到延遲時間的影響。