文獻標識碼: A

文章編號: 0258-7998(2015)03-0051-04

0 引言

近年來,隨著電子產品特別是智能電子產品硬件的不斷普及,對芯片的功耗和性能提出了越來越苛刻的要求[1]。

基準源(簡稱基準)是模擬芯片所必不可少的基本部件,它為電路提供高質量、高穩(wěn)定性的電流和電壓偏置,而且它的性能會直接影響到電路的性能[2]。傳統(tǒng)基準存在精度低、溫漂大、功耗高和失調電壓高等缺點[3-4]。本文基于傳統(tǒng)基準提出了一種低功耗基準,以期克服這些缺點。

1 帶隙基準的基本原理分析

對于一個雙極型晶體管(BJT)的基極-發(fā)射極電壓(VBE),更一般的是pn結二極管的正向電壓,具有負溫度系數[5]。BJT的VBE、集電極電流IC和飽和電流IS有以下關系:

![EL7L$4QD]U15}B@G]93WPDY.png EL7L$4QD]U15}B@G]93WPDY.png](http://files.chinaaet.com/images/2015/06/30/6357130042593200003766912.png)

其中,k為玻爾茲曼常數,T表示熱力學溫度,q為電荷,少數載流子的遷移率,ni為硅的本征載流子濃度[6]。

兩個雙極型晶體管工作在不同的電流密度下,它們之間的基極-發(fā)射極電壓之差(ΔVBE)具有正溫度系數[7]。將以上兩個具有相反溫度系數的變量加以適當的權重,就可以得到滿意的零溫度系數基準[8]。圖1是傳統(tǒng)的帶隙基準電路,這里,運算放大器AV以VX和VY為輸入,AV輸出用于驅動R1和R2(R1=R2)的頂端,使得X點和Y點穩(wěn)定在近似相等的電壓。基準電壓可以在運算放大器的輸出端得到(不是Y點)[9]。三極管基極-發(fā)射極電壓VBE具有負溫度系數。三極管Q2和Q1發(fā)射極有效面積比例為n:1,流過兩者的飽和電流和集電極電流存在以下關系:

IS1=n·IS2 IC1=IC2(3)

三極管Q2和Q1的基極-發(fā)射極電壓之差:

ΔVBE=VBE1-VBE2=VT lnn(4)

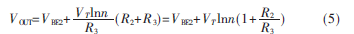

ΔVBE作用在電阻R3上,產生PTAT電流,使得R1上產生PTAT電壓[10],此電壓和VBE相疊加,得到輸出電壓:

VT具有正溫度系數,通過調節(jié)R2、R3和三極管面積比例得到零溫度系數電壓,實際電路中基準電壓溫度系數是一個開口向下的曲線。VBE具有高階的溫度分量,所以需要對VBE進行高階補償。

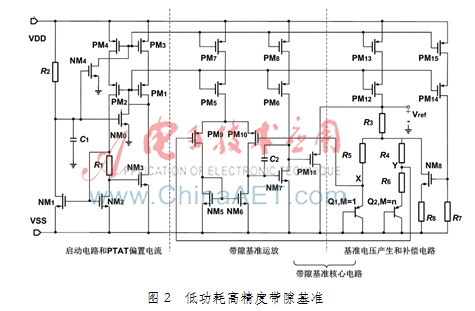

針對傳統(tǒng)帶隙基準啟動失調電壓大、精度低的特點,本文提出了具有低功耗高精度的電壓基準。電路由兩個部分組成,分別為啟動偏置電路、基準核心電路(基準電壓產生和補償結構、基準運放),實際原理圖如圖2所示。

2 新型帶隙基準電壓源設計

2.1 啟動電路和PTAT偏置電路

為了擺脫電源上電時電路的簡并偏置點,啟動電路是不可缺少的。本設計中啟動電路由R2、C1、NM0、NM1、NM4組成。電路正常上電時,VDD通過R2向電容C1充電,NM0的柵極電壓升高,使NM0和NM4導通,PM1、PM4的柵極電壓拉低,偏置電路源開始正常工作;隨著NM2柵電壓逐漸升高,NM1導通,NM0和NM4柵極電壓被拉低,NM0和NM4截止,此時關閉啟動電路。

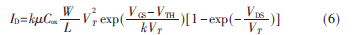

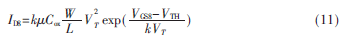

偏置電路為整個電路提供一個與電源無關的PTAT偏置電流。如圖2,偏置電路是由PM1、PM2、PM3、PM4、NM2、NM3和R1構成的自偏置峰值電流源。PM1~PM4的寬長比相同,構成了Cascode電流鏡,形成自偏置機制,同時增加整體電路的電源抑制比。利用NM2和NM3工作在亞閾值區(qū)域時的柵源電壓之差作用在電阻R1產生正溫度系數的電流。在亞閾值區(qū)域時,MOS管漏電流ID為:

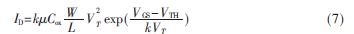

式中k為亞閾值斜率修正因子,VTH為MOS管閾值電壓[11]。漏源電壓VGS遠大于VT,式(6)可簡化為:

可以推導出PTAT偏置電流為:

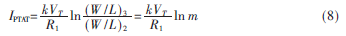

式中m為NM3和NM2寬長比之比。從式(8)可以看出,VT具有正溫度系數,所得偏置電流與溫度成正比和電源電壓無關。

2.2 帶隙基準核心電路

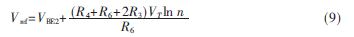

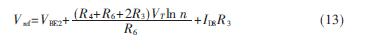

本文設計的基準產生電路由Q1、Q2、R3~R6、PM12和PM13組成。Q2和Q1的有效發(fā)射極面積之比為n:1,電阻R4和R5的阻值相等。根據上文式(1)~(5)的推導,可以得出基準電壓Vref的表達式:

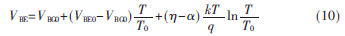

晶體管的VBE并不是與溫度呈線性關系:

式中,VBG0是帶隙電壓,約為1.12 V;T是絕對溫度;T0是參考溫度;VBE0是在溫度為T0時的發(fā)射結電壓;?濁是與工藝有關且與溫度無關的常數;的值與集電極電流的溫度特性有關。調節(jié)三極管和電阻選取的大小,能很好地對式(10)中的第一項進行補償。為了得到更低的溫度系數,必須對式(10)中的第二項進行補償。

本設計提出了一種簡單且效果明顯的補償方式,利用NMOS管工作在亞閾值區(qū)域時漏電流和柵極電壓的指數特性,對基準電壓進行二階曲率補償。補償電路由NM8、R7、R8、PM14、PM15組成,補償基準在高溫下的溫度特性曲線。PM14和PM15鏡像PTAT電流,作用在電阻R7上,產生PTAT電壓,該電壓使NM8工作在亞閾值狀態(tài),隨著溫度的增加,補償電流逐漸增大。由式(6)和式(7),可得:

忽略R8上的壓降,補償電流:

式中是PM14和PM15的鏡像比例因子。加上二階曲率補償電流后,式(9)可改寫為:

運算放大器由PM5~PM11、NM5~NM7和C2組成。本設計采用兩級運放結構,具有較大的開環(huán)增益。同時運用PM11輸出跟隨器,減小輸出電阻。為了減小運放的失調電壓,加大了PM9和PM10的寬長比,并保證了一級運放和二級運放之間的對稱性。電容C1作為補償電容,得到一個低頻極點,增加電路的穩(wěn)定性。

3 仿真結果

本文設計電路采用UMC 0.25 μm BCD工藝模型,電路中n=8,m=2。利用Hspice仿真軟件,對電路進行了仿真。

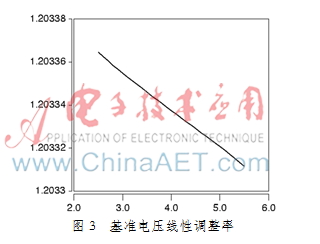

在TT工藝角下。溫度為25 ℃時,基準電壓線性調整率如圖3所示。仿真結果表明,基準電壓的典型值為1.203 V。供電電壓VDD在2.5 V~5.5 V范圍內,基準電壓變化了53 μV,線性調整率為0.001 8%。供電電壓VDD為5 V,在-40 ℃~130 ℃的溫度范圍內,基準電壓的溫度特性仿真結果如圖4所示。仿真結果表明,基準電壓的平均值為1.203 V,基準電壓的波動范圍為175 μV,溫度系數為0.86×10-6/℃。

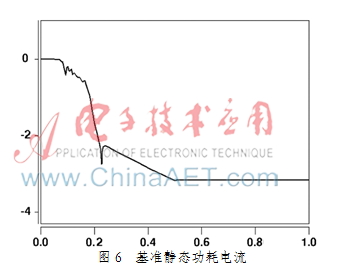

如圖5為電源電壓VDD為5 V,溫度為25 ℃,在三種工藝角下的電源抑制比(PSRR)仿真結果,在三種工藝角下低頻PSRR都小于-95 dB,具有很好的電源抑制能力。圖6為瞬態(tài)仿真下的電流功耗大小,從仿真結果可以看出,電路的靜態(tài)電流功耗為3.16 μA。

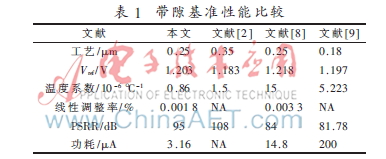

表1為本文和文獻[2]、[8]和[9]的性能參數比較。本文提出的結構具有明顯優(yōu)勢。

4 結論

提出了一種基于傳統(tǒng)結構的低功耗、高精度的帶隙基準電壓源。本設計采用Cascode結構來提高整體電路的電源抑制比。通過增加運放輸入差分對管的尺寸,添加輸出緩沖級結構以及保證運放的對稱性來減小失調電壓。并運用二階曲率補償來對基準電壓進行溫度補償。采用UMC 0.25 μm BCD 工藝,仿真結果表明,基準電壓源在2.5 V~5 V的電壓范圍內提供1.203 V的基準電壓,線性調整率為0.001 8%,靜態(tài)功耗只有3.16 μA,在-40 ℃~130 ℃溫度范圍內的溫度系數為0.86 ppm,低頻電源抑制比為-95 dB。

參考文獻

[1] Chen Junda,Ye Chengkai.Design of a CMOS bandgap ref-erence circuit with a wide temperature range,high precisionand low temperature coefficient[J].Journal of Circuits,Sys-tem,and Computers,2014,23(8):1450107.

[2] 朱龍飛,莫太山,葉甜春.高電源抑制比低溫漂帶隙基準源設計[J].集成電路應用,2013,39(5):35-38.

[3] Lu Shibi.A 19-ppm/℃ bandgap voltage reference source[C].Networks Security Wireless Communications and Trusted Computing,Wuhan:IEEE,2010:409-411.

[4] 楊曉春.一種采用斬波調制的高精度帶隙基準源的設計[J].微電子學與計算機,2013,30(1):86-89.

[5] GRAY P R.Analysis and design of analog integrated circuits[M].America:Lehigh Press,2001.

[6] Feng Chao,Wang Jinhui,Wu Wei.CMOS 1.2 V Bandgap Voltage Reference Design[C].IEEE 10th International Con-ference on ASIC,Shenzhen:IEEE,2013:1-4.

[7] RAZAVI B.模擬CMOS集成電路設計[M].陳貴燦,程軍,譯.西安:西安交通大學出版社,2002.

[8] 唐宇.一種低溫漂低功耗帶隙基準的設計[J].電子元件與材料,2014,33(2):35-38.

[9] Zhang Kun.A high performance bandgap voltage referencedesign[C].Information Science and Engineering(ICISE),2010 2nd International Conference on,Hangzhou:IEEE,2010:4838-4841.

[10] 魏廷存,陳瑩梅,胡正飛.模擬CMOS集成電路設計[M].北京:清華大學出版社,2010.

[11] 林少波.高精度高電源電壓抑制比CMOS帶隙基準源設計[D].西安:西安電子科技大學,2012.