文獻(xiàn)標(biāo)識(shí)碼: A

DOI:10.16157/j.issn.0258-7998.2015.11.006

中文引用格式: 彭昊,黃駿雄,江先陽(yáng),等. 多通道高保真音頻信號(hào)IIR濾波器設(shè)計(jì)[J].電子技術(shù)應(yīng)用,2015,41(11):24-26,30.

英文引用格式: Peng Hao,Huang Junxiong,Jiang Xianyang,et al. Multi-Channel IIR filter design based on FPGA[J].Application of Electronic Technique,2015,41(11):24-26,30.

0 引言

數(shù)字濾波器是現(xiàn)代數(shù)字信號(hào)處理系統(tǒng)的重要組成部分,具有模擬濾波器所無法替代的優(yōu)越特性,在語音處理領(lǐng)域更是有著很廣泛的運(yùn)用。數(shù)字濾波器根據(jù)單位脈沖響應(yīng)的不同,可分為有限脈沖響應(yīng)濾波器(FIR)和無限脈沖響應(yīng)濾波器(IIR)。FIR濾波器的優(yōu)點(diǎn)在于具有良好的相位特性,IIR濾波器的優(yōu)點(diǎn)在于擁有良好的幅頻特性。IIR和FIR濾波器相比,在低階數(shù)時(shí)就可以達(dá)到很好的頻率濾波性能,但其相位特性是非線性的[1]。

音頻信號(hào)可以視為不同頻率正弦波信號(hào)的疊加。通過對(duì)于音頻信號(hào)系統(tǒng)的頻譜分析,可以很清晰地分辨出需要保留的信號(hào)以及需要抑制的噪聲信號(hào)。因?yàn)槿硕鷮?duì)于聲音的相位變化是不敏感的,所以在音頻信號(hào)的濾波中,IIR濾波器的應(yīng)用相比于FIR更有優(yōu)勢(shì)[2]。

另一方面,隨著娛樂媒體的發(fā)展,高精度的多通道處理更是進(jìn)行音頻信號(hào)處理的重要而基本的需求之一。由于軟件的串行特性,多通道的音頻信號(hào)在處理上往往需要預(yù)先搭建特別的平臺(tái),這使得采用軟件實(shí)現(xiàn)的方式既不經(jīng)濟(jì)又缺乏擴(kuò)展性。目前的設(shè)計(jì)很多都是針對(duì)單通道進(jìn)行實(shí)現(xiàn),而音頻信號(hào)往往又存在需要多個(gè)聲道混合產(chǎn)生立體聲的問題。一種傳統(tǒng)的做法是通過DSP專用芯片來實(shí)現(xiàn)實(shí)時(shí)性的音頻信號(hào)處理[3-5],但這種方式中實(shí)現(xiàn)并行多通道傳輸往往需要消耗額外的器件資源;而另外一種通過FPGA實(shí)現(xiàn)的濾波器方案采用以FPGA內(nèi)部的SOPC實(shí)現(xiàn)的一種軟件方式,并沒有涉及到使用FPGA良好的硬件器件特性實(shí)現(xiàn)多路復(fù)用的方法[6]。針對(duì)這一問題,本文基于FPGA設(shè)計(jì)了一款可擴(kuò)展的時(shí)分復(fù)用多通道IIR濾波器。

1 IIR濾波器的設(shè)計(jì)

1.1 系統(tǒng)的穩(wěn)定性判斷

穩(wěn)定性是一個(gè)濾波器的重要指標(biāo)。IIR濾波器的系統(tǒng)傳遞函數(shù)是復(fù)變量z的有理函數(shù),其分子和分母都是z-1的多項(xiàng)式,因此H(z)可以表示為:

其中ci(i∈[1,M])是零點(diǎn)di(i∈[1,N])的極點(diǎn)。一個(gè)線性時(shí)不變系統(tǒng)當(dāng)且僅當(dāng)它的系統(tǒng)傳遞函數(shù)H(z)的極點(diǎn)都處于單位圓內(nèi)時(shí)(包括單位圓)是穩(wěn)定的。由于實(shí)際的PCB板內(nèi)部的電磁干擾輸出端會(huì)出現(xiàn)一個(gè)幅度極小頻率極低的干擾噪聲,在后級(jí)放大后使得噪聲不能忍受,所以濾波器希望能濾掉采樣率為48 kHz的音頻信號(hào)中因PCB中噪聲干擾產(chǎn)生的一個(gè)極低的噪聲信號(hào),目標(biāo)濾波器的濾波器斜率為12 dB/OCT,中心頻率為6 Hz。

1.2 系數(shù)量化轉(zhuǎn)換

由理論設(shè)計(jì)出的理想數(shù)字濾波器傳輸函數(shù)的系數(shù)ai、bi如果用二進(jìn)制表示是無限精度的。在實(shí)現(xiàn)時(shí)硬件只有限位寬,所以必須對(duì)數(shù)字濾波器傳遞函數(shù)的系數(shù)進(jìn)行量化轉(zhuǎn)換。具體來說在FPGA中實(shí)現(xiàn)差分方程時(shí),一般是把這些非整數(shù)系數(shù)乘以2L然后取整[7-8]。當(dāng)L值足夠大的時(shí)候,就可以保證IIR濾波器的精度。而當(dāng)濾波器的系數(shù)乘以2L,從硬件上可以相應(yīng)轉(zhuǎn)化為左移L位操作,左移操作無需消耗乘法邏輯單元從而節(jié)約了邏輯資源。系數(shù)量化轉(zhuǎn)換完成后可以通過Matlab驗(yàn)證濾波器系數(shù)是否滿足穩(wěn)定條件。

1.3 系數(shù)的簡(jiǎn)化問題

高保真的音頻信號(hào)一般是24位的有效數(shù)據(jù),為了保證濾波后音頻信號(hào)的精度,濾波器系數(shù)也設(shè)為24位。通過使用巴特沃斯型IIR濾波器可以將零點(diǎn)全部調(diào)整到單位圓與X軸Y軸的交點(diǎn)處,從而將ai系數(shù)全部調(diào)整為整數(shù)。在此基礎(chǔ)上將系數(shù)乘以2L(L為整數(shù))后可以將乘法操作轉(zhuǎn)化為移位操作節(jié)省邏輯資源。

依據(jù)應(yīng)用需要,目標(biāo)濾波器的中心頻率為6 Hz,所需要的濾波器衰減斜率為12 dB/OCT,即一個(gè)二階濾波器。采用Matlab的fdatool工具設(shè)置對(duì)應(yīng)參數(shù)并選擇濾波器為巴特沃斯逼近,生成滿足條件的濾波器系數(shù)[9-10],如表1所示。

基于1.1節(jié)的穩(wěn)定性分析可知,這一濾波器是一個(gè)穩(wěn)定的二階IIR濾波器,其差分方程可以描述為:

y(n)=a1x(n)+a2x(n-1)+a3x(n-2)+b2y(n-1)+b3y(n-2)

=x(n)-2x(n-1)+x(n-2)-1.998 89y(n-1)

+0.998 89y(n-2)(2)

依據(jù)式(2)和上述分析,這一濾波器在硬件實(shí)現(xiàn)上可簡(jiǎn)化為兩個(gè)24位乘法器以及數(shù)據(jù)的移位、求和操作。

1.4 多路時(shí)分復(fù)用分析

提供多通道可擴(kuò)展支持有兩種方式:(1)在資源限制小的情況下,綜合考慮所需要的濾波器的最大工作頻率以及所需要的通道數(shù),利用FPGA資源的豐富性對(duì)單一濾波器結(jié)構(gòu)進(jìn)行邏輯復(fù)用從而實(shí)現(xiàn)并行方式的多路擴(kuò)展;(2)在所需要的濾波器的工作能力要求不高的情況下,根據(jù)所需要的通道數(shù),通過時(shí)分復(fù)用的方式使用單一的邏輯資源實(shí)現(xiàn)多路通道的擴(kuò)展方案減少資源消耗。由于音頻信號(hào)傳輸?shù)乃俾释桓撸褂脮r(shí)分復(fù)用單一邏輯的方式會(huì)比使用邏輯復(fù)用的方式更為經(jīng)濟(jì),本文基于這一目標(biāo)設(shè)計(jì)實(shí)現(xiàn)一個(gè)4通道的二階IIR濾波器,更多通道的情況將采取類似的思路進(jìn)行擴(kuò)展。

常用的音頻數(shù)據(jù)格式中一次采樣的音頻信號(hào)占32位,如I2S數(shù)據(jù)格式中一次采樣中有24位有效數(shù)據(jù)而另外8位恒定為0,相當(dāng)于一次采樣保有32個(gè)時(shí)鐘周期的可利用時(shí)間。在4路數(shù)據(jù)并行情況下,每一路數(shù)據(jù)計(jì)算及緩存值的更新共同所需的時(shí)鐘周期數(shù)為Tqt≤32/4=8,也即設(shè)計(jì)的濾波器操作周期最大不能大于8。從式(2)發(fā)現(xiàn)每一路信號(hào)都需要保存4個(gè)中間結(jié)果:x(n-1),x(n-2),y(n-1),y(n-2)。由于這些中間結(jié)果之間有強(qiáng)烈的數(shù)據(jù)延遲依賴關(guān)系,即x(n-1)、x(n-2)分別為在第n次計(jì)算時(shí)第n-1次及第n-2次的數(shù)據(jù)輸入值,y(n-1)、y(n-2)分別為第n-1次的數(shù)據(jù)輸出值以及第n-2次的數(shù)據(jù)輸出值,在時(shí)分復(fù)用操作過程中可以利用這一延遲關(guān)系節(jié)省時(shí)間。

2 IIR濾波器硬件電路實(shí)現(xiàn)

2.1 濾波計(jì)算控制狀態(tài)機(jī)

前面已經(jīng)給出濾波器每一次的計(jì)算周期數(shù)不能高于8,在這不多于8個(gè)周期內(nèi)要能夠穩(wěn)定處理中間數(shù)據(jù)的保存和刷新工作采用狀態(tài)機(jī)實(shí)現(xiàn)。觀察式(2)在采用的設(shè)計(jì)方法情況下,其計(jì)算過程的第n次輸入的數(shù)據(jù)x(n)僅需要進(jìn)行移位和加減操作;y(n-1)和y(n-2)需要使用乘法單元。這一部分的計(jì)算利用延遲特性可以從上一路計(jì)算結(jié)束時(shí)開始,進(jìn)而形成流水線提升整個(gè)計(jì)算效率。

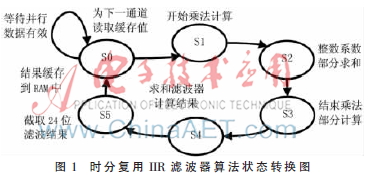

設(shè)計(jì)中采用的算法狀態(tài)轉(zhuǎn)換圖如圖1。其中所示的每一個(gè)狀態(tài)均占用一個(gè)周期,正好能滿足只要有數(shù)據(jù)輸入整個(gè)計(jì)算過程為8個(gè)周期。為了合理地利用延遲,從S0狀態(tài)時(shí)即可對(duì)RAM中的數(shù)據(jù)進(jìn)行預(yù)讀,這樣在讀入數(shù)據(jù)后的下一個(gè)周期,乘法器單元能自動(dòng)地進(jìn)行乘法計(jì)算,同時(shí)在S3狀態(tài)時(shí)得到乘法的輸出結(jié)果;乘法器采用3級(jí)流水線結(jié)構(gòu)剛好和這一計(jì)算過程匹配,充分利用數(shù)據(jù)的延遲特性,并且能極大地提高該設(shè)計(jì)的計(jì)算能力,對(duì)于后續(xù)的擴(kuò)展有著關(guān)鍵意義。對(duì)于系數(shù)部分的移位和求和過程,則在S1和S2狀態(tài)分別執(zhí)行以節(jié)省時(shí)間。

2.2 多路復(fù)用濾波器結(jié)構(gòu)

設(shè)計(jì)采用的濾波器結(jié)構(gòu)如圖2所示。寬度為24的4路待處理數(shù)據(jù)從外部輸入后,首先將24位的待計(jì)算值送入常系數(shù)運(yùn)算處理單元[11],這一運(yùn)算中,首先對(duì)于a1、a2、a3系數(shù)左移L位,然后求和a1、a2所對(duì)應(yīng)部分的結(jié)果sum1,再將sum1與a3移位后所對(duì)應(yīng)的部分求和得到常系數(shù)運(yùn)算處理單元計(jì)算結(jié)果。在進(jìn)行移位操作的同時(shí)從RAM表中取出參與該次計(jì)算的y(n-1)、y(n-2),并分別在相應(yīng)乘法單元中進(jìn)行運(yùn)算,得到乘法計(jì)算的部分和,隨后將各乘法單元以及常系數(shù)運(yùn)算處理單元的運(yùn)算結(jié)果輸入求和單元進(jìn)行運(yùn)算,并根據(jù)參數(shù)的擴(kuò)展量2L截取求和單元輸出的[L+23:L]作為最終輸出,這一部分的值還將作為下次計(jì)算的y(n-1)存入RAM數(shù)據(jù)保存區(qū)中。為了實(shí)現(xiàn)更多的多路擴(kuò)展,在采用類似機(jī)制的同時(shí),需要對(duì)于RAM數(shù)據(jù)保存區(qū)的存儲(chǔ)單元大小進(jìn)行適當(dāng)調(diào)整,以使得容量足夠處理相應(yīng)多路條件下的中間數(shù)據(jù)。

2.3 目標(biāo)濾波器資源占用情況

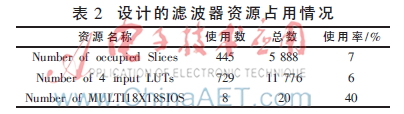

目標(biāo)濾波器選用的器件為Xilinx公司的Spartan 3AN XC3S700A一款非DSP強(qiáng)化型FPGA。目標(biāo)濾波器對(duì)應(yīng)的主要資源消耗情況如表2所示,可見所消耗的資源數(shù)非常低。乘法器的消耗主要是采用24位乘24位的乘法器IP核來處理音頻信號(hào)。目標(biāo)濾波器在該器件上可達(dá)到的最大工作頻率為129.121 MHz,遠(yuǎn)遠(yuǎn)高于實(shí)際使用的時(shí)鐘頻率,說明這一邏輯可以適用于時(shí)鐘頻率更高或同時(shí)滿足更多通路的時(shí)分復(fù)用操作的環(huán)境中。

3 仿真測(cè)試與討論

本文采用Matlab SE 10.1a與ISE Design Suite 14.7聯(lián)合仿真來測(cè)試所設(shè)計(jì)的IIR濾波器。在測(cè)試流程中將比對(duì)Matlab軟件計(jì)算結(jié)果和硬件計(jì)算結(jié)果,從而判斷硬件實(shí)現(xiàn)的成效。仿真測(cè)試中,采用一個(gè)1.5 kHz幅值為1的正弦波信號(hào)疊加上一個(gè)3 Hz幅值為3的正弦波信號(hào)作為低頻噪聲。先使用Matlab產(chǎn)生這一激勵(lì)信號(hào)形成文件然后在測(cè)試中讀取這一文件。為了驗(yàn)證該硬件濾波器的性能,將Xilinx與Matlab數(shù)據(jù)聯(lián)合仿真的輸出結(jié)果通過Matlab繪制成頻譜圖如圖3所示,同時(shí)利用modelsim將測(cè)試的多路濾波的結(jié)果顯示如圖4所示。

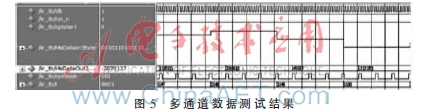

圖3所示為信號(hào)處理前的頻譜圖,由于仿真中使用的噪聲信號(hào)頻率很低,中頻部分幾乎沒有信號(hào),所以將處理前的頻譜分為0~15 Hz,1 000 Hz~2 000 Hz顯示;圖4為處理后的頻譜。對(duì)比圖3與圖4可見對(duì)于3 Hz的噪聲信號(hào)通過設(shè)計(jì)的濾波器后,幅值減為原來的一半,實(shí)現(xiàn)了-3 dB的衰減。圖5顯示每一個(gè)數(shù)據(jù)均能保持4次計(jì)算結(jié)束信號(hào)周期的時(shí)長(zhǎng)說明了該濾波器具有多通道時(shí)分復(fù)用的功能。

4 小結(jié)

本文根據(jù)實(shí)際的音頻信號(hào)處理工程需求,設(shè)計(jì)了一款基于時(shí)分復(fù)用方式實(shí)現(xiàn)4通道語音信號(hào)濾波的二階IIR濾波器。通過Matlab和modelsim的聯(lián)合仿真,讀取輸出數(shù)據(jù)導(dǎo)入Matlab并通過繪制出對(duì)應(yīng)頻譜,驗(yàn)證了該濾波器的幅度頻率特性滿足設(shè)計(jì)目標(biāo)要求。

在設(shè)計(jì)中將傳輸函數(shù)的系數(shù)轉(zhuǎn)換為整數(shù),從而將乘法計(jì)算轉(zhuǎn)化為簡(jiǎn)單的移位操作節(jié)約FPGA專有乘法器單元,這一優(yōu)化形式可以方便地拓展到其他應(yīng)用中。

文章提出了兩種通道擴(kuò)展的方式。本設(shè)計(jì)目標(biāo)濾波器依據(jù)所處理的音頻信號(hào)特點(diǎn)采用了其中的時(shí)分復(fù)用方式。此外,因?yàn)槎A濾波器是高階濾波器的基本單元,高階濾波器可以通過二階濾波器以級(jí)聯(lián)方式來實(shí)現(xiàn)[12],所以本文所設(shè)計(jì)的IIR濾波器對(duì)于實(shí)現(xiàn)更復(fù)雜語音信號(hào)處理所需的高階IIR濾波器有一定的參考意義。

參考文獻(xiàn)

[1] 周利清,蘇菲.數(shù)字信號(hào)處理基礎(chǔ)(第二版)[M].北京:北京郵電大學(xué)出版社,2007.

[2] 趙力.語音信號(hào)處理(第二版)[M].北京:機(jī)械工業(yè)出版社,2011.

[3] 謝海霞,孫志雄.IIR濾波器的DSP實(shí)現(xiàn)[J].電子器件,2013,36(2):194-196.

[4] 崔景安,徐寧.實(shí)時(shí)音頻信號(hào)采集系統(tǒng)中的數(shù)字濾波器的設(shè)計(jì)及實(shí)現(xiàn)[J].內(nèi)蒙古大學(xué)學(xué)報(bào)(自然科學(xué)版),2014,41(3):336-339.

[5] 欒軍山,陳華.實(shí)時(shí)音頻處理系統(tǒng)中的IIR濾波器設(shè)計(jì)及Lattice結(jié)構(gòu)實(shí)現(xiàn)[J].制造業(yè)自動(dòng)化,2011,33(5):97-100.

[6] 邸麗霞,張彥軍,劉怡文.基于SOPC的高速IIR濾波算法的實(shí)現(xiàn)[J].科學(xué)技術(shù)與工程,2013,13(33):9978-9982.

[7] 秦宏伍,史浩,崔·尤里·謝爾蓋維奇.基于FPGA的IIR濾波器整數(shù)設(shè)計(jì)[J].微計(jì)算機(jī)信息,2007,23(122).

[8] MEYER-BEASE.Digital signal processing with field programmable gate arrays[M].Springer,2007.

[9] 劉彬.MATLAB環(huán)境下IIR濾波器設(shè)計(jì),仿真與驗(yàn)證[J].電子測(cè)量技術(shù),2011,34(4):7-10.

[10] 薛定宇,張曉華.控制系統(tǒng)與計(jì)算機(jī)輔助設(shè)計(jì)——MATLAB語言與應(yīng)用(第二版)[M].北京:清華大學(xué)出版社,2000.

[11] 張大為,姜靜,劉迪.基于FPGA的IIR低通數(shù)字濾波器的設(shè)計(jì)[J].船電技術(shù),2012(2).

[12] 王衛(wèi)兵.高階IIR數(shù)字濾波器的FPGA描述[J].現(xiàn)代電子技術(shù),2005,207(16):3-4.