電源完整性 (PI) 是電子行業(yè)中廣泛使用的一個術語,可分析系統(tǒng)內(nèi)部電源從源端向負載轉(zhuǎn)換和傳輸?shù)男省kS著數(shù)字信號速率的不斷提升,特別是提升到 10Gbps 以上數(shù)量級后,電源完整性的測量成為關鍵測試項目之一。

測量內(nèi)容

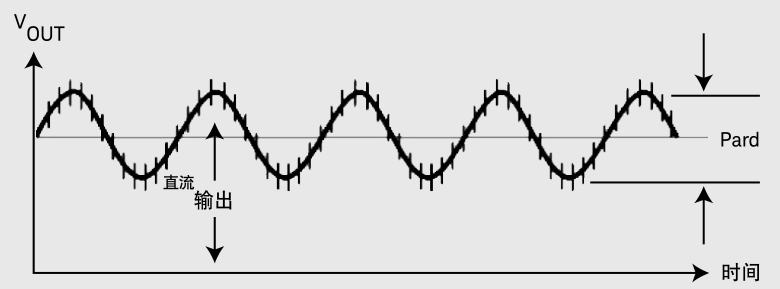

PARD — 周期和隨機偏差,描述了在其他所有參數(shù)均為常數(shù)時直流輸出與直流平均值的偏差,用來衡量直流輸出經(jīng)過電壓調(diào)整和濾波電路之后所殘留的多余的交流和噪聲分量。

負載響應 —指一個靜態(tài)或瞬態(tài)負載,根據(jù)預先確定的負載可以衡量電源維持在指定輸出電壓范圍內(nèi)的能力。通常要測量電源在基于負載的預定義建立頻段內(nèi)的瞬態(tài)恢復時間。

噪聲 — 直流電源與標稱值的偏差。包括隨機噪聲 ( 如熱噪聲 )、雜散信號 ( 例如相鄰電路或 PARD 和負載響應中的開關耦合 )。

時域分析

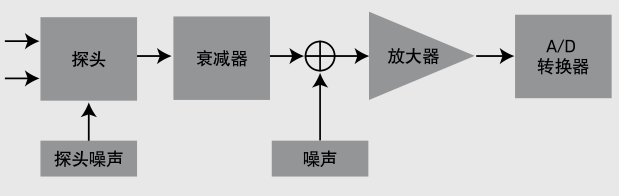

實時示波器是用來進行電源噪聲測量的常用工具,但是不能忽略的是,實時寬帶數(shù)字示波器以及其探頭都有其固有的噪聲。

對于電源紋波噪聲的測試,通常需要注意以下幾點:

盡量不使用 8bits 示波器

盡量使用專用的電源測試探頭

盡量使用小衰減比的探頭

盡量使用示波器最小量程以降低示波器本底噪聲;

探頭的接地線盡量短,構(gòu)成的環(huán)路面積盡可能小

根據(jù)需要使用帶寬限制功能,低通濾波器和高通濾波器,甚至帶通濾波器。

頻域分析

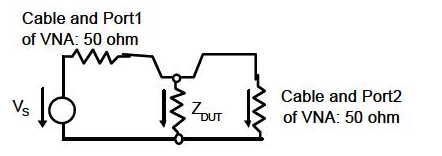

電源完整性分析對象主要是電源分配網(wǎng)絡 PDN(Power Distribution Network)。要衡量 PDN 性能,只用示波器測試 CPU 和 IC 管腳的電源紋波和噪聲是不夠的,要用到網(wǎng)絡分析儀。

用網(wǎng)絡分析儀去測試 PDN,有兩大挑戰(zhàn):

1、PDN 的輸出阻抗和傳輸阻抗是毫歐級的,想準確測試,是一件比較困難的事情。

2、PDN 工作時是帶直流電壓的,即帶偏置的,需要網(wǎng)絡分析儀有偏置測量的功能。

測量技巧

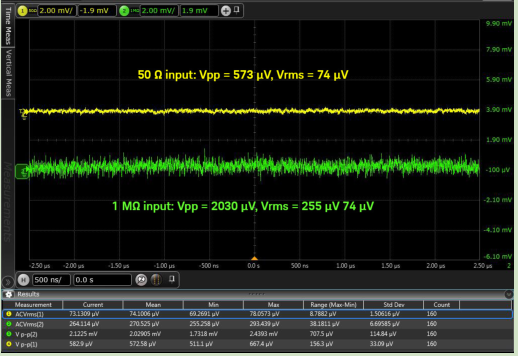

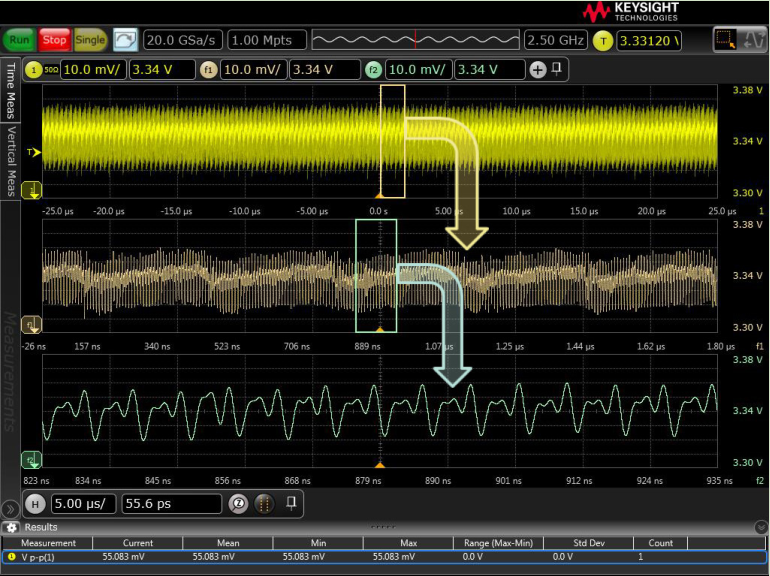

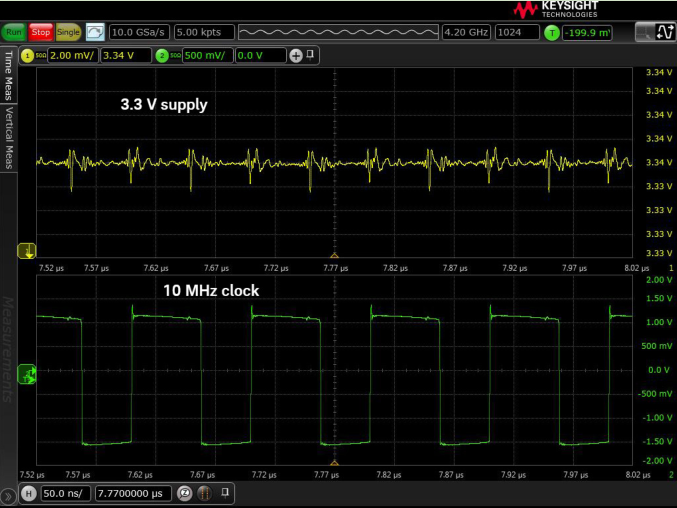

1. 選擇噪聲最低的示波器測量路徑(圖4)

2. 通過限制帶寬來減少測量系統(tǒng)噪聲(圖5)

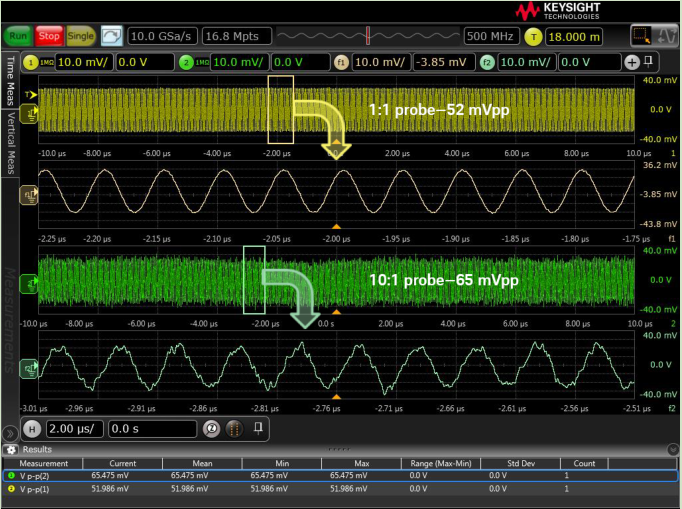

3. 使用 1:1 衰減器來減少測量系統(tǒng)噪聲(圖6)

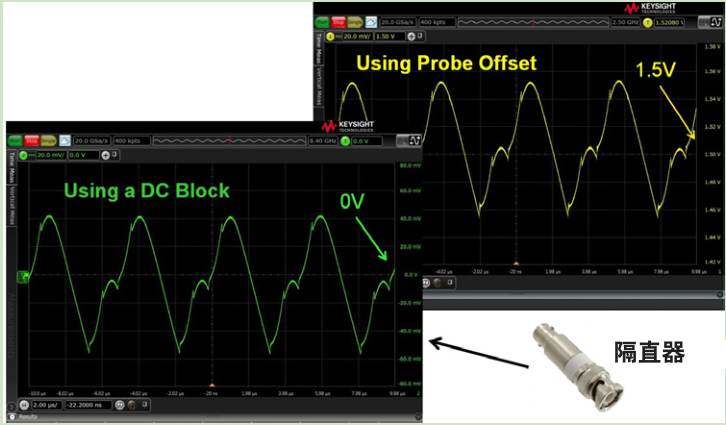

4. 使用探頭偏置來提高動態(tài)范圍(圖7)

5. 正確地使用隔直器(圖8)

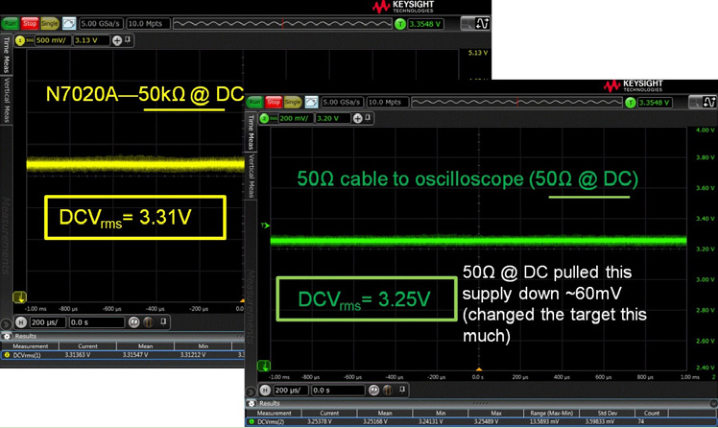

6. 盡量減少電源加載示波器和探頭的需要(圖9)

7. 使用 FFT 進行深入分析(圖10)

8. 觸發(fā)可疑的干擾源,并使用平均值法減少無關噪聲(圖11)

9. 使用足夠的帶寬來捕獲令人困擾的瞬態(tài)和噪聲(圖12)

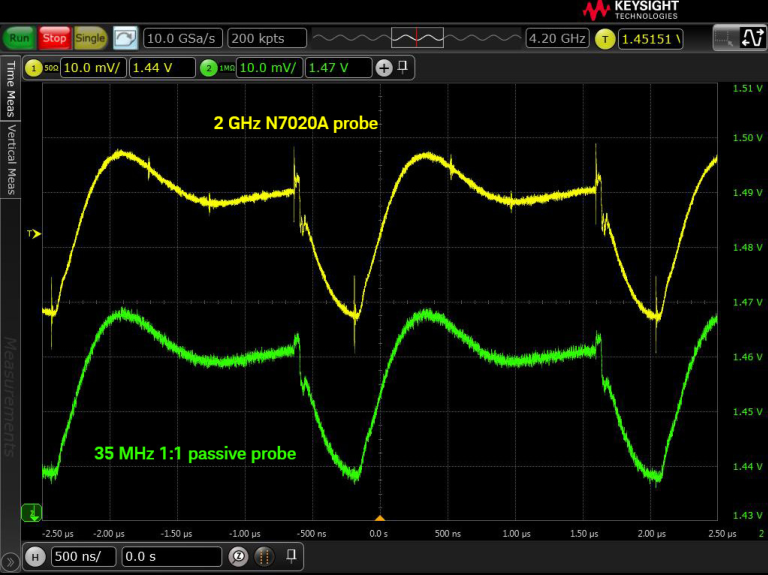

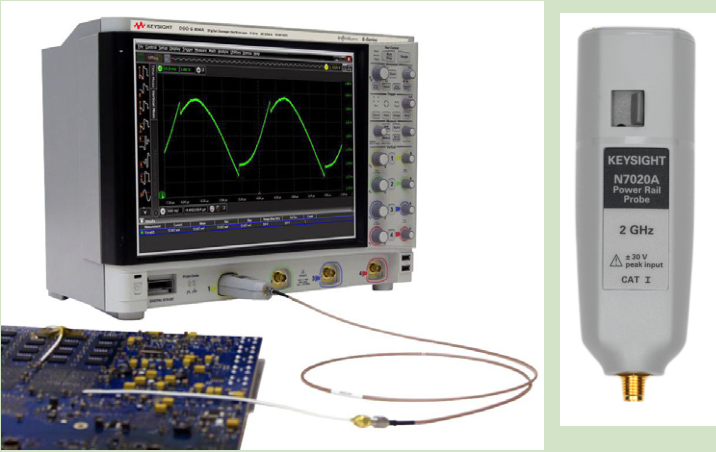

10. 充分利用專為電源噪聲測量而設計的電源探頭(圖13)

然而,掌握了上述技巧,并不意味著你就能解決電源完整性測量這一高速數(shù)字電路領域的大難題。如何快速而準確地搭建電源完整性測量系統(tǒng)?如何恰當?shù)剡x擇測量工具和儀器來完成電源完整性的測量?如何保證測量結(jié)果的精準而有效?1月7日西安,1月12日武漢,1月14日南京,是德科技為您揭曉!