文獻(xiàn)標(biāo)識碼: A

DOI:10.16157/j.issn.0258-7998.2016.08.003

中文引用格式: 戈喆,王志鴻,厲媛玥. 基于Innovus的低功耗物理設(shè)計[J].電子技術(shù)應(yīng)用,2016,42(8):21-24.

英文引用格式: Ge Zhe,Wang Zhihong,Li Yuanyue. Low power physical design in Innovus[J].Application of Electronic Technique,2016,42(8):21-24.

0 引言

高性能與低功耗是當(dāng)今芯片設(shè)計的兩個主要方向。對于便攜式設(shè)備大力發(fā)展的今天、物聯(lián)網(wǎng)應(yīng)用呼之欲出的明天,低功耗芯片的需求空前高漲,同時也對低功耗芯片的設(shè)計提出了更高要求。為了達(dá)到更低的功耗,越來越多的低功耗技術(shù)被應(yīng)用到芯片中,比如電源關(guān)斷技術(shù)(Power Shut Off,PSO)[1]、多電壓域供電(Multi Supply Power,MSV)、多電壓與時鐘模式、動態(tài)電壓頻率調(diào)節(jié)技術(shù)(Dynamic Voltage Frequency Scale,DVFS)、存儲器分割(Memory Split)、門控時鐘(Clock Gating)[2]、門控數(shù)據(jù)線[3]、多閾值電壓設(shè)計(Multi-Vt)[4]、襯底偏壓調(diào)制技術(shù)(Back Bias)等。這些方法從芯片設(shè)計的各個層面實現(xiàn)低功耗,芯片物理設(shè)計是其中的重要一環(huán)。本文基于新一代布局布線工具Innovus,在傳統(tǒng)低功耗物理設(shè)計流程的基礎(chǔ)上,研究了新的低功耗物理設(shè)計方法。

1 低功耗物理設(shè)計

芯片物理設(shè)計是指將芯片電路和代碼轉(zhuǎn)變?yōu)樾酒鎴D的過程,布局布線是芯片物理設(shè)計的核心,本文主要討論低功耗布局布線技術(shù)。

低功耗物理設(shè)計內(nèi)容可以分為兩類,一類是對前端各種低功耗設(shè)計進(jìn)行物理實現(xiàn),比如在物理上對多電壓域進(jìn)行劃分和布局;片上電源管理模塊和電源開關(guān)的放置和連線;通過CPF(Common Power File)控制電平轉(zhuǎn)換邏輯(Level Shifter)和隔離邏輯(Isolation Cell)的加入、電源連接、擺放和優(yōu)化;時鐘門控邏輯的擺放與優(yōu)化;掉電狀態(tài)保持寄存器(State Retention Power Gate,SRPG)電源線和單元行的布置等。另一類是在芯片物理層面(如版圖、標(biāo)準(zhǔn)單元甚至是器件級別)實現(xiàn)的低功耗設(shè)計,這類方法只能在芯片后端設(shè)計時實現(xiàn),比如多閾值電壓標(biāo)準(zhǔn)單元庫選用,襯底偏壓調(diào)制技術(shù),低功耗時鐘樹技術(shù)等。

低功耗物理設(shè)計的核心是與前端設(shè)計相配合,減少芯片內(nèi)一切不必要的翻轉(zhuǎn)和電容充放電,減少乃至關(guān)斷芯片內(nèi)不工作模塊的漏電,減少一切時序路徑上的性能冗余,以及提供多樣化的工作模式以避免在不同應(yīng)用場合的功耗浪費。精巧的低功耗物理設(shè)計能夠在保證芯片性能的基礎(chǔ)上,有效改善芯片功耗。

2 基于Innovus的改進(jìn)低功耗物理設(shè)計

Innovus是Cadence公司的新一代布局布線工具,不僅加強了先進(jìn)工藝和高性能芯片的設(shè)計能力,也為低功耗芯片設(shè)計提供了強大的功能。本文基于Innovus,為90 nm低功耗ARM核微控制器設(shè)計了新的低功耗布局布線流程,最終功耗改善超過15%。

2.1 低功耗標(biāo)準(zhǔn)單元庫設(shè)計

好的芯片物理設(shè)計離不開一套與需求相匹配的標(biāo)準(zhǔn)單元庫,所以低功耗物理設(shè)計也需要一套低功耗標(biāo)準(zhǔn)單元庫。

2.1.1 多閾值電壓單元

這是最普遍、也是最有效的方法,通過不同閾值電壓單元的搭配,達(dá)到芯片性能與功耗的平衡[4]。

2.1.2 加長溝道單元與選擇性加長溝道單元

加長溝道單元(Gate Length Bias,GLB),又稱低漏電單元[5-6]。在數(shù)字標(biāo)準(zhǔn)單元電路設(shè)計中,通常晶體管的溝長都會選擇最小特征尺寸,以獲得最好的性能。但是在加長溝道單元中,所有晶體管的溝長都被加長,比如增加20%最小溝長,這是因為隨著半導(dǎo)體工藝越來越先進(jìn),晶體管漏電流所帶來的功耗比例越來越大,通過提高器件溝長,可以有效抑制器件短溝效應(yīng)和漏致感應(yīng)勢壘降低效應(yīng)(DIBL),從而減小器件漏電。加長溝道單元通常應(yīng)用在非關(guān)鍵時序路徑上,通過去除芯片中的冗余性能降低芯片功耗,這和多閾值電壓單元是一樣的道理。

但是,加長溝道單元有一個問題,它會提高芯片動態(tài)功耗。因為溝道加長以后,柵面積就會增加,相應(yīng)的柵電容充放電就會增加,從而增加動態(tài)功耗。為了應(yīng)對這個問題,新的標(biāo)準(zhǔn)單元庫引入選擇性加長溝道單元(Selective GLB)。選擇性加長溝道單元通過有選擇地對單元內(nèi)關(guān)鍵漏電晶體管進(jìn)行溝道加長,在有效減少漏電的同時將單元動態(tài)功耗和性能的損失降到最低。例如,在選擇性加長溝道寄存器中,所有與時鐘相關(guān)的晶體管都不能加長溝道以避免動態(tài)功耗大量增加,而所有在寄存器掉電狀態(tài)下進(jìn)行狀態(tài)保持的晶體管都建議增加溝長,以減小芯片低漏電模式下的漏電功耗。

2.1.3 多位寄存器

通過將多個(2、4個居多)關(guān)聯(lián)性高的寄存器合并成一個多位寄存器(Multi-bit Flip Flop),可以有效共享每個寄存器內(nèi)的類同邏輯器件,減少寄存器時鐘端口相關(guān)聯(lián)電容,同時更少的寄存器數(shù)量也有助于實現(xiàn)更優(yōu)的時鐘樹設(shè)計[7]。

2.1.4 多尺寸梯度單元和極小尺寸單元

引入更多尺寸的標(biāo)準(zhǔn)單元能夠為工具提供更多選擇,有利于減少芯片在修復(fù)時序和轉(zhuǎn)換時間違例時的過量優(yōu)化。而極小尺寸單元也提供了在某些場合進(jìn)一步減少功耗的可能。

2.1.5 延時單元和保持時序改善寄存器

延時單元(Delay Cell)可以提供大延時,專用于修復(fù)保持時序違例。但原有庫中某些延時單元提供大延時的效率并不理想,新庫對此進(jìn)行了改進(jìn)設(shè)計。

新庫通過設(shè)計特別的掃描路徑保持時序改善寄存器,減少系統(tǒng)保持時序違例,同時不影響系統(tǒng)功能路徑時序,改善芯片功耗[8]。

2.2 低功耗布局與優(yōu)化

一個好的布局和優(yōu)化不僅需要考慮系統(tǒng)時序和布線擁擠程度,也需要考慮整個系統(tǒng)的功耗水平。在布局和優(yōu)化階段,標(biāo)準(zhǔn)單元的選取、物理擺放、等價邏輯轉(zhuǎn)換、非關(guān)鍵路徑功耗優(yōu)化以及系統(tǒng)的總加權(quán)繞線長度等因素都與系統(tǒng)的功耗息息相關(guān),如何在保證系統(tǒng)性能和繞線的基礎(chǔ)上降低功耗是低功耗設(shè)計的關(guān)鍵。在這方面,Innovus的GigaPlace和GigaOpt引擎為設(shè)計者提供了強有力的支持。通過Innovus的功耗驅(qū)動(power-driven)布局和功耗驅(qū)動優(yōu)化,可以有效開展三維驅(qū)動設(shè)計。

2.2.1 布局與優(yōu)化方法分析

為了達(dá)到最優(yōu)效果,本文對Innovus進(jìn)行了多項測試,結(jié)果如表1。

從表1中可以看到,Innovus通過新的功耗驅(qū)動引擎,在沒有任何功耗優(yōu)化的設(shè)置下,可改善總功耗3%。當(dāng)引入更多的功耗優(yōu)化選項后,功耗最大可改善近5%。設(shè)計者可以根據(jù)芯片的應(yīng)用需要,對動態(tài)功耗和靜態(tài)功耗的優(yōu)化比例進(jìn)行選擇,工具可以根據(jù)選擇做出優(yōu)化策略的改變。另外,Innovus可以在布局階段考慮時鐘樹特殊布線的需求(ndrAwareOpt),從而與時鐘樹之后的設(shè)計更加匹配。本文也注意到,Innovus提供的“有用偏時”選項(usefulSkew)結(jié)果并不理想(本文也追蹤比較了時鐘樹之后的結(jié)果),需要進(jìn)一步調(diào)試。

表1顯示,當(dāng)靜態(tài)優(yōu)化程度(leakage power effort)很高時,功耗整體優(yōu)化結(jié)果并不好。這其中的一個原因是90 nm工藝靜態(tài)功耗所占比例太低,另一個原因就是我們采用了加長溝道單元。加長溝道單元在大大降低器件漏電的同時,也會顯著提高器件的動態(tài)功耗。工具如果不能很好地從全局進(jìn)行分辨取舍,就會影響功耗優(yōu)化效率。所以本文給出的建議是,禁止在布局和優(yōu)化階段使用加長溝道單元,引導(dǎo)工具更多地通過高閾值電壓單元和小尺寸單元優(yōu)化靜態(tài)功耗。加長溝道單元可以在時鐘樹后有選擇的進(jìn)行使用。

2.2.2 輸入向量驅(qū)動功耗優(yōu)化

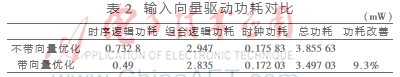

動態(tài)功耗的產(chǎn)生與芯片的運行狀態(tài)息息相關(guān),默認(rèn)情況下,工具使用默認(rèn)的翻轉(zhuǎn)率來進(jìn)行動態(tài)功耗的估算,這會與實際情況有很大偏差,在這種情況下進(jìn)行動態(tài)功耗優(yōu)化,勢必影響功耗優(yōu)化效率。Innovus支持輸入向量驅(qū)動(VCD driven)優(yōu)化,本文測試結(jié)果如表2。

表2顯示,工具在有特定輸入向量驅(qū)動的情況下,可針對此輸入模式進(jìn)行精準(zhǔn)動態(tài)功耗優(yōu)化(vector based optimization),從而有效改善(9.3%)此工作模式下的動態(tài)功耗優(yōu)化效果。所以本文建議在進(jìn)行芯片物理設(shè)計時,可以加入典型芯片工作模式輸入向量,幫助工具更好地優(yōu)化芯片功耗。

2.3 低功耗時鐘樹設(shè)計

時鐘樹綜合是低功耗物理設(shè)計的重要內(nèi)容,因為即使廣泛采用門控時鐘,芯片時鐘系統(tǒng)還是占據(jù)了整個芯片數(shù)字邏輯約40%的功耗比重。通常低功耗時鐘樹的設(shè)計方法有:

(1)分析時鐘樹結(jié)構(gòu),設(shè)計合理時鐘樹綜合方案。

(2)設(shè)置合理的時鐘偏斜(clock skew)和轉(zhuǎn)換時間(transition)要求。

(3)嘗試不同緩沖器或倒相器時鐘樹方案,一般避免使用大尺寸(功耗大)和小尺寸(片上偏差OCV大)單元。使用低閾值單元進(jìn)行時鐘樹綜合。

(4)在片上偏差可接受范圍內(nèi),推薦多使用小尺寸門控時鐘單元。門控時鐘單元盡量靠近其驅(qū)動單元放置。

(5)使用電阻電容小的金屬層進(jìn)行時鐘樹布線,使用多孔(multi-cut)布線。

(6)盡可能多地使用時鐘樹特殊布線,可有效減小時鐘樹電阻和耦合電容。

(7)使用多位寄存器。

現(xiàn)在低功耗時鐘樹的主流趨勢是時鐘樹綜合并不需要以“零時鐘偏斜”為目標(biāo)。因為為了減小時鐘偏斜,時鐘樹上往往需要引入大量邏輯進(jìn)行平衡,但很多時候這是沒有必要的,特別對于性能要求并不高的微控制器來說。允許時鐘偏差,對數(shù)據(jù)路徑和時鐘路徑協(xié)同優(yōu)化,避免引入不必要時鐘樹邏輯,在滿足時序要求的同時減少功耗,這就是時鐘樹協(xié)同優(yōu)化(CCOPT)的低功耗時鐘樹設(shè)計方法。

Innovus使用新一代CCOPT引擎,幫助設(shè)計者進(jìn)行良好的時鐘樹協(xié)同優(yōu)化設(shè)計。本文對兩塊芯片分別進(jìn)行測試,結(jié)果分別如表3和表4。

由表3和表4可知,通過時鐘樹協(xié)同優(yōu)化,可大大減少時鐘樹上的邏輯數(shù)量,從而有效減小時鐘功耗。雖然在后續(xù)時序優(yōu)化中,數(shù)據(jù)路徑上引入的邏輯數(shù)量會有所增加,但由于數(shù)據(jù)路徑的翻轉(zhuǎn)頻率大大低于時鐘路徑,所以并不會對整體功耗產(chǎn)生太大影響。

2.4 時鐘樹后低功耗設(shè)計

時鐘樹綜合后,芯片設(shè)計主要通過邏輯單元替換減少功耗。由于時鐘樹后芯片的時序計算越來越準(zhǔn)確,這時可以通過減小邏輯單元尺寸、替換高閾值單元、替換加長溝道單元等方法進(jìn)一步將非關(guān)鍵路徑上的冗余性能轉(zhuǎn)換為功耗節(jié)省。

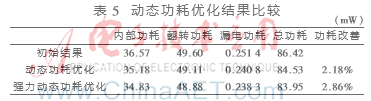

設(shè)計者可以通過Innovus的動態(tài)功耗優(yōu)化命令(optDynamicPower)進(jìn)行單元替換,在滿足時序的前提下優(yōu)化功耗,通過測試(表5)可以看到這能夠帶來2~3%的功耗改善。這一過程同樣支持輸入向量驅(qū)動,并能達(dá)到更優(yōu)效果。

在繞線與繞線后優(yōu)化階段,Innovus的功耗優(yōu)化能力同樣得到改善,經(jīng)測試與上一代工具相比,功耗減少1.4%。如果在繞線后進(jìn)一步打開“面積優(yōu)化”(area reclaim)選項,功耗能夠進(jìn)一步改善4.6%。

在這個階段,設(shè)計者可以考慮替換更多加長溝道單元進(jìn)入芯片以有針對性地改善芯片靜態(tài)漏電。通常而言,靜態(tài)節(jié)點和準(zhǔn)靜態(tài)節(jié)點可以放心使用加長溝道單元,低翻轉(zhuǎn)率節(jié)點也可以考慮使用加長溝道單元,高翻轉(zhuǎn)率節(jié)點不能引入加長溝道單元,低漏電模式下不掉電的單元應(yīng)考慮加長溝道(典型的如SRPG中的常開鎖存器)。

對于芯片中數(shù)量巨大的保持時序違例,設(shè)計者可以通過優(yōu)化延時單元與緩沖器使用組合的方法來減少使用數(shù)量,降低功耗。

最后在時序違例基本干凈以后,能夠通過PBA(Path Based Analysis)方法進(jìn)一步去除時序路徑上的性能冗余,減少不必要的功耗。這個步驟通常在靜態(tài)時序分析(STA)工具中進(jìn)行,比如Cadence的Tempus。

3 結(jié)論

本文借助于Cadence新一代布局布線工具Innovus,對傳統(tǒng)低功耗物理設(shè)計流程進(jìn)行了全面優(yōu)化。內(nèi)容包含低功耗標(biāo)準(zhǔn)單元庫設(shè)計,低功耗布局和優(yōu)化設(shè)計,低功耗時鐘樹設(shè)計和時鐘樹后低功耗設(shè)計。通過新的工具和方法,芯片數(shù)字部分功耗可改善15%,效果顯著。

參考文獻(xiàn)

[1] HUANG P,XING Z C,WANG T R,et al.A brief survey on power gating design[C].Solid-State and Integrated Circuit Technology(ICSICT),2010:788-790.

[2] ZHANG Y L,TONG Q,LI L,et al.Automatic register transfer level CAD tool design for advanced clock gating and low power schemes[C].SoC Design Conference (ISOCC),2012 International:21-24.

[3] GE Z,ZHANG J L,TAN M L.Module-based bus gating methodology in low power SoC design[C].27th IEEEInternational SOCC,Design Track Digest,2014:4-5.

[4] RAO S M,BHATNAGAR H.Power reduction technique using multi-vt libraries[C].System-on-Chip for Real-Time Applications,Proceedings.Fifth International Workshop,2005:363-367.

[5] GUPTA P,KAHNG A B,SHARRMA P,et al.Gate-length biasing for runtime-leakage control[J].IEEE Trans.Computer-aided design of integrated circuits and sysntems,2006,25(8):1475-1485.

[6] HU J P,WANG J.Standard cell design of a low-leakage flip-flop with gate-length biasing[C].ASIC(ASICON),2011IEEE 9th International Conference,:361-364.

[7] SANTOS C,REIS R,GODOI G,et al.Multi-bit flip-flop usage impact on physical synthesis[C].Integrated Circuits and Systems Design(SBCCI),2012 25th Symposium,pp.1-6.

[8] GE Z,TAN M L.Scan-hold-timing-friendly flip-flop to improve chip routing and power[C].IEEE International SOCC 2015,Design Track Digest,Sep 2015:78-79.