文獻標識碼: A

文章編號: 0258-7998(2014)03-0041-04

中文引用格式:楊洪敏,王祖強,徐輝.AVS編碼器中變換量化和掃描的FPGA設(shè)計[J].電子技術(shù)應(yīng)用,2014,40(03):41-44.

AVS(Audio Video coding Standard)標準是由我國獨立制定的具有自主知識產(chǎn)權(quán)的視頻編碼標準[1],采用了與H.264類似的技術(shù)框架[2],,但其編碼效率比國際標準MPEG-2高2~3倍,,與H.264相當(dāng),但存儲要求和算法復(fù)雜度比H.264低,,更便于硬件實現(xiàn)[3],。

變換、量化和掃描在AVS視頻編碼過程中占有很重要的地位,,它是AVS編碼中數(shù)據(jù)處理的中間部分,,即將殘差數(shù)據(jù)經(jīng)過變換、量化和掃描后傳到熵編碼部分,,所以算法的優(yōu)劣和實現(xiàn)架構(gòu)對AVS視頻編碼器的性能有很大的影響,。本文為了提高AVS視頻編碼器的處理速度,結(jié)合了國內(nèi)外學(xué)者的設(shè)計思想提出了一種變換,、量化與掃描模塊結(jié)構(gòu),,在消耗邏輯資源允許的情況下提高了處理速度,達到了速度和面積的平衡,。

本文以實現(xiàn)1 080i,、30 f/s格式視頻實時高清編碼為目標,結(jié)合AVS標準中變換,、量化和掃描的特點,,設(shè)計了一種高速并行流水線結(jié)構(gòu)。通過對整數(shù)變換模塊內(nèi)部結(jié)構(gòu)的優(yōu)化和一維整數(shù)變換模塊的復(fù)用,,節(jié)省了硬件資源,。量化和一維變換模塊內(nèi)部均采用3級流水線處理。掃描模塊采用從首尾兩端同時開始掃描的方法,,完成一個8×8塊的掃描僅需要33個時鐘周期,,節(jié)約了掃描的時間。

1 整數(shù)變換和掃描算法分析

1.1 整數(shù)變換

早期的視頻編碼標準往往采用浮點DCT來去除視頻圖像的空間冗余,,而浮點變換不適合在數(shù)字硬件環(huán)境中實現(xiàn)。在實際中,,常采用整數(shù)近似的DCT代替浮點DCT來編碼視頻圖像,,不僅可以保持浮點變換的編碼性能,而且能夠大大減少計算復(fù)雜度,。但是整數(shù)DCT近似有可能出現(xiàn)編解碼器采用不同的DCT和IDCT的情況,,這種情況會導(dǎo)致解碼圖像的誤差漂移[1]。為了避免這個問題,,AVS采用8×8的二維整數(shù)變換,,變換公式如下[1]:

Y=T8 X T8T(1)

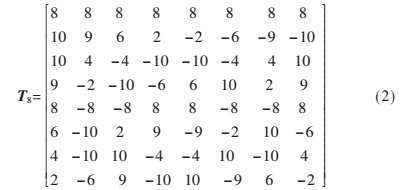

其中,,X為殘差系數(shù)矩陣,T8為8×8變換矩陣,,有:

可見,,變換矩陣T8具有奇數(shù)行奇對稱和偶數(shù)行偶對稱的特性,這為后文整數(shù)變換模塊的優(yōu)化提供了條件,。

1.2 掃描

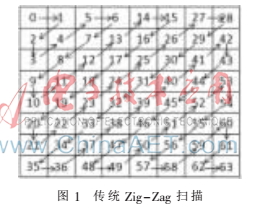

1976年,,Tescher在他的自適應(yīng)變換編碼方案中首次提出DCT系數(shù)的高效組織方式——Zig-Zag掃描。此掃描方式成為DCT系數(shù)高效熵編碼前所常用的預(yù)處理技術(shù),,并一直沿用至今,。通常把掃描中遇到的非零系數(shù)記為level,一個非零系數(shù)前的連續(xù)零系數(shù)游程記為run[1],。掃描后的系數(shù)被組織成(run,,level)對。傳統(tǒng)的Zig-Zag掃描從低頻系數(shù)開始逐個掃描,,掃描一次需要64個時鐘周期,,如圖1所示。

2 硬件結(jié)構(gòu)

系統(tǒng)工作頻率為100 MHz時,,實現(xiàn)AVS高清1 920×1 088,、30 f/s格式視頻的實時編碼,一個宏塊的處理時間為4 085 ns,,即不超過408個時鐘周期,,否則就不滿足高清編碼的要求。

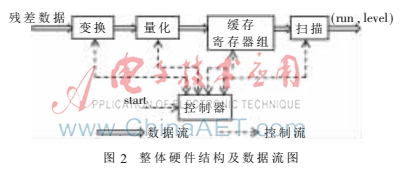

本文提出了一種高效簡潔的變換,、量化和掃描系統(tǒng)結(jié)構(gòu),,硬件結(jié)構(gòu)及數(shù)據(jù)流如圖2所示??刂颇K依據(jù)緩存寄存器組的狀態(tài)產(chǎn)生輸入殘差數(shù)據(jù)命令,,每個周期讀入一列殘差數(shù)據(jù)。殘差數(shù)據(jù)經(jīng)過變換后送入量化模塊進行量化,。量化數(shù)據(jù)保存到緩存寄存器組,,由掃描模塊控制并進行掃描,掃描模塊輸出(run,,level)對,。變換和量化模塊內(nèi)部都采用流水線結(jié)構(gòu)。

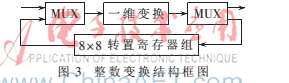

2.1 變換模塊

變換模塊是將當(dāng)前塊的殘差系數(shù)矩陣轉(zhuǎn)換為變換系數(shù)矩陣的一個過程,,其結(jié)構(gòu)框圖如圖3所示,。此設(shè)計采用一維變換和轉(zhuǎn)置矩陣實現(xiàn)二維變換,與參考文獻[4]中的設(shè)計相比節(jié)約了硬件資源。參考文獻[5]中轉(zhuǎn)置操作由RAM實現(xiàn),,本文中轉(zhuǎn)置操作由8×8的寄存器組實現(xiàn),,避免了訪問RAM造成的延時,便于后續(xù)的并行流水線處理,。參考文獻[6]中整數(shù)變換采用了蝶形算法,,其缺點是需要對變換后的結(jié)果進行重排序。參考文獻[7]提出了一種快速有效的變換方法,,但是資源消耗大,。本文對整數(shù)變換的方法進行了優(yōu)化,節(jié)約了不必要的硬件資源和時鐘,。

下面主要介紹一維整數(shù)變換過程,。

設(shè)AVS的一維整數(shù)變換的輸入、輸出變量分別為:

X=[X0,,X1,,X2,X3,,X4,,X5,X6,,X7](3)

Y=[Y0,,Y1,Y2,,Y3,,Y4,Y5,,Y6,,Y7](4)

根據(jù)Y=T8×X,把8個輸出元素展開成以下組合,,其中T8為8×8的變換矩陣:

R0=X0+X7,;R1=X1+X6;R2=X2+X5,;R3=X3+X4,;

R4=X0-X7;R5=X1-X6,;R6=X2-X5,;R7=X3-X4。

再定義12個中間變量M0~M11:

M0=R0+R3,;M1=R1+R2,;M2=R0-R3,;

M3=R1-R2,;M4=4R4+4R6,;M5=9R5+2R7;

M6=9R4-10R6,;M7=2R5+6R7,;M8=6R4+2R6;

M9=9R7-10R5,;M10=2R4+9R6,;M11=4R5+4R7。

其中所有的乘法均可化為移位操作,,重新整理后得到輸出:

Y0=8M0+8M1,;Y1=M4+M5+M8;Y2=10M2+4M3,;

Y3=M6-M7,;Y4=8M0-8M1;Y5=M8+M9,;

Y6=4M2-10M3,;Y7=M10-M11-M7。

由以上算法可以看出,,一維變換模塊只需要移位和加法操作,,既方便硬件實現(xiàn),還節(jié)省了硬件資源,。經(jīng)計算,,此一維變化模塊共需要40個加法器,比參考文獻[7]中的一維變換節(jié)省了加法器和移位器,。

設(shè)計中對變換采用流水線的處理方法[7],,先進行列變換,然后進行行變換,,單步變換為3級流水線結(jié)構(gòu),。變換模塊中,第1時鐘周期進行并行讀取數(shù)據(jù),,第2,、3個時鐘周期進行一維反變換,第4個時鐘周期開始向轉(zhuǎn)置矩陣中存入一維反變換后的數(shù)據(jù),,第12個時鐘周期開始讀取轉(zhuǎn)置矩陣中的數(shù)據(jù),,第14個時鐘周期開始輸出數(shù)據(jù),第21個時鐘周期結(jié)果輸出完畢,。

2.2 量化

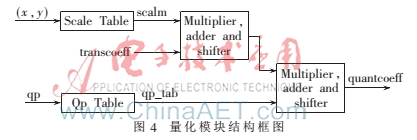

量化模塊采用并行流水線進行設(shè)計,,每個周期處理一行數(shù)據(jù)。該模塊采用了3級流水線,第一級流水線通過查表得到伸縮參數(shù)scalm和量化參數(shù)qp_tab,;第二級流水線計算Y=(transcoeffscalm+218)>>19,,其中,transcoeff為變換系數(shù),;第三級流水線計算quantcoeff=(Yqp_tab+214)>>15,,其中,quantcoeff為量化系數(shù),。該模塊的結(jié)構(gòu)框圖如圖4所示,。

2.3 掃描

經(jīng)過整數(shù)變換和量化后,需要對變換后的系數(shù)進行Zig-Zag掃描,。傳統(tǒng)掃描是將64個系數(shù)從首端開始逐個進行掃描,,因此傳統(tǒng)掃描方法會占用大量的時鐘周期,降低了編碼的速度,,不利于高清實時編碼,。

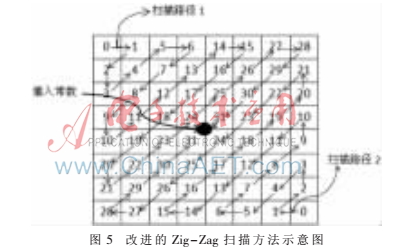

本文改進了傳統(tǒng)的Zig-Zag掃描方法,對變換后的系數(shù)從首尾兩端同時開始掃描,,節(jié)約了掃描的時間,。其實現(xiàn)方法示意圖如圖5所示。首先,,在量化后的系數(shù)矩陣的中間插入一個非零常數(shù),,然后從該系數(shù)矩陣的首尾兩端同時開始掃描,一共掃描33個周期,。掃描路徑1統(tǒng)計非零系數(shù)前零的個數(shù)run0和非零系數(shù)值level0,,掃描路徑2統(tǒng)計非零系數(shù)后零的個數(shù)run1和非零系數(shù)的值level1,并逐個輸(run0,,level0)和(run1,,level1)。最后,,將第33個掃描周期輸出的run0和run1相加,,并將結(jié)果賦給run1,即得到插入常數(shù)后面的第一個非零系數(shù)前零的個數(shù),,而插入常數(shù)后面的第一個非零系數(shù)的值為第33個掃描周期輸出的level1,。至此掃描完成。

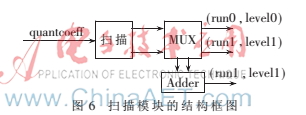

改進的掃描方法完成掃描過程只需要33個時鐘周期,,比傳統(tǒng)的掃描方法節(jié)省31個時鐘周期,。掃描模塊的結(jié)構(gòu)框圖如圖6所示。與傳統(tǒng)的掃描方法相比,,只增加了一個選擇器和加法器,,卻節(jié)約了將近一半的掃描時間,。

3 仿真綜合結(jié)果及分析

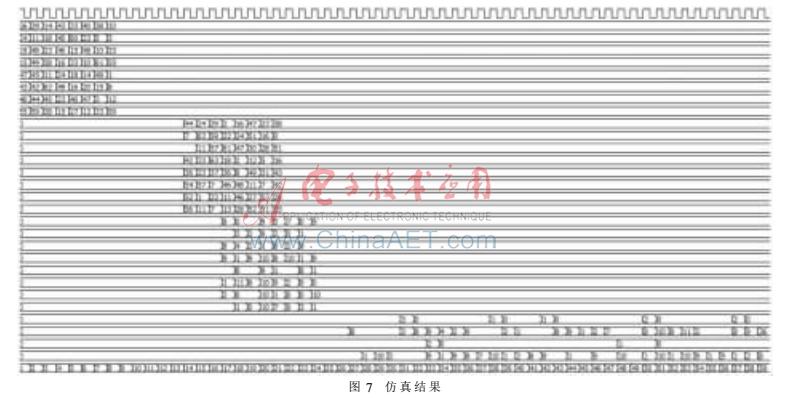

根據(jù)上述思想,采用Verilog HDL語言完成硬件的編寫,,選用Altera公司的軟件Quartus II 11.0和ModelSim 6.6d進行了實現(xiàn)和仿真,。部分仿真結(jié)果如圖7所示。從仿真圖中可以看出,,本設(shè)計中第1~21個周期完成一個塊的變換,第17~24個周期完成量化,,第25~26個周期進行掃描數(shù)據(jù)的準備,,第27~59個周期完成數(shù)據(jù)的掃描并輸出掃描的結(jié)果,整個掃描過程只用了33個周期,,各個模塊輸出結(jié)果正確,,達到了預(yù)期的設(shè)計要求。本設(shè)計完成一個塊的變換,、量化和掃描需要59個時鐘周期,,因此,處理一個宏塊的時間為236個時鐘,,滿足編碼要求,。

本設(shè)計采用的FPGA為Altera公司的EP2C35F672C6。綜合占用的資源如圖8所示,。由圖8可見,,使用LE的總數(shù)為4 157個。綜合布局布線后的結(jié)果表明,,該結(jié)構(gòu)的最高頻率為120 MHz,,滿足設(shè)計的要求。

參考文獻

[1] 高文,,趙德斌,,馬思偉.數(shù)字視頻編碼技術(shù)原理[M].北京:科學(xué)出版社,2010.

[2] 李文軍,,王祖強,,徐輝,等.基于FPGA的AVS幀內(nèi)預(yù)測電路設(shè)計[J].電子技術(shù)應(yīng)用,,2013,,39(8):50-53.

[3] AVS工作組.信息技術(shù)先進音視頻編碼:視頻[M].北京:中國標準出版社,2006.

[4] 劉海鷹,,張兆楊,,沈禮權(quán).基于FPGA的H.264變換量化的高性能的硬件實現(xiàn)[J].中國圖象圖形學(xué)報,2006,,11(11):1636-1639.

[5] 黃學(xué)超,,張衛(wèi)寧.AVS編碼變換量化和掃描硬件設(shè)計與實現(xiàn)[J].電氣電子教學(xué)學(xué)報,,2011,33(2):34-37.

[6] 白玉婷.AVS編碼器關(guān)鍵模塊的硬件設(shè)計[D].太原:太原理工大學(xué),,2012.

[7] Wang Leirui,,Zhang Zhaoyang,Teng Guowei,,et al.Hardwareimplementation of transform and quantization for AVS encoder[C].ICALP 2008,,2008:843-847.