ISSCC 2020 頂著新冠疫情,于2月16日開始在舊金山地下室繼續(xù)召開。開會的結(jié)果就是會議結(jié)束后,舊金山市宣布進入面的疫情緊急狀態(tài)。()雖然今年沒有去開成會,但是不影響小編的擼文章/Slides進程。許多公眾號都已經(jīng)把今年ISSCC的核心焦點放在Chiplet——這個說新不新,卻再次綻放光芒的設(shè)計方法——上。小編也在此分享個人關(guān)于Chiplet對于集成電路生態(tài)、體系結(jié)構(gòu)、模擬電路影響的一些思考。

導(dǎo)讀一:雖然本文有著科普的初心,但是為了節(jié)約篇幅,對于Chiplet一些基礎(chǔ)知識大家可參考黃老師的《ISSCC 2020看Chiplet研究現(xiàn)狀》,我們的《ISSCC 2020 觀感:高級封裝正在成為潮流》,以及唐博士的《從AI Chip到AI Chiplet》,本文不贅述技術(shù)細節(jié)。

導(dǎo)讀二:本文的觀點可能比較科幻,純屬個人臆測,大家自行決定是否相信,這里先把結(jié)論羅列出來(1)Chiplet拐點將帶領(lǐng)集成電路生態(tài)將邁入“打土豪分田地"的新時期;(2)Chiplet拐點面前,新形態(tài)體系結(jié)構(gòu)形態(tài)的將提倡富含想象力的小而美,并且“去中心化”;(3)Chiplet拐點將誕生一類新型態(tài)的富含模擬電路芯片——有源基板,它將終結(jié)低電壓低增益低匹配的先進工藝模擬設(shè)計困局。

打土豪,分田地

如果用一個字來概來涵蓋單芯片片上系統(tǒng)(Monolithic SoC)方案與芯粒(Chiplet)方案,我會選天朝人民最耳熟能詳?shù)摹安稹弊帧:喍灾褪前言瓉硪粔K大的單芯片,拆分為多個小芯片的組和,然后通過高級封裝重組。以前我們也把這樣的模式稱為System-in-Package,2.5D/3D封裝。2015年,Marvell的老板還把這樣的模式稱為芯片界的樂高——抹茶計劃(Mochi)。

但是SiP早期只是滿足不同工藝間芯片的鏈接,比如CPU/GPU和DRAM的異構(gòu)集成。所以當(dāng)時Chiplet被提出以后,也就是少數(shù)幾個學(xué)有余力的學(xué)霸間的花式表演。SoC在過去的很長一段時間,仍然是主流,Chiplet拐點從未真正到來。

然而,世界發(fā)展地太快。AI來了,貪欲來了,土豪炫富心態(tài)也來了。Monolithic SoC芯片在過去幾年進入了“貧窮限制了想象力”的新境界——

首先推波助瀾的英偉達黃教主,收到人工智能的助力,英偉達的旗艦GPU從100mm2,開始指數(shù)級發(fā)展。去年發(fā)布的Volta架構(gòu)核彈級GPU——GV100的面積率先突破800mm2大關(guān),據(jù)說今年即將推出的Ampere系列新核彈級GPU將在7nm工藝達到826mm2 【瑟瑟發(fā)抖地 】。

然后就是那些不要face的初創(chuàng)小妮子們,為了造一個個大新聞,變得毫無”節(jié)止“(此處不帶貶義)—— 其中最有名的當(dāng)推硅谷初創(chuàng) Cerebras Systems的AI芯片,面積達到了令人發(fā)指的46,225mm2,(你沒有看錯,那是逗號!)片上SRAM達到18GB 【我只能說你咋不上天呢?】:

如此大面積的芯片,有良率么,有意義么?下圖統(tǒng)計了良率與面積大小的關(guān)系,對于小于10mm2的芯片而言,monolithic方案和chiplet方案的良率差別很小,但是一旦芯片面積超過200mm2,monolithic方案的良率會比chiplet方案低超過20%。可以預(yù)期,在700-800mm2的面積上,monolithic方案的良率很可能不超過10%。

由此,對于要商業(yè)化賣錢的芯片而言成本問題就活生生地體現(xiàn)了。假設(shè)研發(fā)費用是相同的,那么可以分攤研發(fā)一次性費用NRE的芯片數(shù)量,chiplet會比monolithic高3-4倍。如果忽略制造成本,但chiplet方案的成本價將遠遠低于monolithic方案。

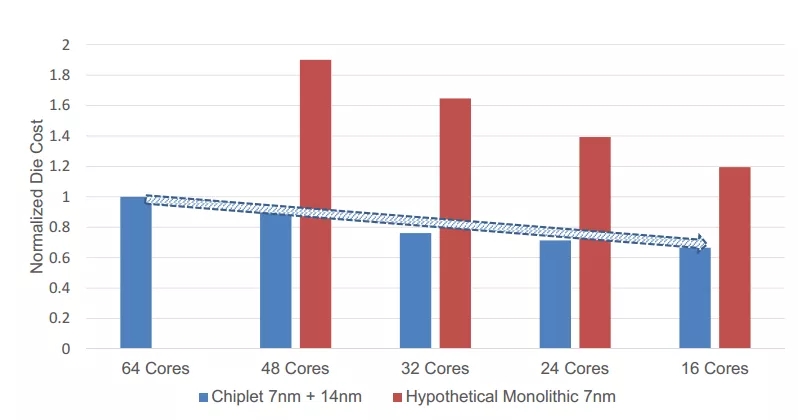

AMD公司在ISSCC2020年上就以其多核架構(gòu)為例子,對比了AMD服務(wù)器級別設(shè)計中,采用chiplet方案和monolithicSoC方案的成本,可見芯片越大monlithic方案和的成本比在chiplet高的越多,并且能保持在一倍以上。

誠然,土豪們與新貴們依舊可以炫富。但是chiplet卻是高性能芯片(組)打開市場化,完成生態(tài)的最有效捷徑。

正所謂,他強由他強,清風(fēng)拂山崗;他橫由他橫,明月照大江;他自狠來他自惡,我自一口真氣足。“小而美”的專用芯片們,只要能搭上chiplet高速列車,終究笑到最后才是王道。

去中心化的新架構(gòu)形態(tài)

故事講到這里,看官們你或許會問,chiplet是不是只會給龐然大物帶來沖擊?小打小鬧的呢?我在過去的很長一段時間,也簡單的認為,chiplet是是巨頭們的樂高玩具,學(xué)術(shù)界的玩家既玩不起,也沒啥必要玩。

直到今年的ISSCC,當(dāng)頭一棒點醒了我。

還用樂高做例子。樂高除了有圖紙按圖索驥的標(biāo)準(zhǔn)玩法,還有給出元模塊自定義樂高的高級版——Lego MOC (My Own Creations),每年樂高官方都會有Lego MOC的最佳評比。小編某天還在B站抖音刷到過一個用樂高做的洗丑襪子專用迷你洗衣機。

即便如此,樂高迷們?nèi)匀徊蛔阋詽M足MoC的需求,此時,3D打印的普及進一步?jīng)_擊了樂高的世界——用戶可以自定義元積木的任何形狀,然后打印出來,以填補官方元間庫的不足。好事者還用Lego MOC自己打造打一個3D打印機的教程。于是,樂高的世界打開了新維度的新大門~

當(dāng)3D打印遇上樂高MOC

搭樂高當(dāng)然有不同的搭法,搭chiplet也一樣。常規(guī)方法就是按照目前高性能計算體系結(jié)構(gòu)的研究成果,按圖索驥搭出如下類SoC的標(biāo)準(zhǔn)化結(jié)構(gòu),以主控/多核CPU為核心+并行計算協(xié)處理器(GPU,AI芯片)+ 堆疊的Memory+IO是常規(guī)操作。(下圖來自ISSCC 2020 法國CEA的chiplet paper)

與常規(guī)操作相對應(yīng)的,就是非主流殺馬特了。Chiplet的發(fā)展會催生非常多目前不存在的芯片形態(tài),或者大大簡化某些形態(tài)的芯片進入主流平臺的過程。

在這個過程中,“去中心化”或?qū)⒊蔀橐粋€重要的特點。

先來看AMD的Server級處理器Chiplet方案——二代EPYC。(這家伙在7nm工藝下耗電280W,據(jù)前方記者報道,該芯片在ISSCC現(xiàn)場demo用液氮冷卻云山霧罩,遠觀還以為是炊煙裊裊)

AMD的Chiplet方案方案,由其Ryzen系列芯片演化而來。然而,在逐漸演化的過程中,系統(tǒng)的核心從CCX高性能計算核,逐步變成了一顆一存儲和互聯(lián)為主的IOD核。而且AMD還給IOD的互聯(lián)拓撲結(jié)構(gòu),起了一個“復(fù)仇者聯(lián)盟”式的名字——無限結(jié)構(gòu),infinity fabric。

而原本在系統(tǒng)中起著關(guān)鍵作用的處理器核心,變成了一個可以被scaling的元素:2/4/6/8,任意數(shù)量的核心方案都可以定制,要多少買多少,經(jīng)濟實惠。

Chiplet的這種新型配置帶來的主客異位的變化是否會引發(fā)體系結(jié)構(gòu)的新一輪討論?這種新形態(tài)下的互聯(lián)方式和存儲模式,還有沒有必要遵從目前主流的片上網(wǎng)絡(luò)/總線的模式?畢竟從物理學(xué)上,其電路的拓撲結(jié)構(gòu)已經(jīng)不一樣了。他也應(yīng)該不同于現(xiàn)在繁瑣的PCIe等一鏈接版上原件為主的橋連接方法,畢竟還是夠近,通信間即便需要一些協(xié)議,也應(yīng)該是簡單的。

法國CEA在ISSCC 2020提出了他們的建議:采用如下的全數(shù)字,全擺幅,極簡的準(zhǔn)同步握手機制,完成chiplet間通信。chiplet間通信的延時采用延時補償?shù)臋C制,相比于片內(nèi)SoC的延遲,只提高了1到3倍,根據(jù)距離長短,完全可估計。相比于目前的LPDDR之類的協(xié)議,無論在電路復(fù)雜度還是能效上都有顯著提高。

在這種特征下,“去中心”化的設(shè)計理念是保障芯片組間可以靜態(tài)重構(gòu)的重要前提。畢竟很可能Chiplet的主體再也不是擁有譯碼能力的處理器核心,而是一個并沒有多少處理能力的片上網(wǎng)絡(luò)。與此同時,每一個Chiplet的鍵位上可以放芯片類型也將更加不拘一格。除了今年ISSCC提到的微處理器,還可以是如今火爆的存算一體芯片,領(lǐng)域?qū)S眯酒堑湫虲MOS工藝(ReRAM / MEMS / TFET / ...)的IoT芯片等等,以及更多發(fā)揮想象力的新型芯片。只要你流的起片,去他的超大規(guī)模SoC設(shè)計驗證,小而美的百花齊放才是春天。

總之一句,Chiplet拐點到來后,玩家絕不僅是土豪,去中心化發(fā)展會讓土豪們面臨各種“特洛伊”陷阱。

模擬電路能擺脫scaling down噩夢了?

不同于AMD,Intel和CEA設(shè)計chiplet方案時,還推出了一種全新功能定義的電路來實現(xiàn)chiplet——active interposer,有源基板。

早期的Chiplet基板,實現(xiàn)的功能完成芯片間的互聯(lián)和芯片pin腳到封裝pin腳的扇出功能,取代wire bond方案里面長長引線的寄生效應(yīng),可以簡單的理解為是密度更高、體積更小的PCB版,也被稱為無源基板, passive interposer。

但是,今年ISSCC上法國CEA提出的有源基板卻令人眼前一亮:

有源基板講白了就是一顆工藝節(jié)點大、面積大、能做底盤的新型芯片,由于是完整的芯片,設(shè)計師可以自定義這顆芯片的方案。

在CEA的方案中,不僅可以用于鏈接,同時通過實現(xiàn)路由功能(router)在基板上完成類片上網(wǎng)絡(luò)的互聯(lián)。更驚艷的是,他在基板上實現(xiàn)了基于開關(guān)電容的穩(wěn)壓電源。由于基板工藝的節(jié)點比高性能計算的節(jié)點大很多、成本低很多,所以,用基板工藝做一些用能量存儲的大容量片上電容一點都不心疼。這時候也完全不用擔(dān)心先進工藝下各種開關(guān)的各種非理想(漏電/淺溝槽閾值調(diào)制)等非理想效應(yīng)。

過去十年,模擬電路工程師們被摩爾定律逼的要多慘有多慘。Scaling下先進工藝那低于1V的電源電壓,(卻沒有scaling熱噪聲的幅度,SNR又不允許下降);越來越低的輸出阻抗,導(dǎo)致放大器的增益難以為繼;甚至是40nm后開始的不可理喻的版圖匹配要求,還有FinFET開始的柵極電阻……種種麻煩都在把基于運算放大器的傳統(tǒng)模擬電路往絕路上逼。模擬工程師們只能調(diào)轉(zhuǎn)槍頭往Digital PLL / Digial LDO / SAR ADC / Digital PA等不少基于數(shù)字電路的模擬設(shè)計上走,可總有些電路是要靠放大器的。

然而chiplet卻給了讓這一困局新的思路——把適合大工藝節(jié)點的模擬電路放在有源基板上。同時,還包括那些占面積超大的無源器件,這個方法同時還能將最大程度地提高先進工藝的利用效率,把昂貴的工藝花在刀刃上。讓做放大器的模擬工程師遠離先進工藝的噩夢,回到亞微米時代自由發(fā)揮的黃金歲月。

下圖是Intel在今年ISSCC 2020的Chiplet 產(chǎn)品——lakefield的Foveros 3D封裝平臺里提到的如何布局計算芯片(Compute Die)和基板芯片(Base Die)的策略。高壓(比如高壓串行接口USB/LVDS,用于同步的晶振)、無源、電源管理、以及對Scaling Down不敏感的模擬電路,還有各類經(jīng)典(溫度等)傳感器統(tǒng)統(tǒng)可放在基板大節(jié)點工藝上。

順帶提一句,當(dāng)在選擇不同節(jié)點的基板時,還能發(fā)揮初異構(gòu)的功耗優(yōu)勢。比如Intel在選擇基板上用了超低漏電的節(jié)點(22FFL),然后將standby的相關(guān)電路集成到大基板上去,進一步優(yōu)化stand功耗。這是傳統(tǒng)SoC不具有的選項。

chiplet拐點也讓模擬工程師可以喘口氣,不再被scaling down追著打了。

能看到這里的讀者們,你對Chiplet心動了么?如果您有更多comments,歡迎留言。