在摩爾定律的指引下,芯片上集成的晶體管數(shù)量不斷超越人們的想象,芯片性能也不斷升級(jí),同時(shí)成本逐年下降。

但隨著半導(dǎo)體制造工藝的不斷升級(jí),從7nm、5nm到3nm等延伸下去,越來越接近物理極限,而工藝提升所帶來的成本效益也越來越不明顯,僅靠工藝節(jié)點(diǎn)提升已無法滿足市場需求。如何讓芯片繼續(xù)提升算力同時(shí)降低成本?業(yè)界需要在其他途徑上再想對(duì)策。

Chiplet芯粒技術(shù)就是一個(gè)新的探索。

日前,在IC CHINA 2020的開幕式上,芯原股份創(chuàng)始人、董事長兼總裁戴偉民詳細(xì)解讀了Chiplet芯粒這一新技術(shù),剖析了Chiplet時(shí)下的新機(jī)遇。

Chiplet最早由Marvell創(chuàng)始人周秀文提出,在ISSCC2015上,周秀文率先提出MoChi(Modular Chip,模塊化芯片)架構(gòu)的概念。據(jù)戴偉民介紹,MoChi是許多應(yīng)用的基準(zhǔn)架構(gòu),包括物聯(lián)網(wǎng)、智能電視、智能手機(jī)、服務(wù)器、筆記本電腦、存儲(chǔ)設(shè)備等。

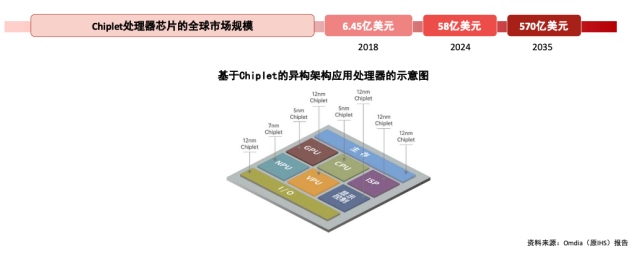

戴偉民認(rèn)為,先進(jìn)工藝中只有22nm、12nm和5nm這三個(gè)工藝節(jié)點(diǎn)是“長命節(jié)點(diǎn)”,其他中間節(jié)點(diǎn)的“壽命”都比較短。而且,并非每種芯片都需要5nm這樣的尖端工藝,因?yàn)椴皇敲恳患夜径寄茇?fù)擔(dān)起5nm工藝的成本,于是Chiplet這種將不同工藝節(jié)點(diǎn)的die混封的新形態(tài)是未來芯片的重要趨勢之一。

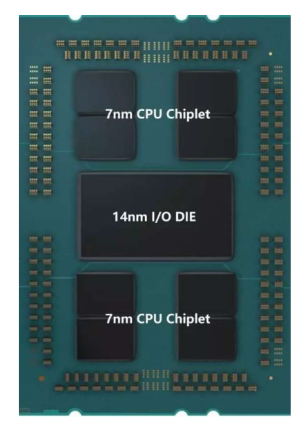

據(jù)戴偉民介紹,目前將Chiplet運(yùn)用做得最好的是AMD。在一塊芯片上,CPU用的是7nm工藝,I/0則使用的是14nm工藝,與完全由7nm打造的芯片相比成本大約降低了50%。

“AMD是最會(huì)做大芯片的公司,連它都能接受小芯片,這很好的證明了Chiplet的發(fā)展前景。”戴偉民表示。

戴偉民在演講中還特別強(qiáng)調(diào),封裝和接口對(duì)于Chiplet的重要性。臺(tái)積電的CoWoS技術(shù)和英特爾的Foveros 3D立體封裝技術(shù)都為Chiplet的發(fā)展奠定了基礎(chǔ),接口則代表了標(biāo)準(zhǔn)問題,芯片拼接在一起需要有一致的互聯(lián)協(xié)議。所以,戴偉民表示,何時(shí)切入Chiplet領(lǐng)域很關(guān)鍵,如果過早切入,則沒有標(biāo)準(zhǔn)可以依靠,設(shè)計(jì)好的成品可能會(huì)面臨日后的接口不匹配等問題。

不過,整體來看,Chiplet給半導(dǎo)體全產(chǎn)業(yè)鏈都帶來了新的機(jī)會(huì)。戴偉民指出,芯片設(shè)計(jì)環(huán)節(jié)能夠降低大規(guī)模芯片設(shè)計(jì)的門檻;半導(dǎo)體IP授權(quán)商能升級(jí)為Chiplet供應(yīng)商,提升IP的價(jià)值且有效降低芯片客戶的設(shè)計(jì)成本;芯片制造與封裝環(huán)節(jié)能夠增設(shè)多芯片模塊(Multi-Chip Module,MCM)業(yè)務(wù),Chiplet迭代周期遠(yuǎn)低于ASIC,可提升晶圓廠和封裝廠的產(chǎn)線利用率;標(biāo)準(zhǔn)與生態(tài)環(huán)節(jié),則能夠建立起新的可互操作的組件、互連、協(xié)議和軟件生態(tài)系統(tǒng)。例如,作為IP供應(yīng)商的芯原提出了IP as a Chip(IaaC)的理念,旨在以Chiplet實(shí)現(xiàn)特殊功能IP從軟到硬的“即插即用” ,解決7nm、5nm及以下工藝中性能與成本的平衡,并降低較大規(guī)模芯片的設(shè)計(jì)時(shí)間和風(fēng)險(xiǎn)。

據(jù)Omdia報(bào)告,2018年Chiplet市場規(guī)模為6.45億美元,預(yù)計(jì)到2024年會(huì)達(dá)到58億美元,2035年則超過570億美元,Chiplet的全球市場規(guī)模正在井噴式增長。