幾十年來,,封裝半導(dǎo)體集成電路的規(guī)范方式是單個(gè)單元從晶片中切割后再進(jìn)行封裝的工藝。然而,,這種方法不被主要半導(dǎo)體制造商認(rèn)可,,主要是因?yàn)楦咧圃斐杀疽约敖裉斓哪K的射頻成分在增加。

因此,,晶圓級(jí)封裝(WLP)的出現(xiàn)帶來了低成本封裝開發(fā)的范式轉(zhuǎn)變,。WLP是一種在切割晶圓封裝器件之前的晶圓級(jí)封裝技術(shù)。使用標(biāo)準(zhǔn)工具和工藝,,WLP作為晶圓制造過程的擴(kuò)展,。最終,制造的WLPdie將在芯片表面上有金屬化墊,,并在切割晶圓之前在每個(gè)墊上沉積焊錫點(diǎn),。

這反過來又使WLP與傳統(tǒng)的PCB組裝工藝兼容,并允許對(duì)晶圓本身進(jìn)行器件測(cè)試,。因此,,這是一個(gè)相對(duì)較低的成本和效率的工藝,特別是當(dāng)晶圓尺寸增加而芯片die在收縮時(shí),。

晶圓的尺寸在過去幾十年中一直在增加,,從直徑4、6,、8英寸增加到12英寸,。這導(dǎo)致每個(gè)晶圓die的數(shù)量增加,,從而降低了制造成本。

在電氣性能方面,,WLP優(yōu)于其他封裝技術(shù),,從某種意義上說,一旦WLP器件集成在密集的RF模塊中,,它就會(huì)導(dǎo)致EM寄生耦合顯著減少,,因?yàn)槠骷蚉CB之間的互連相對(duì)較短,而不像在某些類型的CSP技術(shù)中使用線鍵合互連,。

WLP芯片倒裝(flip-chip)技術(shù)

倒裝(flip-chip)芯片技術(shù)也被稱為控制塌陷芯片連接(C4,,controlledcollapsechipconnection),是IBM在20世紀(jì)60年代開發(fā)的芯片組裝技術(shù)之一,。

雖然基于導(dǎo)線鍵合的封裝技術(shù)在硬件建成后為實(shí)驗(yàn)室調(diào)試提供了自由的電感能力方面更加靈活,,而且還提供良好的熱導(dǎo)特性,但使用倒裝芯片封裝技術(shù)使用焊錫凸起使基板和芯片之間的電氣連接提供了相對(duì)尺寸減小,、減少延遲以及在其輸入和輸出引腳方面實(shí)現(xiàn)更好地隔離,。

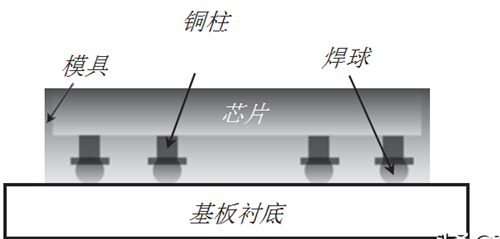

圖1說明了芯片die在基板上的基本結(jié)構(gòu),在芯片表面生長(zhǎng)的Cu柱頂部有焊錫球,。焊點(diǎn)通常由填充?;衔锓庋b,為焊點(diǎn)提供機(jī)械支撐,。

圖1,、倒裝(flip-chip)芯片的基本結(jié)構(gòu)示例

WLP芯片級(jí)封裝

芯片級(jí)封裝CSP(chipscalepackaging)是微電子和半導(dǎo)體工業(yè)中最常用的封裝方法之一。

雖然有幾種類型的CSP技術(shù)已經(jīng)可供微芯片制造商使用,,但新的類型繼續(xù)出現(xiàn),以滿足對(duì)支持新功能和新的特定應(yīng)用的產(chǎn)品的需求,。這些包裝要求可能因所需的可靠性水平,、成本、附加功能和整體尺寸而不同,。

顧名思義,,CSP的封裝尺寸與芯片die尺寸大致相同,這是其主要優(yōu)點(diǎn)之一,。通過采用WLP制造工藝,,CSP正在不斷發(fā)展,以實(shí)現(xiàn)最小可能的封裝-die之間的尺寸比,。

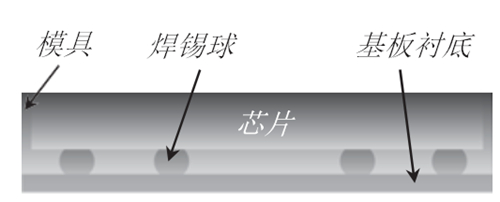

如圖2所示,,CSP在封裝下的球柵陣列(BGA)風(fēng)格允許有幾個(gè)互連,同時(shí)簡(jiǎn)化PCB路由,,提高PCB組裝產(chǎn)量,,降低制造成本,。

圖2、芯片級(jí)封裝CSP(chipscalepackaging)的基本結(jié)構(gòu)示例

其它的封裝技術(shù)

還有幾種其它的集成電路封裝形式,,允許無縫集成到應(yīng)用定制的模塊封裝中,。

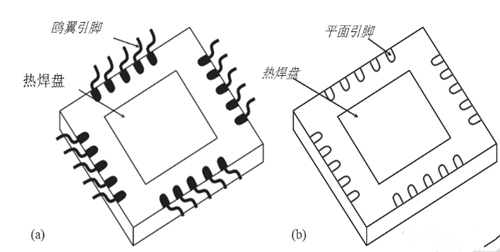

四平封裝(QFP,Quadflatpackage)是最早的表面貼裝IC封裝技術(shù)之一,,其中封裝的結(jié)構(gòu)是由四個(gè)側(cè)面組成的,,具有擴(kuò)展的互連引線,如圖3(a)所示,。

凸起的引線連接到封裝框架上,,在引線和芯片die金屬之間形成一個(gè)金屬-絕緣體-金屬(MIM,metal-insulator-metal)型的電容,,可以作為匹配元件,。

該技術(shù)適用于毫米大小的IC,其中封裝的外圍引腳數(shù)量可以達(dá)到100多個(gè)引腳,。這種類型的封裝還存在幾種衍生物,,它們?nèi)Q于所使用的材料,如陶瓷四扁封裝(CQFP,,ceramicquadflatpack),、薄四扁封裝(TQFP,thinquadflatpack),、塑料四扁封裝(PQFP,,plasticquadflatpack)以及金屬四扁封裝(MQFP,metalquadflatpack),。

圖3(b)所示的四平無引線(QFN,,Quadflatnolead)是由平面銅引線框架和用作散熱器的熱傳播墊的塑料封裝形成的幾種表面安裝封裝技術(shù)之一。鍵合線(Wirebonding)也可以用于互連,,而且由于鍵合線不僅是導(dǎo)體,,而且是電感,它們通常會(huì)影響在這項(xiàng)封裝技術(shù)下器件的性能,,除非它被視為整個(gè)設(shè)計(jì)的一部分,。

雖然QFN是由四個(gè)側(cè)面組成的互連,但雙平面無引線(DFN)也已經(jīng)出現(xiàn),,并組成互連平面引線的兩側(cè),。

圖3、集成電路封裝技術(shù):(a)四平封裝和(b)四平無引腳封裝

然而,,我們剛才討論的所有封裝技術(shù)都不適用于當(dāng)代微電子SoP和SiP,。

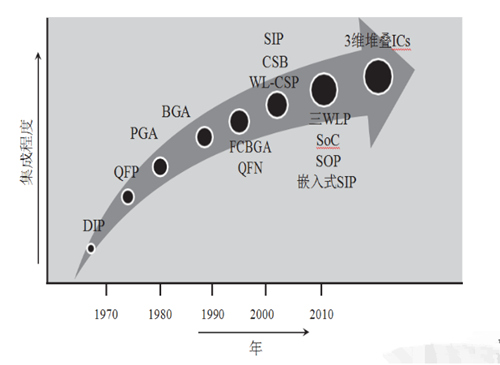

它們的使用在20世紀(jì)90年代超大規(guī)模集成電路革命期間蓬勃發(fā)展,隨著更緊湊和更密集的晶圓級(jí)封裝技術(shù)的出現(xiàn)而逐漸被淘汰,。在過去幾十年中,,芯片和模塊封裝技術(shù)的發(fā)展主要是由引腳計(jì)數(shù)需求的增加所驅(qū)動(dòng)的,,并見證了功能、組件密度和集成水平的巨大提高,。

圖4顯示了自1970年以來集成電路封裝的演變,,其中雙內(nèi)聯(lián)封裝(DIP,dualinlinepackages)開始在電子IC行業(yè)發(fā)揮作用,,然后出現(xiàn)了更多引腳的IC,,如QFP,甚至更高的引腳計(jì)數(shù)技術(shù),,如引腳網(wǎng)格陣列(PGA,,pingridarray)以及倒裝芯片球網(wǎng)格陣列(FCBGA,flip-chipballgridarray)等,。