在1納米或更小規(guī)格也能保持高導(dǎo)電性體的新材料TMDC

2023年2月,日本產(chǎn)業(yè)技術(shù)綜合研究所 (AIST)與東京都立大學(xué)聯(lián)合宣布,已經(jīng)成功在二硫化鉬 (MoS2) 上形成了層狀材料三碲化二銻 (Sb2Te3),并 制造的 n 型 MoS2晶體管具有足夠的耐熱性以承受半導(dǎo)體制造過程。

一種稱為過渡金屬二硫化物(TMDC)的材料具有二維晶體結(jié)構(gòu),作為下一代晶體管溝道的半導(dǎo)體材料受到關(guān)注,因?yàn)樗词乖?1 納米或更小的原子層區(qū)域也能保持高導(dǎo)電性。然而,公共金屬電極與MoS2界面之間的高接觸電阻阻礙了晶體管性能的提升。

AIST正在參與日本科學(xué)技術(shù)廳的戰(zhàn)略基礎(chǔ)研究促進(jìn)計(jì)劃(CREST)“原子層異質(zhì)結(jié)構(gòu)器件的演示和3D集成LSI的原子層沉積工藝的開發(fā)(2017-2021財(cái)年):Metropolitan I一直在研究與大學(xué)的聯(lián)合項(xiàng)目中的高性能 TMDC 晶體管。

這一次,研究小組使用 MoS2制造了晶體管,并專注于將Sb2Te3作為其接觸材料。Sb2Te3有很多原子層,原子層通過稱為范德華力的弱鍵結(jié)合在一起。它還表現(xiàn)出類似于半金屬的特性(帶隙為 0.2 至 0.3 eV),并且具有約 620°C 的高熔點(diǎn)。

這些特征表明在Sb2Te3和MoS2之間可能形成范德華界面以抑制費(fèi)米能級(jí)釘扎(FLP)現(xiàn)象。因此,確定通過使用Sb2Te3,可以同時(shí)實(shí)現(xiàn)高耐熱性和低接觸電阻。

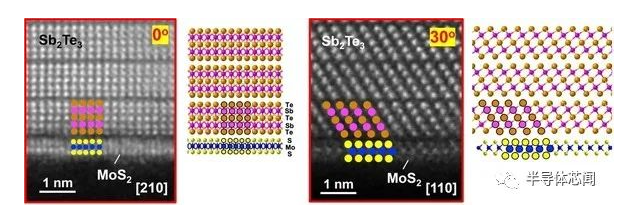

因此,這一次,使用濺射法在單層MoS2上形成Sb2Te3膜。然后,通過透射電子顯微鏡(TEM)確認(rèn)在Sb2Te3/MoS2接觸界面處形成了范德華界面。

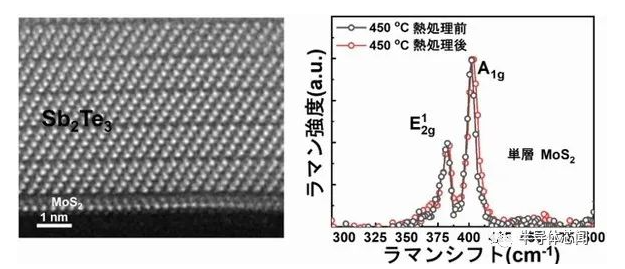

還研究了Sb2Te3/MoS2層壓膜結(jié)構(gòu)的耐熱性。拉曼光譜分析證實(shí),MoS2單層結(jié)構(gòu)在熱處理前后均保持不變。還證實(shí),即使在 450°C 的熱處理后,Sb2Te3/MoS2層壓膜結(jié)構(gòu)也保持良好的結(jié)晶度和范德華界面。

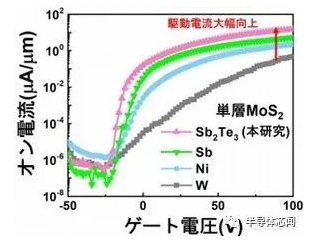

該研究小組還研究了Sb2Te3/MoS2范德瓦爾斯界面形成對(duì)晶體管特性的影響。結(jié)果發(fā)現(xiàn),具有Sb2Te3電極的晶體管的驅(qū)動(dòng)電流比使用Sb、Ni、W等作為接觸材料時(shí)高4至30倍。事實(shí)上,當(dāng)測(cè)量MoS2晶體管的接觸電阻時(shí),使用Sb2Te3電極的晶體管的接觸電阻值比使用Sb電極的晶體管低約一個(gè)數(shù)量級(jí)。

未來,課題組將致力于p型TMDC晶體管的低接觸電阻技術(shù)開發(fā),旨在通過串聯(lián)n型和p型TMDC晶體管來制造CMOS。

臺(tái)積電將帶來全球第一個(gè)2D納米片晶體管

臺(tái)積電工程師與臺(tái)灣兩所大學(xué)合作,將在今年的國(guó)際電子器件會(huì)議 (IEDM) 上報(bào)告世界上第一個(gè)由二維半導(dǎo)體材料制成的納米片柵環(huán)晶體管。

硅納米片晶體管或又名納米帶提供改進(jìn)的靜電控制和相對(duì)較高的驅(qū)動(dòng)電流,并在 3nm 制造工藝中實(shí)施。

根據(jù)即將推出的 IEDM 計(jì)劃的亮點(diǎn),臺(tái)積電已經(jīng)展示了在納米片晶體管中使用過渡金屬二硫?qū)倩飭螌幼鳛榘雽?dǎo)體通道的可能性。在這種情況下,它是二硫化鉬

與硅和自旋軌道耦合相比,這種二維材料可以具有增強(qiáng)的電子遷移率,從而產(chǎn)生自旋電子計(jì)算的可能性。

柵極寬度為 40nm 的晶體管在 1V 的 Vds 下產(chǎn)生每微米 410 微安的驅(qū)動(dòng)電流。期望通過堆疊設(shè)備來增加驅(qū)動(dòng)電流。

臺(tái)積電領(lǐng)導(dǎo)的團(tuán)隊(duì)將報(bào)告制造此類晶體管的集成流程,但優(yōu)化性能仍有待完成。

TSMC 論文#34.5首次展示 GAA 單層 MoS2 納米片 nFET……是第 68 屆年度 IEDM 的亮點(diǎn)之一。

在論文 #7.4 中,在 EOT 為 1 nm 的單層 MoS2 頂柵 nFET 中接近理想的亞閾值擺動(dòng)中,臺(tái)積電領(lǐng)導(dǎo)的團(tuán)隊(duì)描述了鉿基電介質(zhì)與 MoS2 的集成,以構(gòu)建頂柵 nFET 創(chuàng)建可堆疊系統(tǒng). 亞閾值電壓擺幅小于70mV/dec。這表明當(dāng)晶體管關(guān)閉時(shí)泄漏電流較低。

1納米以下制程重大突破!臺(tái)積電官宣「鉍」密武器

IBM 剛剛官宣研發(fā)2nm芯片不久,臺(tái)積電再次發(fā)起了挑戰(zhàn)! 臺(tái)積電取得1nm以下制程重大突破,不斷地挑戰(zhàn)著物理極限。 近日,臺(tái)大與臺(tái)積電、美國(guó)麻省理工學(xué)院合作研究發(fā)現(xiàn)二維材料結(jié)合「半金屬鉍(Bi)」能達(dá)極低電阻,接近量子極限。 這項(xiàng)研究成果由臺(tái)大電機(jī)系暨光電所教授吳志毅,與臺(tái)灣積體電路和MIT研究團(tuán)隊(duì)共同完成,已在國(guó)際期刊Nature上發(fā)表,有助實(shí)現(xiàn)半導(dǎo)體1nm以下制程挑戰(zhàn)。

目前半導(dǎo)體主流制程進(jìn)展到5nm和3nm節(jié)點(diǎn)。 晶片單位面積能容納的電晶體數(shù)目,已將逼近半導(dǎo)體主流材料「硅」的物理極限,晶片效能也無法再逐年顯著提升。 近年科學(xué)界積極尋找能取代硅的二維材料,挑戰(zhàn)1nm以下的制程,卻苦于無法解決二維材料高電阻及低電流等問題。 臺(tái)大、臺(tái)積電和MIT自2019年展開了長(zhǎng)達(dá)1年半的跨國(guó)合作,終于找到了這把key。

這個(gè)重大突破先由MIT團(tuán)隊(duì)發(fā)現(xiàn)在「二維材料」上搭配「半金屬鉍(Bi)」的電極,能大幅降低電阻并提高傳輸電流。 臺(tái)積電技術(shù)研究部門則將「鉍(Bi)沉積制程」進(jìn)行優(yōu)化,最后臺(tái)大團(tuán)隊(duì)運(yùn)用「氦離子束微影系統(tǒng)」將元件通道成功縮小至納米尺寸,終于獲得突破性的研究成果。 吳志毅教授說明,在使用「鉍(Bi)」為「接觸電極」的關(guān)鍵結(jié)構(gòu)后,二維材料電晶體的效能,不但與「硅基半導(dǎo)體」相當(dāng),又有潛力與目前主流的硅基制程技術(shù)相容,有助于未來突破「摩爾定律」極限。

研究成果能替下世代晶片,提供省電、高速等絕佳條件,未來可望投入人工智能、電動(dòng)車、疾病預(yù)測(cè)等新興科技應(yīng)用。

敬請(qǐng)關(guān)注電子技術(shù)應(yīng)用2023年2月22日==>>商業(yè)航天研討會(huì)<<