線邊緣粗糙度(LER)如何影響先進(jìn)節(jié)點(diǎn)上半導(dǎo)體的性能

2023-06-12

作者:Coventor(泛林集團(tuán)旗下公司)半導(dǎo)體工藝與整合團(tuán)隊(duì)成員Yu De Chen

來(lái)源:泛林集團(tuán)

介紹

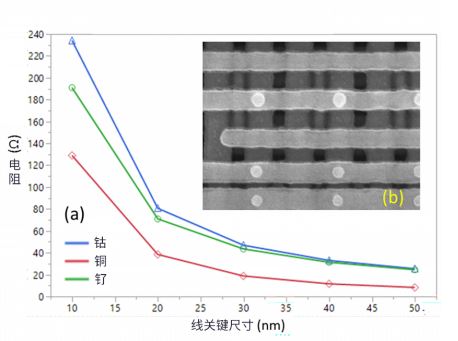

由后段制程(BEOL)金屬線寄生電阻電容(RC)造成的延遲已成為限制先進(jìn)節(jié)點(diǎn)芯片性能的主要因素[1]。減小金屬線間距需要更窄的線關(guān)鍵尺寸(CD)和線間隔,這會(huì)導(dǎo)致更高的金屬線電阻和線間電容。圖1對(duì)此進(jìn)行了示意,模擬了不同后段制程金屬的線電阻和線關(guān)鍵尺寸之間的關(guān)系。即使沒(méi)有線邊緣粗糙度(LER),該圖也顯示電阻會(huì)隨著線寬縮小呈指數(shù)級(jí)增長(zhǎng)[2]。為緩解此問(wèn)題,需要在更小的節(jié)點(diǎn)上對(duì)金屬線關(guān)鍵尺寸進(jìn)行優(yōu)化并選擇合適的金屬材料。

除此之外,線邊緣粗糙度也是影響電子表面散射和金屬線電阻率的重要因素。圖1(b)是典邏輯5nm后段制程M2線的掃描電鏡照片,可以看到明顯的邊緣粗糙度。最近,我們使用虛擬工藝建模,通過(guò)改變粗糙度振幅(RMS)、相關(guān)長(zhǎng)度、所用材料和金屬線關(guān)鍵尺寸,研究了線邊緣粗糙度對(duì)線電阻的影響。

圖1:(a) 線電阻與線關(guān)鍵尺寸的關(guān)系;(b) 5nm M2的掃描電鏡俯視圖(圖片來(lái)源:TechInsights)

實(shí)驗(yàn)設(shè)計(jì)與執(zhí)行

在晶圓廠里,通過(guò)改變線關(guān)鍵尺寸和金屬來(lái)進(jìn)行線邊緣粗糙度變化實(shí)驗(yàn)很困難,也需要花費(fèi)很多時(shí)間和金錢。由于光刻和刻蝕工藝的變化和限制,在硅晶圓上控制線邊緣粗糙度也很困難。因此,虛擬制造也許是一個(gè)更直接和有效的方法,因?yàn)樗梢浴疤摂M地”生成具有特定線邊緣粗糙度的金屬線結(jié)構(gòu),進(jìn)而計(jì)算出相應(yīng)顯粗糙度條件下金屬的電阻率。

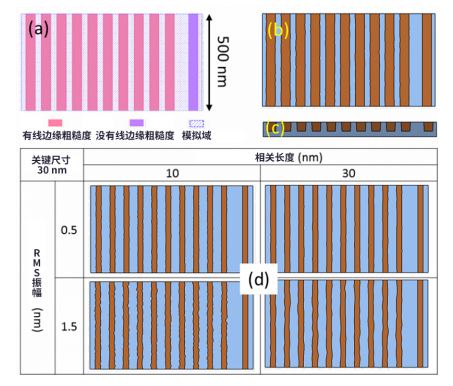

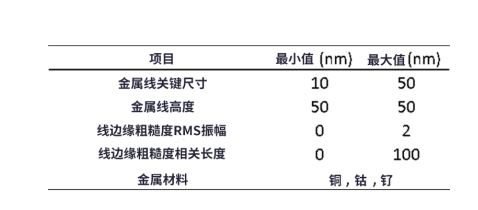

圖2(a)顯示了使用虛擬半導(dǎo)體建模平臺(tái) (SEMulator3D?) 模擬金屬線邊緣粗糙度的版圖設(shè)計(jì)。圖2(b)和2(c)顯示了最終的虛擬制造結(jié)構(gòu)及其模擬線邊緣粗糙度的俯視圖和橫截面圖。通過(guò)設(shè)置具體的粗糙度振幅(RMS)和相關(guān)長(zhǎng)度(噪聲頻率)值,可以在虛擬制造的光刻步驟中直接修改線邊緣粗糙度。圖2(d)顯示了不同線邊緣粗糙度條件的簡(jiǎn)單實(shí)驗(yàn)。圖中不同RMS振幅和相關(guān)長(zhǎng)度設(shè)置條件下,金屬的線邊緣展示出了不同的粗糙度。這些數(shù)據(jù)由SEMulator3D的虛擬實(shí)驗(yàn)仿真生成。為了系統(tǒng)地研究不同的關(guān)鍵尺寸和材料及線邊緣粗糙度對(duì)金屬線電阻的影響,使用了表1所示的實(shí)驗(yàn)條件進(jìn)行結(jié)構(gòu)建模,然后從相應(yīng)結(jié)構(gòu)中提取相應(yīng)條件下的金屬線電阻。需要說(shuō)明的是,為了使實(shí)驗(yàn)更為簡(jiǎn)單,模擬這些結(jié)構(gòu)時(shí)沒(méi)有將內(nèi)襯材料納入考慮。

圖2:(a) 版圖設(shè)計(jì);(b) 生成的典型金屬線俯視圖;(c) 金屬線的橫截面圖;(d) 不同RMS和相關(guān)長(zhǎng)度下的線邊緣粗糙度狀態(tài)

表1: 實(shí)驗(yàn)設(shè)計(jì)分割條件

實(shí)驗(yàn)設(shè)計(jì)結(jié)果與分析

為了探究線邊緣粗糙度對(duì)金屬線電阻的影響,用表1所示條件完成了約1000次虛擬實(shí)驗(yàn)設(shè)計(jì)。從這些實(shí)驗(yàn)中,我們了解到:

1.當(dāng)相關(guān)長(zhǎng)度較小且存在高頻噪聲時(shí),電阻受到線邊緣粗糙度的影響較大。

2.線關(guān)鍵尺寸較小時(shí),電阻受線邊緣粗糙度RMS振幅和相關(guān)長(zhǎng)度的影響。

3.在所有線關(guān)鍵尺寸和線邊緣粗糙度條件下,應(yīng)選擇特定的金屬來(lái)獲得最低的絕對(duì)電阻值。

結(jié)論

由于線邊緣粗糙度對(duì)較小金屬線關(guān)鍵尺寸下的電阻有較大影響,線邊緣粗糙度控制在先進(jìn)節(jié)點(diǎn)將變得越來(lái)越重要。在工藝建模分割實(shí)驗(yàn)中,我們通過(guò)改變金屬線關(guān)鍵尺寸和金屬線材料研究了線邊緣粗糙度對(duì)金屬線電阻的影響。

在EUV(極紫外)光刻中,由于大多數(shù)EUV設(shè)備測(cè)試成本高且能量密度低,關(guān)鍵尺寸均勻性和線邊緣粗糙度可能會(huì)比較麻煩。在這種情況下,可能需要對(duì)光刻顯影進(jìn)行改進(jìn),以盡量降低線邊緣粗糙度。這些修改可以進(jìn)行虛擬測(cè)試,以降低顯影成本。新的EUV光刻膠方法(例如泛林集團(tuán)的干膜光刻膠技術(shù))也可能有助于在較低的EUV曝光量下降低線邊緣粗糙度。

在先進(jìn)節(jié)點(diǎn)上,需要合適的金屬線材料選擇、關(guān)鍵尺寸優(yōu)化和光刻膠顯影改進(jìn)來(lái)減小線邊緣粗糙度,進(jìn)而減少由于電子表面散射引起的線電阻升高。未來(lái)的節(jié)點(diǎn)上可能還需要額外的線邊緣粗糙度改進(jìn)工藝(光刻后)來(lái)減少線邊緣粗糙度引起的電阻。

參考資料

[1] Chen, H. C., Fan, S. C., Lin, J. H., Cheng, Y. L., Jeng, S. P., & Wu, C. M. (2004)。 The impact of scaling on metal thickness for advanced back end of line interconnects. Thin solid films, 469, 487-490.

[2] van der Veen, M. H., Heyler, N., Pedreira, O. V., Ciofi, I., Decoster, S., Gonzalez, V. V., … & T?kei, Z. (2018, June)。 Damascene benchmark of Ru, Co and Cu in scaled dimensions. In 2018 IEEE International Interconnect Technology Conference (IITC) (pp. 172-174)。 IEEE.

[3] Techinsights TSMC 5nm logic tear down report.

[4] http://www.coventor.com/products/semulator3d