晶圓的另一面:背面供電領(lǐng)域的最新發(fā)展

2023-09-08

作者:泛林集團 Semiverse? Solutions 半導(dǎo)體和工藝整合工程師 Sandy Wen

來源:泛林集團

在我從事半導(dǎo)體設(shè)備的職業(yè)生涯之初,晶圓背面是個麻煩問題。當時發(fā)生了一件令我記憶深刻的事:在晶圓傳送的過程中,幾片晶圓從機器人刀片上飛了出來。收拾完殘局后,我們想到,可以在晶圓背面沉積各種薄膜,從而降低其摩擦系數(shù)。放慢晶圓傳送速度幫助我們解決了這個問題,但我們的客戶經(jīng)理不太高興,因為他們不得不向客戶解釋由此導(dǎo)致的產(chǎn)量減少的原因。

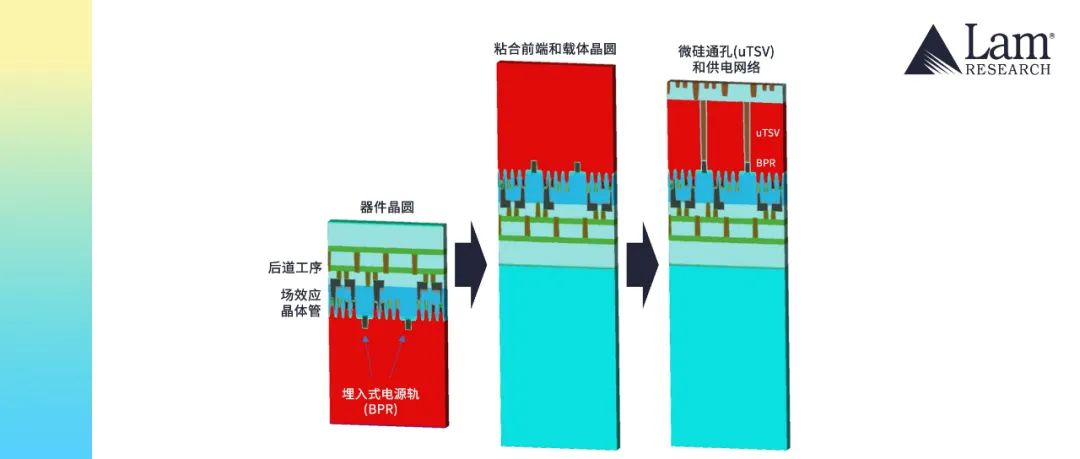

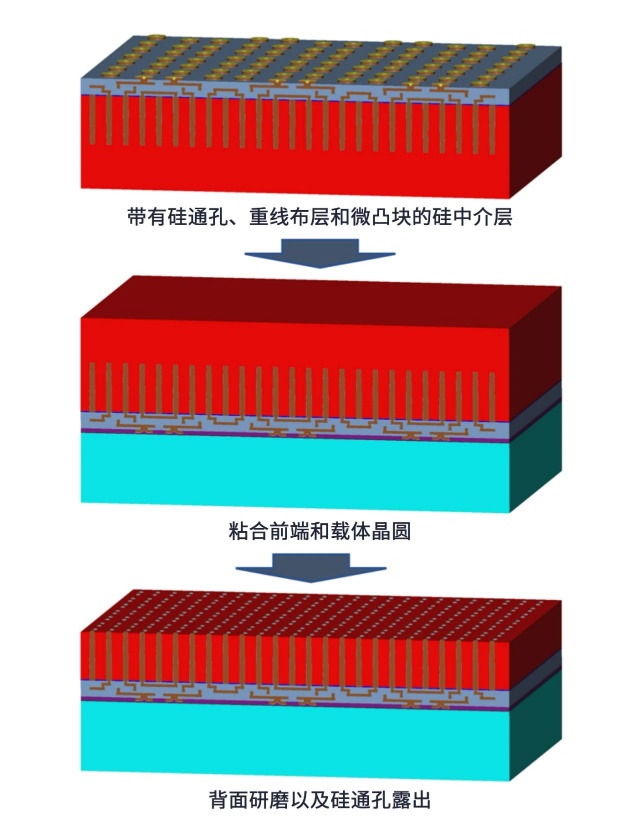

盡管初識晶圓背面的過程不太順利,但當2010年代早期Xilinx Virtex-7系列FPGA發(fā)布時,我開始更加關(guān)注這個領(lǐng)域。Xilinx的產(chǎn)品是首批采用“堆疊硅互連技術(shù)”的異構(gòu)集成的FPGA[1]。該技術(shù)使用了在不同的FPGA組件之間傳遞電信號或電力的硅中介層,這一中介層通過創(chuàng)建部分通過硅晶圓的硅通孔 (TSV) 并在頂部創(chuàng)建信號重布線層而成形。通過對晶圓背面進行工藝處理,連接硅通孔的兩端:晶圓的正面暫時粘到一個載體晶圓上,然后倒置硅中介層進行工藝處理,隨后使用背面研磨和刻蝕來暴露硅通孔。Xilinx產(chǎn)品推出時,我已經(jīng)離開這個行業(yè),回到了研究生院。在課堂上,硅通孔的金屬化是個熱門話題,而隨著異構(gòu)集成不斷發(fā)展,晶圓背面也在工程師中成為了更有意思的話題。

圖1:硅中介層的工藝處理。通孔和初始金屬化之后,研磨晶圓背面直至到達通孔

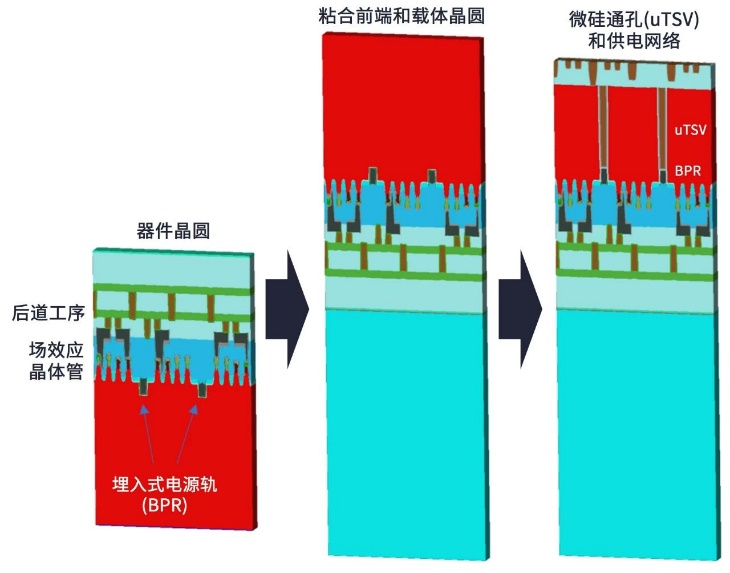

雖然Xilinx FPGA使用了硅中介層來處理信號傳輸和帶寬要求,但去除中介層、直接使用晶圓背面進行電氣布線的做法會更有前瞻性。背面供電是“背面”架構(gòu)的示例之一,它的供電不是來源于傳統(tǒng)的晶圓正面的后道工序,而是背面。這種架構(gòu)可能可以減少電源軌和有源器件之間的電壓降。作為背面架構(gòu)的示例,imec正嘗試在鰭片架構(gòu)中使用埋入式電源軌[2]。在imec的工藝流程中,導(dǎo)軌位于鰭片之間,類似DRAM(動態(tài)隨機存取存儲器)埋入式字線。為了信號傳輸建成后道工序后,在器件晶圓的背面創(chuàng)建硅通孔,連通埋入式導(dǎo)軌。為了供電也可以在背面進行進一步的互連。

圖2:參考資料[2],使用埋入式電源軌進行背面供電(不按比例)

至少出于性能原因,器件晶圓背面的空間看起來很有發(fā)展?jié)摿Α0央娫窜墢那岸艘频奖趁婵梢跃徑饩A正面的擁塞,實現(xiàn)單元微縮并減少電壓降。領(lǐng)先的半導(dǎo)體邏輯企業(yè)深知背面供電的優(yōu)勢,正積極開發(fā)背面分布網(wǎng)絡(luò)。2021年年中,英特爾宣布將使用公司的“PowerVia”技術(shù)進行晶背供電;臺積電也計劃在他們下一節(jié)點的技術(shù)中使用埋入式電源軌[3]。我們期待看到晶圓背面的未來發(fā)展。

參考資料:

[1] K. Saban. “Xilinx Stacked Silicon Interconnect Technology Delivers Breakthrough FPGA Capacity, Bandwidth, and Power Efficiency”, Xilinx WP380, 2012.

[2] J. Ryckaert et al., “Extending the roadmap beyond 3nm through system scaling boosters: A case study on Buried Power Rail and Backside Power Delivery,” 2019 Electron Devices Technology and Manufacturing Conference (EDTM), 2019, pp. 50-52, doi: 10.1109 / EDTM. 2019. 8731234.

[3] D. O’Laughlin, “Backside Power Delivery and Bold Bets at Intel”, https://www.fabricatedknowledge.com/p/backside-power-delivery-and-bold