8月6日消息,在近日的英特爾財(cái)報(bào)電話會(huì)議上,英特爾CEO帕特·基辛格(Pat Gelsinger)透露,全球第二臺(tái)High NA (高數(shù)值孔徑)EUV光刻機(jī)即將進(jìn)入英特爾位于美國(guó)奧勒岡州的晶圓廠。

ASML此前在二季度財(cái)報(bào)會(huì)議上也表示,該公司已經(jīng)開(kāi)始向客戶(hù)出貨其第二臺(tái)High NA EUV光刻機(jī),但是并未指出是哪家客戶(hù)。現(xiàn)在來(lái)看,這家客戶(hù)正是英特爾。

資料顯示,ASML的第一代High NA EUV(EXE:5000)的分辨率為 8nm,可以實(shí)現(xiàn)比現(xiàn)有EUV光刻機(jī)小1.7倍物理特征的微縮,從將單次曝光的晶體管密度提高2.9倍,可以使芯片制造商能夠簡(jiǎn)化其制造流程。并且,EXE:5000每小時(shí)可光刻超過(guò) 185 個(gè)晶圓,與已在大批量制造中使用的 NXE 系統(tǒng)相比還有所增加。ASML還制定了到 2025 年推出的第二代High NA EUV光刻機(jī)將產(chǎn)能提高到每小時(shí) 220 片晶圓的路線圖,確保將High NA EUV光刻機(jī)集成到芯片工廠對(duì)于芯片制造商來(lái)說(shuō)在經(jīng)濟(jì)性上至關(guān)重要。根據(jù)此前的爆料顯示,High NA EUV的售價(jià)高達(dá)3.5億歐元一臺(tái)。

眾所周知,英特爾與ASML合作了數(shù)十年時(shí)間,推動(dòng)了光刻技術(shù)從 193nm浸沒(méi)式光刻技術(shù)發(fā)展到 EUV,但出于成本考慮,英特爾選擇不在其 10nm 工藝(相當(dāng)于臺(tái)積電6nm)中使用該技術(shù)。相反,英特爾選擇使用標(biāo)準(zhǔn)深紫外 (DUV) 光刻機(jī)進(jìn)行四重圖案化,需要對(duì)單個(gè)芯片層進(jìn)行四次 DUV 曝光,而不是使用 EUV 進(jìn)行單次曝光。結(jié)果,英特爾在良率方面遇到了重重困難,導(dǎo)致其10nm工藝推遲了五年。這也使得英特爾被臺(tái)積電、三星等率先使用EUV光刻機(jī)的廠商持續(xù)超越。

因此,在英特爾CEO基辛格提出“IDM 2.0”戰(zhàn)略后,英特爾便迅速重新聚焦于尖端制程工藝的提升,提出的了四年五個(gè)工藝節(jié)點(diǎn)的計(jì)劃,希望在2025年憑借Intel 18A實(shí)現(xiàn)對(duì)于臺(tái)積電2nm工藝的超越。與此同時(shí),英特爾還希望通過(guò)率先采用High NA EUV光刻機(jī)來(lái)實(shí)現(xiàn)對(duì)于臺(tái)積電等競(jìng)爭(zhēng)對(duì)手的持續(xù)領(lǐng)先。最終在2030年前實(shí)現(xiàn)英特爾代工業(yè)務(wù)實(shí)現(xiàn)收支平衡的運(yùn)營(yíng)利潤(rùn)率,并成為全球第二大晶圓代工廠。

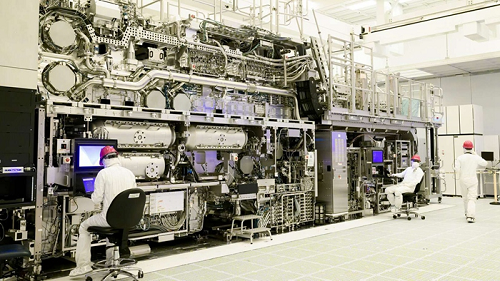

為此,英特爾在2023年12月已率先拿下了全球首臺(tái)High NA EUV光刻機(jī),并開(kāi)始在英特爾俄勒岡州晶圓廠安裝。一套High NA EUV光刻系統(tǒng)的大小等同于一臺(tái)雙層巴士,重量更高達(dá)150噸,相當(dāng)于兩架空中客車(chē)A320客機(jī),全套系統(tǒng)需要43 個(gè)貨運(yùn)集裝箱內(nèi)的 250個(gè)貨箱來(lái)裝運(yùn),裝機(jī)時(shí)間預(yù)計(jì)需要250名工程人員、歷時(shí)6個(gè)月才能安裝完成,不僅價(jià)格高昂也相當(dāng)耗時(shí)。

今年4月18日,英特爾公司正式宣布在俄勒岡州希爾斯伯勒的研發(fā)基地達(dá)成了先進(jìn)半導(dǎo)體制造領(lǐng)域的一個(gè)重要里程碑,完成了業(yè)界首個(gè)商用High NA EUV光刻機(jī)的組裝。

根據(jù)英特爾的計(jì)劃,High NA EUV光刻機(jī)將會(huì)首先會(huì)被用到Intel 18A的相關(guān)測(cè)試,以積累相關(guān)經(jīng)驗(yàn),最終會(huì)被用于Intel 14A的量產(chǎn)。

此前的報(bào)道顯示,ASML已獲得十多臺(tái)High NA EUV光刻機(jī)的訂單,客戶(hù)包括臺(tái)積電、三星、英特爾、美光及SK海力士。ASML CEO Christophe Fouquet指出,DRAM芯片制造商,可能會(huì)在2025或2026年開(kāi)始使用High NA EUV設(shè)備。