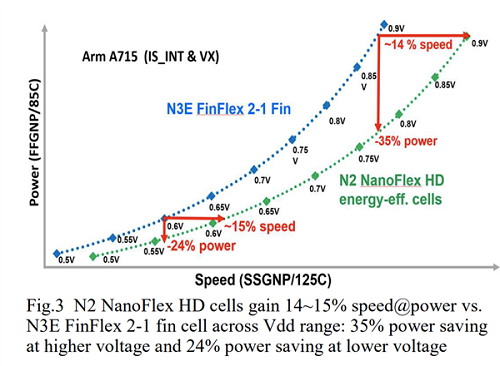

12月15日消息,IEDM 2024大會(huì)上,臺(tái)積電首次披露了N2 2nm工藝的關(guān)鍵技術(shù)細(xì)節(jié)和性能指標(biāo):對(duì)比3nm,晶體管密度增加15%,同等功耗下性能提升15%,同等性能下功耗降低24-35%。

臺(tái)積電2nm首次引入全環(huán)繞柵極(GAA)納米片晶體管,有助于調(diào)整通道寬度,平衡性能與能效。

新工藝還增加了NanoFlex DTCO(設(shè)計(jì)技術(shù)聯(lián)合優(yōu)化),可以開發(fā)面積最小化、能效增強(qiáng)的更矮單元,或者性能最大化的更高單元。

此外還有第三代偶極子集成,包括N型、P型,從而支持六個(gè)電壓閾值檔(6-Vt),范圍200mV。

通過種種改進(jìn),N型、P型納米片晶體管的I/CV速度分別提升了70%、110%。

對(duì)比傳統(tǒng)的FinFET晶體管,新工藝的納米片晶體管可以在0.5-0.6V的低電壓下,獲得顯著的能效提升,可以將頻率提升大約20%,待機(jī)功耗降低大約75%。

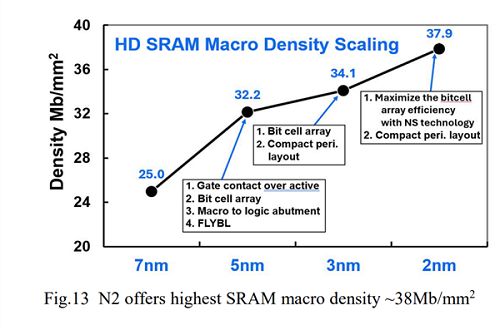

SRAM密度也達(dá)到了創(chuàng)紀(jì)錄的新高,每平方毫米約38Mb。

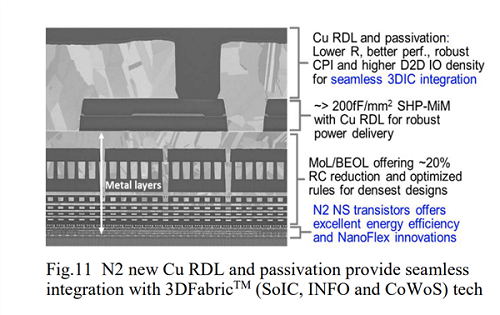

此外,臺(tái)積電2nm還應(yīng)用了全新的MOL中段工藝、BEOL后段工藝,電阻降低20%,能效更高。

值得一提的是,第一層金屬層(M1)現(xiàn)在只需一步蝕刻(1P1E)、一次EVU曝光即可完成,大大降低了復(fù)雜度、光罩?jǐn)?shù)量。

針對(duì)高性能計(jì)算應(yīng)用,臺(tái)積電2nm還引入了超高性能的SHP-MiM電容,容量大約每平方毫米200fF,可以獲得更高的運(yùn)行頻率。

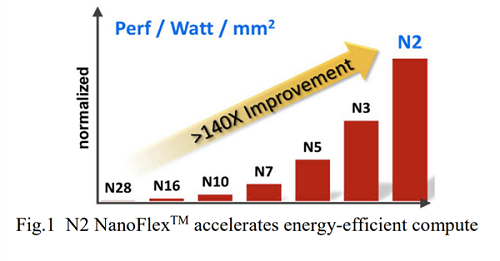

按照臺(tái)積電的說法,28nm工藝以來,歷經(jīng)六代工藝改進(jìn),單位面積的能效比已經(jīng)提升了超過140倍!