??? 摘 要: 介紹了等精度" title="等精度">等精度頻率測量方法的原理及誤差分析,利用基于FPGA的SoPC技術(shù)在QuartusⅡ5.0環(huán)境下用VHDL語言實(shí)現(xiàn)了等精度頻率計" title="等精度頻率計">等精度頻率計的軟核IP Core設(shè)計,并在相應(yīng)的開發(fā)平臺上作了驗(yàn)證。

??? 關(guān)鍵詞: FPGA? SoPC? 等精度? IP Core

?

??? 頻率測量是電子測量技術(shù)中最基本的測量之一。在現(xiàn)代信號分析和處理領(lǐng)域中,高精度的頻率測量有非常重要的意義。

??? 常用的測頻" title="測頻">測頻方法有計數(shù)法和周期法。計數(shù)法是在預(yù)制的閘門時間TW內(nèi)測量被測信號的脈沖個數(shù)Nx,進(jìn)行換算得出被測信號的頻率為fx=Nx/:TW。這種測量方法的測量精度" title="測量精度">測量精度取決于閘門時間和被測信號頻率。當(dāng)被測信號頻率較低時將產(chǎn)生較大誤差,除非閘門時間取得很大。周期法是在被測信號的一個周期Tx內(nèi),測量標(biāo)準(zhǔn)信號(周期TC)ΔFS/FS的周期個數(shù)NS,進(jìn)行換算得出被測信號的頻率為fx=fC/NS。這種測量方法的測量精度取決于被測信號的周期和計時精度。本文采用的測量方法克服了以上兩種方法的缺點(diǎn),測頻精度與被測信號的頻率大小無關(guān),從而保證了頻率的等精度測量。

??? 隨著FPGA和SoPC技術(shù)的迅速發(fā)展,在單芯片上實(shí)現(xiàn)的功能越來越復(fù)雜。這就使得設(shè)計師的工作量非常大,而IP Core的復(fù)用可以大大減少工作量,從而減小設(shè)計的復(fù)雜性,提高產(chǎn)品的設(shè)計效率。本文根據(jù)等精度頻率測量的原理,用VHDL語言實(shí)現(xiàn)了等精度頻率計的IP Core,實(shí)現(xiàn)軟核的重用。

1 等精度頻率測量

1.1 等精度頻率測量原理

??? 基于傳統(tǒng)測頻原理的頻率計的測量精度將隨被測信號頻率的下降而降低,在實(shí)用中有較大的局限性。而等精度頻率計不但具有較高的測量精度,并且在整個頻率區(qū)域保持恒定的測量精度。

??? 等精度頻率測量用被測信號的多周期而不是單周期作門控" title="門控">門控信號;門控信號周期數(shù)可根據(jù)被測頻率的大小自動調(diào)節(jié),使計數(shù)值Ns保持不變,從而實(shí)現(xiàn)等精度測量。

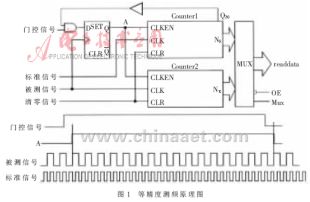

??? 等精度測頻的原理框圖如圖1所示。圖中預(yù)置門控信號是寬度為Tpr的一個脈沖,Counterl和Counter2是兩個可控計數(shù)器,標(biāo)準(zhǔn)頻率信號從Counter1的時鐘輸入端CLK輸入,其頻率為Fs;經(jīng)整形后的被測信號從Counter2的時鐘輸入端CLK輸入,設(shè)其實(shí)際頻率為Fxe,測量頻率為Fx。

???????????????????????????????

??? 當(dāng)預(yù)置門控信號為高電平時,經(jīng)整形后的被測信號的上沿通過D觸發(fā)器的Q端同時啟動計數(shù)器Counter1和Counter2。Counter1、Counter2分別對被測信號(頻率為Fx)和標(biāo)準(zhǔn)頻率信號(頻率為Fs)同時計數(shù)。當(dāng)預(yù)置門信號為低電平時,隨后而至的被測信號的上沿將使這兩個計數(shù)器同時關(guān)閉。設(shè)在一次預(yù)置門時間Tpr中對被測信號計數(shù)值為Nx;對標(biāo)準(zhǔn)頻率信號的計數(shù)值為Ns,則下式成立:

???

1.2 誤差分析

??? 設(shè)所測頻率值為Fx,其真實(shí)值為Fxe,標(biāo)準(zhǔn)頻率為Fs。在一次測量中,由于計數(shù)的起停時間都是由該信號的上跳沿觸發(fā)的,在Tpr時間內(nèi)對Fx的計數(shù)Nx無誤差;在此時間內(nèi),F(xiàn)s的計數(shù)Ns最多相差一個脈沖,即:

???

??? 則下式成立:

??? 根據(jù)相對誤差的公式有:

??? 由上式可以得出以下結(jié)論:

??? (1)相對測量誤差與頻率無關(guān)。

??? (2)增大Tpr或提高Fs,可以增大Ns,減少測量誤差,提高測量精度。

??? (3)標(biāo)準(zhǔn)頻率誤差為ΔFs/Fs。

??? (4)等精度測頻方法測量精度與預(yù)置門寬度和標(biāo)準(zhǔn)頻率有關(guān),與被測信號的頻率無關(guān)。在預(yù)置門時間和常規(guī)測頻閘門時間相同,而被測信號頻率不同的情況下,等精度測量法的測量精度不變,而常規(guī)的直接測頻法精度隨著被測信號頻率的下降而下降。測試電路可采用高頻率穩(wěn)定度和高精度的恒溫可微調(diào)的晶體振蕩器作標(biāo)準(zhǔn)頻率發(fā)生電路。

1.3 等精度頻率計的實(shí)現(xiàn)方法

??? 隨著微電子技術(shù)與工藝的發(fā)展,等精度頻率計的實(shí)現(xiàn)從完全使用小規(guī)模集成電路、單片機(jī)+小規(guī)模集成電路、FPGA+單片機(jī)發(fā)展到基于FPGA的SoPC設(shè)計。小規(guī)模集成電路在實(shí)現(xiàn)乘除運(yùn)算時相當(dāng)復(fù)雜,而單片機(jī)受本身時鐘頻率和若干指令運(yùn)算的限制,測頻速度較慢,無法滿足高速、高精度的測頻要求,同時需要外部分離元件的支持,這增加了系統(tǒng)的復(fù)雜度。采用高集成度、高速的現(xiàn)場可編程門陣列FPGA為實(shí)現(xiàn)高速、高精度的測頻提供了保證。

??? 本系統(tǒng)采用基于FPGA的SoPC技術(shù)實(shí)現(xiàn)等精度頻率測量。基于SoPC的特點(diǎn),本系統(tǒng)具有靈活的設(shè)計方式,體積小、開發(fā)周期短、可裁剪、可擴(kuò)充、可升級,并具備軟硬件在系統(tǒng)可編程的功能。

2 等精度頻率計IP Core

??? 本文主要介紹等精度頻率計的功能模塊設(shè)計,包括任務(wù)邏輯、寄存器文件及Avalon接口的設(shè)計。

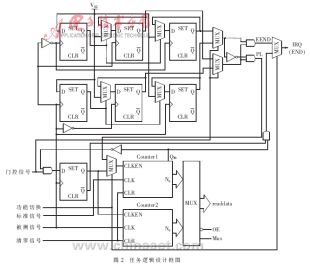

2.1 任務(wù)邏輯

??? 任務(wù)邏輯框圖如圖2所示。任務(wù)邏輯完成用戶定制元件的基本功能。本設(shè)計中任務(wù)邏輯完成頻率測量、脈寬測量及占空比測量三個功能。由于FPGA低偏斜、高負(fù)載的布線資源有限,為了避免高速、高頻率系統(tǒng)時序中潛在的競爭、毛刺、建立和保持時間違反問題,本系統(tǒng)采用同步設(shè)計。然而在實(shí)際運(yùn)用中經(jīng)常出現(xiàn)時鐘選擇和時鐘控制的異步設(shè)計,導(dǎo)致系統(tǒng)產(chǎn)生毛刺和時鐘偏斜及時鐘分析路徑復(fù)雜等問題。為了解決該問題,需將時鐘控制改為觸發(fā)器輸入允許,將時鐘選擇改為獨(dú)立的時鐘分析。

??????????????????

??? 當(dāng)功能切換和門控信號同時為1時,該系統(tǒng)實(shí)現(xiàn)頻率的測量。Counter1和Counter2分別輸出標(biāo)準(zhǔn)頻率數(shù)(Ns)和被測頻率數(shù)(Nx)。考慮到等精度頻率計的精度和速度,該系統(tǒng)選擇標(biāo)準(zhǔn)頻率計數(shù)器計滿20位時產(chǎn)生中斷,同時輸出Ns和Nx。

??? 當(dāng)功能切換為0、門控信號為1時,系統(tǒng)實(shí)現(xiàn)被測時鐘信號的高電平寬度測量(即脈寬測量),并由Counter1輸出其寬度值N1;當(dāng)功能切換和門控信號同時為0時,系統(tǒng)實(shí)現(xiàn)被測時鐘信號的低電平寬度測量,同時由Counter1輸出其寬度值N2,則被測時鐘信號的占空比為: 。

。

??? 功能切換=1時,測頻率;功能切換=0時,測占空比和脈沖寬度。門控信號在測頻率時是門控信號;測占空比時,門控信號=1,測高電平寬度;門控信號=0,測低電平寬度。

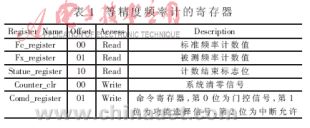

2.2 寄存器文件

??? 寄存器文件提供了任務(wù)邏輯與外界交換信息的途徑。用戶可以通過Avalon接口采用基地址 +地址偏移量的方式來訪問元件內(nèi)部各寄存器。本IP Core內(nèi)部寄存器如表1所示。

??????????????????????????????

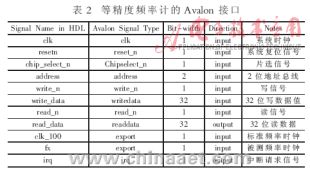

2.3 Avalon接口設(shè)計

??? Avalon接口為寄存器文件提供了一個標(biāo)準(zhǔn)的Avalon前端,它使用Avalon必須的信號來訪問寄存器文件,并且支持任務(wù)邏輯的傳輸類型。 等精度頻率計的Avalon接口信息如表2所示。

???????????????????????????????

3 測試與驗(yàn)證

??? IP Core設(shè)計完成后,利用SoPC Builder搭建一測試該IP Core的系統(tǒng),并在其中加入該IP核。硬件測試結(jié)果如表3所示。

???????????????????????????????

??? 本設(shè)計通過SoPC技術(shù)在FPGA上實(shí)現(xiàn)了等精度頻率計的IP Core設(shè)計。系統(tǒng)采用同步設(shè)計,避免了由時鐘異步導(dǎo)致的時鐘偏斜。

??? 經(jīng)測試證明,該頻率計的測頻范圍為0.1Hz~100MHz,測頻精度恒為百萬分之一,能夠滿足高速度、高精度的測頻要求。本設(shè)計可移植性好、穩(wěn)定性好、精確度高、測頻速度快,達(dá)到設(shè)計要求。

參考文獻(xiàn)

[1] 譚會生,瞿遂春.EDA技術(shù)綜合應(yīng)用實(shí)例與分析.西安:西安電子科技大學(xué)出版社,2004.

[2] 潘松,王國棟.VHDL實(shí)用教程.電子科技大學(xué)出版社,2004.

[3] 莫琳.基于FPGA的等精度頻率計的設(shè)計與實(shí)現(xiàn).現(xiàn)代電子技術(shù),2004.

[4] 毛智德,呂善偉.基于FPGA的等精度頻率計設(shè)計.電子測量技術(shù),2006