0 引言

模數(shù)轉(zhuǎn)換器(ADC)在信號(hào)處理中起了一個(gè)非常重要的作用。在數(shù)字音頻、數(shù)字電視、圖像編碼及頻率合成等領(lǐng)域需要大量的數(shù)據(jù)轉(zhuǎn)換器。由于超大規(guī)模集成電路的尺寸和偏壓不斷減小,模擬器件的精度和動(dòng)態(tài)范圍也不斷降低,對(duì)于實(shí)現(xiàn)高分辨率的ADC是一種挑戰(zhàn)。高階多位Delta-sigma ADC由于不需要采樣保持電路,電路規(guī)模小,可以實(shí)現(xiàn)較高的分辨率,因此在實(shí)際中得到廣泛的應(yīng)用。Delta-sigma ADC采用過(guò)采樣技術(shù)和噪聲整形技術(shù)相結(jié)合,對(duì)量化噪聲雙重抑制,從而實(shí)現(xiàn)高精度模數(shù)轉(zhuǎn)換。在實(shí)際的設(shè)計(jì)中需要根據(jù)設(shè)計(jì)指標(biāo)穩(wěn)定性和動(dòng)態(tài)范圍等進(jìn)行折衷。要實(shí)現(xiàn)大的動(dòng)態(tài)范圍,就需要較高的過(guò)采樣率和多位量化器。為了保持高階DSM的穩(wěn)定性就需要使用多位量化器,而多位量化器會(huì)增加后續(xù)內(nèi)部ADC的設(shè)計(jì)難度。因此,必須仔細(xì)選擇過(guò)采樣率和量化器的位數(shù),以實(shí)現(xiàn)預(yù)期的性能指標(biāo)。本文提出一種三階單環(huán)局部反饋的Delta-sigma調(diào)制器結(jié)構(gòu),利用Richard Schreier的Matlab Delta-sigma調(diào)制器設(shè)計(jì)工具包,推導(dǎo)調(diào)制器傳輸函數(shù),并對(duì)系數(shù)進(jìn)行優(yōu)化,使用Verilog硬件語(yǔ)言對(duì)調(diào)制器進(jìn)行行為級(jí)建模。調(diào)制器的信號(hào)帶寬為32.8kHz,過(guò)采樣率為128,工作時(shí)鐘8.4MHZ,精度16位,可以達(dá)到145dB以上的SNR。

1 Delta-sigma調(diào)制器的原理和結(jié)構(gòu)

△-∑調(diào)制技術(shù)來(lái)自高分辨率的A/D、D/A變換器中的過(guò)取樣△-∑轉(zhuǎn)換技術(shù),利用經(jīng)典自動(dòng)控制理論中負(fù)反饋概念,通過(guò)反饋環(huán)來(lái)提高量化器的有效分辨率并整形其量化噪聲。在對(duì)信號(hào)進(jìn)行過(guò)取樣后,噪聲功率譜幅度降低,并通過(guò)一個(gè)對(duì)輸入呈低通而對(duì)量化噪聲呈現(xiàn)高通的噪聲整形器,將量化噪聲功率的絕大部分移到信號(hào)頻帶之外,從而可通過(guò)濾波有效地抑制噪聲。

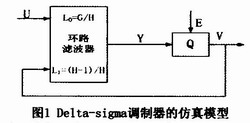

Delta-sigma調(diào)制器的仿真模型可以用圖1來(lái)表示。該系統(tǒng)是一個(gè)雙端輸入、單端輸出的線性系統(tǒng),系統(tǒng)的一個(gè)輸入為外部輸入信號(hào)U,另一個(gè)輸入為量化器的反饋V,輸出則是量化器的輸入Y。

由圖1根據(jù)疊加原理,可知系統(tǒng)的輸出可以表示為

![]()

其中,L0(z)和L1(z)分別是輸入U(xiǎn)(z)和V(z)到輸出Y(z)的傳遞函數(shù)。

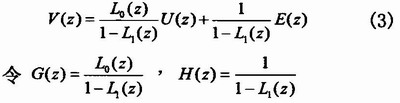

令調(diào)制器量化噪聲為E(z),則調(diào)制器的輸出為

![]()

由式(1)、(2)可得

其中G(z)是信號(hào)傳遞函數(shù)(STF),H(z)是NTF(NTF)。所以

![]()

這種仿真模型將不同結(jié)構(gòu)的Delta-sigma調(diào)制器用同一種模型來(lái)描述。因此,在設(shè)計(jì)調(diào)制器的NTF時(shí)不必考慮調(diào)制器具體的實(shí)現(xiàn)結(jié)構(gòu)。

2 三階單環(huán)DSM結(jié)構(gòu)

2.1 高階穩(wěn)定的調(diào)制器函數(shù)的設(shè)計(jì)

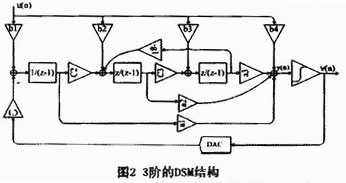

高階Delta-sigma的NTF具有一般形式(5)。從表達(dá)式可以看出,NTF的n個(gè)零點(diǎn)都集中直流頻率處。但是,文獻(xiàn)指出,如果將NTF的零點(diǎn)均勻地分布在信號(hào)基帶中,而不是全都集中在直流頻率處,將對(duì)量化噪聲有更好的整形效果。Delta-sigma調(diào)制器的不穩(wěn)定狀態(tài)主要與調(diào)制器N-TF的帶外增益有關(guān),為了限制NTF的帶外增益,將式(5)所示的NTF的一般表達(dá)式改寫(xiě)成式(6)。

通過(guò)調(diào)整D(z)就可以有效地達(dá)到限制NTF帶外增益的目的。

Delta-sigma調(diào)制器的設(shè)計(jì)重點(diǎn)就是設(shè)計(jì)出使系統(tǒng)穩(wěn)定mSTF和NTF。。在文獻(xiàn)中指出,NTF的極點(diǎn)決定了它的帶外增益,而帶外增益又與系統(tǒng)的噪聲整形性能及穩(wěn)定性密切相關(guān),帶外增益越高,噪聲整形的效果越好,但是帶外增益過(guò)高系統(tǒng)將不能穩(wěn)定,而且?guī)庠鲆嬖礁邉t輸入信號(hào)的穩(wěn)定的范圍越小。所以,對(duì)于3階以上的Delta-sigma調(diào)制器,隨著輸入信號(hào)幅度的增加,調(diào)制器的SNR線性增長(zhǎng),但是當(dāng)輸入的幅度超過(guò)一定值后。調(diào)制器的SNR突然下降,這時(shí)的調(diào)制器就處于不穩(wěn)定的狀態(tài)。NTF的帶外增益決定了輸入信號(hào)幅度和調(diào)制器輸出SNR之間的一對(duì)矛盾關(guān)系。

在調(diào)制器階數(shù)、過(guò)采樣率以及調(diào)制器位數(shù)確定的情況下,調(diào)制器NTF設(shè)計(jì)的關(guān)鍵問(wèn)題是,找出調(diào)制器能夠穩(wěn)定所對(duì)應(yīng)的輸入范圍。最大SNR所對(duì)應(yīng)的輸入范圍就是調(diào)制器能夠穩(wěn)定所對(duì)應(yīng)的輸入范圍。

2.2 改進(jìn)的DSM結(jié)構(gòu)圖

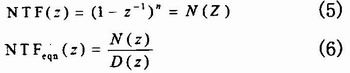

實(shí)現(xiàn)傳輸函數(shù)的拓?fù)浣Y(jié)構(gòu)不是唯一的,是多種形式的,一般來(lái)說(shuō)有四種結(jié)構(gòu)使用最為普遍CIFB(cascade-integrator-feedback)、CRFB(cascade-resonator-feedback)、CIFF(cascade-integrator-feedforward)、CRFF(cascade-resonator-feedforward)。如果不需要經(jīng)過(guò)零點(diǎn)優(yōu)化,可以采用CIFB和CIFF的結(jié)構(gòu),需要零點(diǎn)經(jīng)過(guò)優(yōu)化可采用CRFB和CRFF結(jié)構(gòu)。本文是高精度調(diào)制器的設(shè)計(jì),而經(jīng)過(guò)零點(diǎn)優(yōu)化的可以得到更好的噪聲整形,實(shí)現(xiàn)更高的精度,而CRFF相對(duì)CRFB結(jié)構(gòu)在電路設(shè)計(jì)方面具有結(jié)構(gòu)更為簡(jiǎn)單和電路規(guī)模更小的優(yōu)勢(shì),所以采用CRFF結(jié)構(gòu),如圖2。

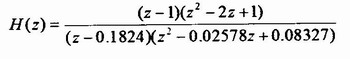

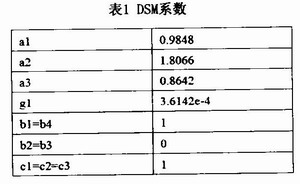

由圖可以看出,輸入信號(hào)在比較器前與前饋信號(hào)直接相加,實(shí)現(xiàn)了STF為1,因此數(shù)字濾波器可以不需要考慮基帶補(bǔ)償;al-a3前饋方式實(shí)現(xiàn)NTF的極點(diǎn),降低了積分器輸出的幅度;第三級(jí)積分器輸出通過(guò)g反饋給第二級(jí)積分器,即局部反饋(LFB),這在NTF中引入了共軛零點(diǎn),挺高了基帶SNR。根據(jù)高階穩(wěn)定的調(diào)制器函數(shù)的設(shè)計(jì)方法,設(shè)計(jì)一個(gè)過(guò)采樣率為128和3位量化器的3階調(diào)制器,圖2中的系數(shù)值(a1、a2、a3、a4、bl、b2、b3、b4、cl、c2、c3、g1),由Richard Schreier提供的Matlab Delta-sigma調(diào)制器設(shè)計(jì)工具包可以得出,具體值在表1中給出,表中的數(shù)值用于設(shè)計(jì)NTF和STF的Matlab模型。在實(shí)際的數(shù)字電路實(shí)現(xiàn)時(shí),為了減少芯片面積和設(shè)計(jì)難度避免使用乘法器,所以這些系數(shù)均取2n的近似值,這樣可以用移位相加來(lái)代替乘法。利用Richard Schreier提供的Matlab Delta-sigma調(diào)制器設(shè)計(jì)工具包得到帶外增益為6.1,DSM的NTF為

2.3 Verilog語(yǔ)言行為級(jí)建模

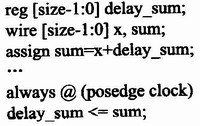

圖2所示的是一種單路差異積分器調(diào)制器,可用延遲積分器和非延遲積分器,以及各種前饋和反饋路徑組合而成。在Matlab結(jié)構(gòu)中對(duì)應(yīng)的積分器轉(zhuǎn)換成Verilog硬件描述框圖的過(guò)程如圖3所示

本文使用Verilog硬件語(yǔ)言來(lái)實(shí)現(xiàn)單回路差異積分調(diào)制器,由時(shí)鐘控制構(gòu)成延遲積分器與非延遲積分器的相加動(dòng)作。assign指令使等式兩邊永遠(yuǎn)處于活動(dòng)狀態(tài),而alwavs指令將會(huì)在時(shí)鐘正好觸發(fā)時(shí)將sum的值存入寄存器delay_sum中,因此,所有的積分器將會(huì)在每一次時(shí)鐘完成時(shí)完成一次累加動(dòng)作。同理,非延遲積分器是由相同的程序代碼組成。實(shí)現(xiàn)延遲積分器的程序部分代碼如下表示:

3 模型的仿真結(jié)果

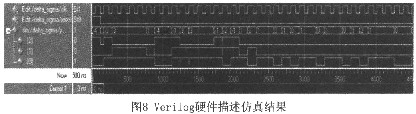

圖3給出的是NTF的極點(diǎn)與零點(diǎn)圖。很明顯,NTF的零點(diǎn)均勻地分布在信號(hào)基帶中,而不是集中在直流頻率處。圖4給出了輸入幅度范圍與SNR。圖5給出了NTF和STF的幅頻響應(yīng)。可以看到,帶內(nèi)信號(hào)的衰減幾乎是0,而圖6顯示噪聲的衰減小于-110dB,滿足帶內(nèi)噪聲的要求。圖7給出了調(diào)制器的頻域特性圖。圖8給出的是在輸入為42000,時(shí)鐘頻率為8.4MHz的verilog硬件描述語(yǔ)言的仿真結(jié)果,可以看出經(jīng)過(guò)2μs后結(jié)果趨于穩(wěn)定。

4 結(jié)論

本文提出一個(gè)用在ADC中的16位的3階8級(jí)量化的三階單環(huán)Delta-sigma調(diào)制器。為了提高電路性能,實(shí)現(xiàn)較高的SNR和DR,減少量化噪聲的影響,在設(shè)計(jì)NTF時(shí)采用前饋方式和局部反饋的結(jié)構(gòu),并進(jìn)行零點(diǎn)優(yōu)化,通過(guò)這些方法優(yōu)化了輸出SNR,提高DR,降低量化噪聲,使得電路對(duì)于量化噪聲有較好的敏感度。根據(jù)仿真結(jié)果,這個(gè)DSM的峰值SNR可以達(dá)到145dB以上,在3階的系統(tǒng)和128的過(guò)采樣率下,達(dá)到相當(dāng)高的SNR,之后用Verilog語(yǔ)言對(duì)調(diào)制器各電路模塊進(jìn)行建模與仿真。