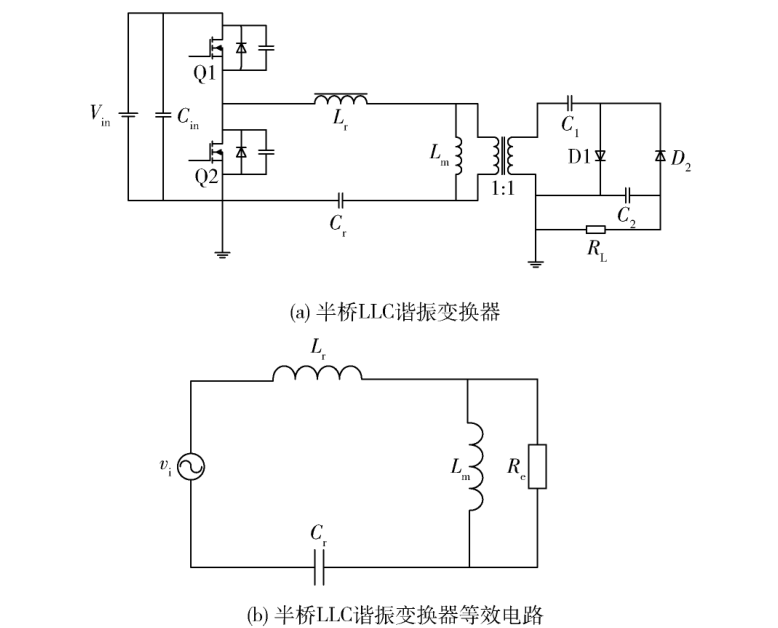

一種高效率行波管高壓電源的設(shè)計(jì)與實(shí)驗(yàn)研究[電源技術(shù)][工業(yè)自動(dòng)化]

發(fā)表于:5/27/2024 3:28:28 PM

用于土壤濕度監(jiān)測(cè)的無(wú)芯片RFID傳感器設(shè)計(jì)[微波|射頻][通信網(wǎng)絡(luò)]

發(fā)表于:5/27/2024 3:28:26 PM

基于深度學(xué)習(xí)的可視化圖表分類方法研究[模擬設(shè)計(jì)][工業(yè)自動(dòng)化]

發(fā)表于:5/27/2024 3:28:20 PM

一起DCS網(wǎng)絡(luò)異常事件分析研究[通信與網(wǎng)絡(luò)][智能電網(wǎng)]

發(fā)表于:5/27/2024 3:28:17 PM

基于Modbus協(xié)議的濕度檢定系統(tǒng)設(shè)計(jì)[測(cè)試測(cè)量][工業(yè)自動(dòng)化]

發(fā)表于:5/27/2024 3:28:14 PM

三種石英晶體諧振器頻率測(cè)試方法對(duì)比分析研究[測(cè)試測(cè)量][工業(yè)自動(dòng)化]

發(fā)表于:5/27/2024 3:28:13 PM

基于Innovus改善芯片繞線資源的電源網(wǎng)絡(luò)布線方法[模擬設(shè)計(jì)][工業(yè)自動(dòng)化]

發(fā)表于:5/27/2024 3:28:10 PM

一種低峰均功率比的數(shù)字梳狀譜模塊設(shè)計(jì)[嵌入式技術(shù)][工業(yè)自動(dòng)化]

發(fā)表于:5/27/2024 3:28:08 PM

基于ADS的微系統(tǒng)電源完整性仿真及優(yōu)化[電源技術(shù)][工業(yè)自動(dòng)化]

發(fā)表于:5/27/2024 3:28:06 PM

基于FPGA的視頻圖像去霧算法的優(yōu)化與實(shí)現(xiàn)[嵌入式技術(shù)][工業(yè)自動(dòng)化]

發(fā)表于:5/27/2024 3:28:00 PM