在處理微弱信號的時候自適應(yīng)濾波器所處的環(huán)境可能是非平穩(wěn)的,,輸入信號的自相關(guān)矩陣和互相關(guān)向量等算法參量將隨時間變化,會對濾波器的收斂跟蹤性能造成較大影響?,F(xiàn)代通信系統(tǒng)發(fā)展到3G,,4G后,幾十甚至上百兆比特每秒的數(shù)據(jù)傳輸速率對自適應(yīng)處理技術(shù)是個極大的挑戰(zhàn),。如何在這類高速環(huán)境中運用自適應(yīng)算法處理高靈敏度信號并使算法保持較低的復(fù)雜度以利于實現(xiàn),,是工程應(yīng)用中必須解決的問題。

由Levinson-Durbin遞推公式得到的自適應(yīng)格型結(jié)構(gòu)以其反射系數(shù)收斂快,,對輸入信號自相關(guān)矩陣的特征值擴散相對惰性,,是解決此類問題的一個優(yōu)良選擇。GALJP(Gradient Adaptive Lattice Joint Processing)是一種梯度自適應(yīng)格型結(jié)構(gòu)和LMS結(jié)構(gòu)組成的聯(lián)合濾波器,,由格型結(jié)構(gòu)對輸入信號進行迅速解耦,,用LMS結(jié)構(gòu)進行自適應(yīng)處理??紤]到實時處理的要求,,采用高度并行的FPGA進行算法實現(xiàn)是一個很好的選擇。但是由于GALJP的結(jié)構(gòu)相對復(fù)雜,,導(dǎo)致其在FPGA中實現(xiàn)的工作頻率不高,。本文以自適應(yīng)噪聲對消為模型,采用流水線技術(shù)和時序重構(gòu)技術(shù)對GALJP算法結(jié)構(gòu)進行改進優(yōu)化,,提出一種改進型RD-GALJP結(jié)構(gòu),。在算法性能影響不大的情況下,,在FPGA中能實現(xiàn)達到167.53MHz采樣吞吐率,適合于高速自適應(yīng)應(yīng)用的場合,。

1 梯度自適應(yīng)聯(lián)合濾波算法(GALJP)

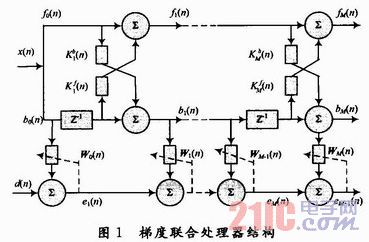

格型濾波器具有快速解耦的性質(zhì),,利用這個特性,結(jié)合基本LMS算法得到的一種實用的聯(lián)合處理結(jié)構(gòu)GALJP,,如圖1所示,。這種聯(lián)合濾波器由多級格型預(yù)測器和LMS期望響應(yīng)估計器組合而成,它可以先將信號輸入進行快速Gram-Schmidt正交化,,并由后續(xù)的自適應(yīng)期望響應(yīng)估計器的LMS算法對去耦信號進行自適應(yīng)濾波,,以改善輸入信號特征值擴散對傳統(tǒng)LMS算法性能的影響。這種結(jié)構(gòu)具有很大的優(yōu)點,,如調(diào)節(jié)濾波器的階數(shù)十分方便,,增減節(jié)數(shù)不會影響到系統(tǒng)全局的優(yōu)化,改變某一節(jié)不需要對整個系統(tǒng)進行調(diào)節(jié),。

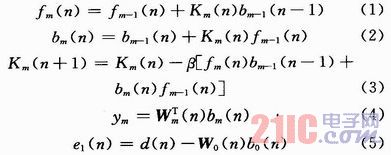

GALJP的基本算法如下:

式中:m=2,,3,…,,M+1,,不同于傳統(tǒng)的單個誤差e調(diào)節(jié)各級濾波器權(quán)向量更新,上面的GALJP算法是把各節(jié)誤差信號em(n)的均方值由單節(jié)計算,,采用多級單LMS結(jié)構(gòu),,并分別指導(dǎo)各級權(quán)向量更新,。

2 改進型RD-GALJP算法

由于GALJP的算法相對復(fù)雜,,正常情況下的硬件實現(xiàn)不能達到高速信號處理的要求。在此,,結(jié)合馳豫超前流水線技術(shù)和時序重構(gòu)技術(shù)對算法進行優(yōu)化改進,,以便在對濾波性能沒有很大影響的情況下能有效地切割關(guān)鍵路徑,提高系統(tǒng)運行頻率,。

2.1 馳豫超前流水線優(yōu)化

流水線技術(shù)是構(gòu)造高速運行系統(tǒng)的一種實用技術(shù),。在硬件實現(xiàn)中,通過插入流水寄存器,,可以斬斷系統(tǒng)關(guān)鍵路徑的長度,,提高系統(tǒng)的運行頻率。單向前饋割集表示能夠斬斷同向信號流,,使系統(tǒng)成為完全不相連兩個部分的分割形式,。本文對于單向前饋割集路徑插入一級流水寄存器,這里會使輸出增加一個時鐘滯后,,但可以在不影響系統(tǒng)算法性能的情況下切割路徑,,提高系統(tǒng)頻率,。

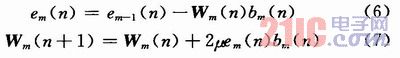

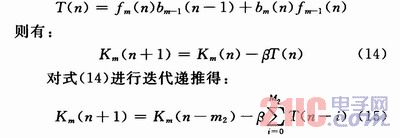

馳豫技術(shù)也是一種可以構(gòu)造實現(xiàn)流水線的方式,它通過近似的方式改變算法,,在系統(tǒng)可以良好穩(wěn)定運行的情況下得到適合流水實現(xiàn)的拓撲結(jié)構(gòu),。對于GALJP算法,考慮到其中有多個環(huán)路迭代計算,,無法使用前饋割集插入流水線的方式改進,。對此,通過馳豫超前技術(shù),,提出的改進部分如下,,對于格型預(yù)測器有:

式中:m=2,3,,…,,M+1,對于格型預(yù)測器,,由于反射系數(shù)Km收斂迅速,,所以在收斂后由于Km基本不變,故等式(8),,式(9)是合理的,。穩(wěn)態(tài)性能則基本不變。

考慮收斂時段的式(10),,令:

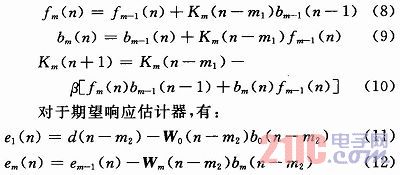

當(dāng)系統(tǒng)處于收斂時段,,恰當(dāng)選取較小的β值時,式(15)的遞推也是合理的,,對比改變前的式(14),,只是更新部分數(shù)值變大。這里可以看到,,對于反射系數(shù)的馳豫,,其算法收斂步長的區(qū)間將變得相對嚴格。類似的,,對于期望響應(yīng)估計器,,對bm和Wm的馳豫變換在恰當(dāng)選取稍小的μ的情況下也是合理的,同樣的,,會造成步長收斂區(qū)間變得相對狹窄,。觀察改進后的拓撲結(jié)構(gòu),對于期望響應(yīng)估計器,,改進后的誤差更新和權(quán)系數(shù)更新可以同時流水進行,,提高了模塊速度,對于格型預(yù)測器,雖然改進方案沒有使其能夠流水線化,,不能實質(zhì)地提高系統(tǒng)頻率,,但是提供了馳豫寄存器,為后續(xù)優(yōu)化做了準(zhǔn)備,。在這里,,馳豫寄存器m1,m2的個數(shù)需要根據(jù)要求仔細選取,。

2.2 時序重構(gòu)優(yōu)化

時序重構(gòu)又稱重定時,,是一種在保持系統(tǒng)功能不變的前提下,改變系統(tǒng)的延遲數(shù)目和分布的方法,。它在同步電路中有許多應(yīng)用,,如縮短系統(tǒng)時鐘周期,減少系統(tǒng)寄存器數(shù)目,,降低系統(tǒng)的功耗和邏輯綜合的規(guī)模,。對于時序不變系統(tǒng),通過時序重構(gòu)技術(shù),,可以在不改變算法功能的情況下,,有效地切割關(guān)鍵路徑,從而提高系統(tǒng)工作頻率,。時序重構(gòu)的映射等式定義為:

![]()

式中:Wr(e)表示重構(gòu)映射后的路徑e的延時,;W(e)表示重構(gòu)映射前的路徑e的延時;r(V)表示路徑e的前端處理單元V的重構(gòu)參數(shù),;r(U)代表路徑e的后端處理單元U的重構(gòu)參數(shù),。通過合理地選取重構(gòu)映射參數(shù),可以得到合法的重構(gòu)映射結(jié)構(gòu),。

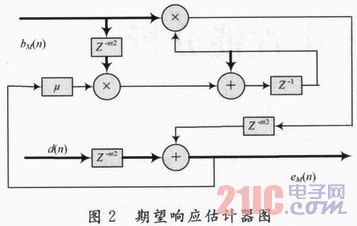

環(huán)路邊界的定義為t1/wl,,其中tl是環(huán)路l的運算時間;wl是環(huán)路l的延遲數(shù)目,;迭代邊界是環(huán)路結(jié)構(gòu)的環(huán)路邊界的最大值,,定義為![]() ,,迭代邊界反映了一個反饋算法環(huán)路部分通過時序重構(gòu)技術(shù)能達到的極限關(guān)鍵路徑的大小,。在此認為加法器和乘法器都是一個處理時間,考慮期望響應(yīng)估計器模塊的環(huán)路部分,,如圖2所示,。

,,迭代邊界反映了一個反饋算法環(huán)路部分通過時序重構(gòu)技術(shù)能達到的極限關(guān)鍵路徑的大小,。在此認為加法器和乘法器都是一個處理時間,考慮期望響應(yīng)估計器模塊的環(huán)路部分,,如圖2所示,。

根據(jù)定義可以知道,迭代邊界為4/(1+m2),,使其迭代邊界最小化,,等于1,得到馳豫寄存器的數(shù)目m2=3。采用時序重構(gòu)映射,,根據(jù)式(16)得到重構(gòu)后的算法結(jié)構(gòu),,重構(gòu)參數(shù)及重構(gòu)結(jié)果如圖3所示。

由于重構(gòu)后每個信號路徑上都沒有負延時情況,,根據(jù)時序重構(gòu)原理的性質(zhì),,則這個重構(gòu)映射是合理的,重構(gòu)后的算法結(jié)構(gòu)是合理的,,穩(wěn)定的,。可以看到,,合理地選取映射規(guī)則對電路進行時序重構(gòu),,可以合理地斬斷關(guān)鍵路徑,提高系統(tǒng)運行速度,。在這里,,重構(gòu)后的關(guān)鍵路徑為一個處理單位。同理,,可以對多級格型預(yù)測器模塊進行時序重構(gòu),。同樣的,重構(gòu)后格型預(yù)測器電路的關(guān)鍵路徑也為一個處理單元,。這樣,,整個改進后的RD-GALJP(Retimed Delay-GALJP)系統(tǒng)結(jié)構(gòu)的關(guān)鍵路徑就縮短為1個處理單元。

3 基于FPGA的算法的實現(xiàn)與仿真

以自適應(yīng)噪聲對消為模型進行仿真驗證,,設(shè)格型預(yù)測器的反射系數(shù)收斂因子為0.008,,期望響應(yīng)估計器的收斂因子為0.002。在Matlab中對改進前和改進后的算法進行仿真,,測試信號為隨機2FSK+高斯白噪聲,,SNR=-9dB,得到的收斂曲線如圖4所示,。

可以看到,,改進后的算法在收斂性能和穩(wěn)態(tài)表現(xiàn)都有些許下降,但是降低的幅度很小,,在可接受的范圍內(nèi),。利用DSP-builder進行FPGA算法建模,實現(xiàn)4階16位定點格式的格型濾波結(jié)構(gòu),,并在Modelsim中進行RTL級仿真,,得到的改進算法濾波效果如圖5所示。

在EP2C70F896C6芯片上進行代碼的綜合,,得到的結(jié)果為:改進前系統(tǒng)的最高工作頻率為23.99MHz,,改進后系統(tǒng)的最高工作頻率為167.53MHz。顯然,系統(tǒng)頻率在算法結(jié)構(gòu)改進后有很大的提高,。最后,,利用DDS技術(shù)產(chǎn)生需要的測試信號和噪聲(測試頻率為100MHz),將相應(yīng)的HDL代碼綜合布線后下載到FPGA芯片中,,利用Signaltap內(nèi)嵌邏輯分析儀進行板級功能測試,,結(jié)果如圖6所示。

實驗結(jié)果表明,,該模塊可以很好地運行在100MHz以上,,適用于高速自適應(yīng)處理的場合。

4 結(jié)語

FPGA以其高效的硬件特性在信號處理方面有著越來越多的應(yīng)用,。本文結(jié)合馳豫超前流水線和時序重構(gòu)技術(shù),,提出一種RD-GALJP算法結(jié)構(gòu),并以自適應(yīng)噪聲對消為模型進行算法仿真,。算法仿真的結(jié)果表明,,改進算法結(jié)構(gòu)相比改進前的算法在濾波性能上只有些許下降,但是卻能夠很好地切割關(guān)鍵路徑,,以利于流水實現(xiàn),。最后以4階16位定點格式為背景在FPGA中對算法進行實現(xiàn)和板級功能測試,綜合布線后得到167.53MHz采樣吞吐率的運算性能,,比較于改進前的23.99MHz的工作頻率表明,,工作頻率的改善顯著。實驗結(jié)果表明,,改進算法結(jié)構(gòu)可以很好地應(yīng)用于對輸入自相關(guān)矩陣特征值擴散敏感的高速高靈敏度的自適應(yīng)信號處理場合,。