基于PowerPC 的嵌入式系統(tǒng)在網(wǎng)絡(luò)通信應(yīng)用方面具有不可替代的優(yōu)勢(shì), 論文基于Freescale 公司的MPC8360E PowerQUICCII Pro 處理器設(shè)計(jì)多網(wǎng)口嵌入式終端系統(tǒng),實(shí)現(xiàn)系統(tǒng)啟動(dòng)、網(wǎng)絡(luò)數(shù)據(jù)交換和存儲(chǔ)等功能。系統(tǒng)由MPC8360E 基本系統(tǒng)、電源模塊、存儲(chǔ)模塊和網(wǎng)絡(luò)接口模塊及UART 接口、編程接口等模塊組成。論文針對(duì)PowerPC 控制器及網(wǎng)絡(luò)接口芯片的抗干擾要求,討論了電源電路的抗干擾設(shè)計(jì)、重要信號(hào)線的阻抗匹配、未使用信號(hào)的合理處理及PCB 的抗干擾處理等關(guān)鍵問題。經(jīng)測(cè)試該系統(tǒng)能夠可靠地工作,完成網(wǎng)絡(luò)通信功能。

1 引言

PowerPC 處理器性能好,穩(wěn)定性強(qiáng),集成度高。最新的PowerPC處理器集成了具有通信處理功能的通信引擎(QUICC Engine)技術(shù),在網(wǎng)絡(luò)通信領(lǐng)域得到了廣泛應(yīng)用。

為滿足多個(gè)網(wǎng)絡(luò)產(chǎn)品數(shù)據(jù)匯接的特殊需要, 本文設(shè)計(jì)一套多網(wǎng)口嵌入式終端系統(tǒng), 具有多個(gè)網(wǎng)絡(luò)端口間數(shù)據(jù)交換和存儲(chǔ)的功能。

系統(tǒng)基于Freescale 的PowerPC 處理器MPC8360E 設(shè)計(jì),包括MPC8360E 基本系統(tǒng)、電源模塊、存儲(chǔ)模塊和網(wǎng)絡(luò)接口模塊及UART 接口、編程接口。

MPC8360E 處理器首次采用QUICC Engine 技術(shù),具有8 個(gè)通用的通信處理器(Unified Communication Controller,UCC),支持廣泛的通信接口,為網(wǎng)絡(luò)、通信的開發(fā)提供了一個(gè)高性價(jià)比、高集成控制的處理器解決方案。

論文討論了基于MPC8360E 的多網(wǎng)口嵌入式終端系統(tǒng)設(shè)計(jì)方案及系統(tǒng)框圖,重點(diǎn)討論了系統(tǒng)設(shè)計(jì)中的抗干擾措施,給出了電源抗干擾電路、PowerPC 及網(wǎng)絡(luò)芯片特殊信號(hào)處理等關(guān)鍵的抗干擾電路設(shè)計(jì), 并介紹了分層與布局、BGA 走線、等長走線、蛇形走線、差分走線等抗干擾印制電路板(PCB)設(shè)計(jì)方法。

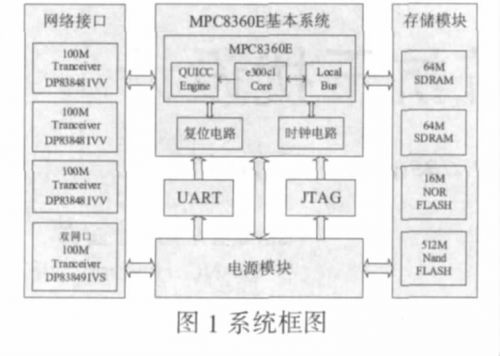

2 基于MPC8360E 的多網(wǎng)口嵌入式終端系統(tǒng)框圖

基于MPC8360E 的多網(wǎng)口嵌入式系統(tǒng)具有五個(gè)百兆網(wǎng)絡(luò)接口,能夠?qū)崿F(xiàn)系統(tǒng)啟動(dòng)、網(wǎng)絡(luò)設(shè)備管理及多網(wǎng)絡(luò)端口的數(shù)據(jù)傳輸控制。如圖1 所示,主要包括MPC8360E 基本系統(tǒng)、電源模塊、存儲(chǔ)模塊和網(wǎng)絡(luò)接口模塊及UART 接口、編程接口幾部分。在MPC8360E 的主控下,幾部分協(xié)調(diào)工作,實(shí)現(xiàn)網(wǎng)絡(luò)數(shù)據(jù)的交換和存儲(chǔ)等功能。

MPC8360E 基本系統(tǒng)提供MPC8360E 正常復(fù)位及啟動(dòng)需要的基本信號(hào)。MPC8360E 基于增強(qiáng)的e300c1 內(nèi)核,提供了豐富的系統(tǒng)接口, 如支持general -purpose chip -select machine(GPCM),synchronous DRAM (SDRAM) machine,user -programmablemachines (UPM) 三種接口的Local Bus Controller(LBC)。此外它還使用了QUICC Engine 技術(shù),配備了兩個(gè)速率可以高達(dá)500MHz 的RISC 核心,提供了集成的多協(xié)議處理和互通技術(shù),使得MPC8360E 的通信處理功能更加強(qiáng)大。

電源模塊負(fù)責(zé)給整個(gè)系統(tǒng)供電, 提供PowerPC 芯片及外圍電路需要的3.3V 和1.2V 兩種電壓。

存儲(chǔ)模塊用來存儲(chǔ)系統(tǒng)啟動(dòng)代碼、Linux 內(nèi)核鏡像和網(wǎng)絡(luò)通信中的數(shù)據(jù)等, 其包括兩片64M SDRAM, 一片16M NORFLASH 和一片512M NAND FLASH.其中,SDRAM 提供程序的運(yùn)行空間;NOR FLASH 用來存儲(chǔ)U-Boot、Linux 內(nèi)核、文件系統(tǒng)等;NAND FLASH 主要用來存儲(chǔ)網(wǎng)絡(luò)通信中的數(shù)據(jù)。

系統(tǒng)中通過芯片DP83848IVV,DP83849IVS 與MPC8360E的UCC、網(wǎng)絡(luò)隔離器的連接提供了五個(gè)RJ45 接口,以滿足嵌入式終端系統(tǒng)多個(gè)網(wǎng)口的需求。DP83848IVV 和DP83849IVS 分別是單端口和雙端口以太網(wǎng)物理層收發(fā)器,支持100Mbps 全雙工工作方式,適用于高速網(wǎng)絡(luò)互聯(lián)設(shè)備。

JTAG 和UART 接口系統(tǒng)用于調(diào)試系統(tǒng),打印系統(tǒng)調(diào)試信息或者其他有用信息。

3 抗干擾電路設(shè)計(jì)

高頻嵌入式系統(tǒng)電路的抗干擾處理措施是影響系統(tǒng)能否正常工作的關(guān)鍵,電源電路的抗干擾處理、重要信號(hào)的阻抗匹配、未使用信號(hào)的合理處理,都是確保系統(tǒng)正常工作的關(guān)鍵。本系統(tǒng)設(shè)計(jì)中,著重研究了電源電路的抗干擾處理、重要信號(hào)的阻抗匹配、未使用信號(hào)管腳的處理等抗干擾電路設(shè)計(jì)的關(guān)鍵問題。

3.1 電源電路抗干擾處理

提高電源的抗干擾性是保證系統(tǒng)可靠性的關(guān)鍵問題之一。

系統(tǒng)除了要對(duì)輸入電源進(jìn)行穩(wěn)壓外還要采取以下措施: ⑴在每個(gè)集成電路的電源與地之間加上高頻濾波電容和幾十微法到幾百微法的大電容器。這些電容既可以旁路掉該電路的高頻噪聲,又可以濾除紋波,避免電流突變引起電壓的波動(dòng),從而給電路提供穩(wěn)定的最佳電壓。⑵根據(jù)芯片的要求對(duì)不同的電源進(jìn)行特殊相應(yīng)的處理。

系統(tǒng)所需要的3.3V 和1.2V 電源上都并接了0.1μF、0.01μF 的高頻濾波電容器和220μF 的大電容,它們可以有效地抑制在電源線上傳導(dǎo)的高頻干擾,克服干擾信號(hào)對(duì)系統(tǒng)工作的影響,還可以儲(chǔ)存能量,給元器件提供穩(wěn)定的最佳電壓。隨著應(yīng)用場(chǎng)合和芯片的不同,電源電路的要求也會(huì)有所區(qū)別,實(shí)際應(yīng)用中要注意根據(jù)具體要求采取相應(yīng)的設(shè)計(jì)方案。如MPC8360E 中各個(gè)PowerQuicc II Pro PLL 電路不能直接由電源引腳VDD 供電,而是要獨(dú)立供電。每個(gè)PowerQuicc II Pro PLL 都要由它所對(duì)應(yīng)的獨(dú)立于VDD 的電源引腳AVDDn(n=1,2,3,4,5,6)供電,并且每個(gè)AVDDn(n=1,2,3,4,5,6)引腳還要有獨(dú)立的低通濾波電路。通過這些濾波電路濾除頻率在500kHz-10MHz 的噪聲, 降低PLL彼此間的噪聲干擾。

3.2 重要信號(hào)線的阻抗匹配

高速系統(tǒng)設(shè)計(jì)中信號(hào)傳輸線上阻抗匹配是有效地減小信號(hào)反射,提高信號(hào)質(zhì)量的重要措施。一般情況下,對(duì)芯片的控制信號(hào)、時(shí)鐘信號(hào)等關(guān)鍵信號(hào),采取在盡量靠近這些信號(hào)源端的位置上串行接入一個(gè)電阻的措施,以減少二次反射,增強(qiáng)信號(hào)的完整性。

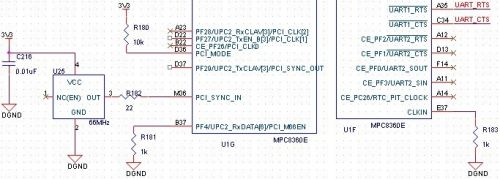

圖2 串聯(lián)端接阻抗匹配電路

本系統(tǒng)中,MPC8360E 的時(shí)鐘信號(hào)線對(duì)系統(tǒng)工作具有重要影響,以圖2 為例,在傳輸線上靠近時(shí)鐘信號(hào)源端MPC8360E 位置處串聯(lián)了22Ω 的小電阻,實(shí)現(xiàn)了串聯(lián)端接阻抗匹配,減小了過沖和振鈴,降低了高頻成分,增強(qiáng)了電磁兼容性,同時(shí)也有利于延長器件的使用壽命。此外,電路中對(duì)MPC8360E 的讀寫控制信號(hào)線及某些芯片的地址線等信號(hào)線也采取了阻抗匹配處理。

3.3 未使用的重要信號(hào)的特殊處理

電路的輸入引腳一般都不懸空, 尤其是CMOS 電路的輸入引腳絕對(duì)不能懸空,否則可能會(huì)使柵極因感應(yīng)靜電而擊穿,也可能會(huì)因受到外界噪聲的干擾而破壞電路的正常邏輯關(guān)系。

在系統(tǒng)設(shè)計(jì)時(shí), 對(duì)于MPC8360E 芯片的一些重要的不可以懸空的引腳進(jìn)行了上拉或下拉的處理。

以圖3 為例,MPC8360E 有兩個(gè)時(shí)鐘輸入CLKIN 和PCI_CLK(PCI_SYNC_IN),當(dāng)系統(tǒng)工作在PCI 缺省模式時(shí),(本系統(tǒng)采用的工作模式), 時(shí)鐘信號(hào)通過PCI_CLK 輸入, 并不需要CLKIN.但是引腳CLKIN 不能懸空,要通過1K 電阻連接到地。

再如PCI 信號(hào)M66EN 作為輸入引腳也不能懸空,可以上拉到固定電平,也可以下拉到地,系統(tǒng)中選用下拉到地的方式。

圖3 未使用的重要信號(hào)的特殊處理

3.4 網(wǎng)絡(luò)芯片的抗干擾處理

網(wǎng)絡(luò)芯片DP83848IVV 和DP83849IVS 都含有內(nèi)置穩(wěn)壓器,其電源反饋供電電路要正確處理。每個(gè)內(nèi)置穩(wěn)壓器有電源反饋輸入引腳和電源反饋輸出引腳,要確保其正確工作,必須將電源反饋輸入引腳連接到電源反饋輸出引腳,而且還要在靠近各個(gè)電源反饋輸入引腳處分別并接一個(gè)0.1μF 的小電容, 以及在靠近電源反饋輸出引腳處并接一個(gè)0.1μF 的小電容和一個(gè)10μF的鉭電容。

4 抗干擾PCB 設(shè)計(jì)

高速電路系統(tǒng)PCB 設(shè)計(jì)的好壞嚴(yán)重影響了系統(tǒng)的抗干擾能力,干擾嚴(yán)重的時(shí)候會(huì)造成系統(tǒng)無法正常工作。在進(jìn)行PCB設(shè)計(jì)時(shí),分別考慮了系統(tǒng)分層與布局、特殊布線及電源平面地平面處理等關(guān)鍵問題。

4.1 分層與布局

確定電路板的布線層數(shù)、電源層數(shù)以及它們之間的相對(duì)排布位置對(duì)PCB 設(shè)計(jì)至關(guān)重要,成功解決這些問題,不但可以得到一個(gè)好的疊層結(jié)構(gòu),還可以更好地防范大多數(shù)信號(hào)整體問題和電磁兼容性(EMC)問題。多網(wǎng)口嵌入式終端系統(tǒng),采用了六層疊層結(jié)構(gòu),其中布線層有四層,電源層和地層各有一層,并且選擇將電源層和地層分別放在第2 層和第5 層, 以更加方便地控制信號(hào)的阻抗。

多網(wǎng)口終端系統(tǒng)的元件布局遵循信號(hào)流向原則,把同類元器件按相同的方向擺放原則和盡可能地使互連線最短原則等一般原則,同時(shí)它的布局還注意了以下幾個(gè)方面:

⑴電源的去耦電容遵循就近原則, 即每個(gè)電源的去耦電容盡量挨著該電源引腳擺放。

⑵芯片MPC8360E 是BGA 封裝,布局時(shí)與該芯片相關(guān)的旁路電容、時(shí)鐘終端RC 電路、阻尼電阻等小零件要靠近芯片擺放。

⑶網(wǎng)絡(luò)芯片內(nèi)置穩(wěn)壓器的濾波電容要特殊放置: 在靠近各個(gè)電源反饋輸入和輸出引腳處均放置一個(gè)0.1μF 的小電容,另外靠近電源反饋輸出引腳處還要放置一個(gè)10μF 的鉭電容。

4.2 布線策略

本系統(tǒng)的PCB 設(shè)計(jì)在遵循45°拐角布線、相鄰層垂直布線等一般原則基礎(chǔ)上,使用了一些特殊的布線技巧,以減少布線對(duì)系統(tǒng)的可靠性產(chǎn)生的不利影響。

4.2.1 BGA 走線

芯片MPC8360E 是BGA 封裝,系統(tǒng)中的高頻信號(hào)大都是從此封裝拉出的,為了使BGA 自身信號(hào)的干擾降至最低,布線遵循BGA 芯片自身的走線原則。①BGA 封裝的芯片MPC8360E扇出前先將芯片由中心以十字劃分,過孔分別朝左上、左下、右上、右下方向打在芯片引腳與引腳正中間。如果走線需要,過孔可以從表面層拉出之后再打,需要注意的是信號(hào)線不能在內(nèi)部回轉(zhuǎn),要以輻射形態(tài)向外拉出。②當(dāng)旁路電容和芯片MPC8360E在同一面時(shí),走線直接從芯片引腳接至旁路電容,再由旁路電容拉出打過孔到電源平面。③當(dāng)旁路電容與芯片MPC8360E 不同面時(shí),即旁路電容在底層時(shí),它與芯片MPC8360E 臨近的電源、地引腳共享同一個(gè)過孔,且線長不超過100mil.④電源線寬、地線寬和時(shí)鐘信號(hào)的線寬大于一般信號(hào)的線寬。

4.2.2 等長布線和蛇形布線

有些數(shù)據(jù)信號(hào)或者地址信號(hào)對(duì)實(shí)際走線長度十分敏感,如果它們的長度不匹配就會(huì)引起信號(hào)的不同步,從而影響系統(tǒng)的正常工作。在布此類信號(hào)線時(shí)一般通過采用等長布線的技巧達(dá)到信號(hào)線長度匹配的要求。本系統(tǒng)中, ①通過等長布線,芯片MPC8360E 的引腳LSYNC_IN 到引腳LSYNC_OUT 的長度等同于MPC8360E 到SDRAM 的長度,實(shí)現(xiàn)了同頻同相。②系統(tǒng)中用了兩片SDRAM 芯片MT48LC32M16A2,在布線時(shí)也采取了等長布線的策略。其中時(shí)鐘線長度控制在2567±25mil;控制信號(hào)線以及地址線和時(shí)鐘線等長,且線長誤差不超過±100mil;數(shù)據(jù)線盡量和時(shí)鐘線,地址線以及控制線等長但長度不長于這些線。

等長布線往往需要在規(guī)定的空間里增加布線的長度, 這時(shí)不可避免的要用到蛇形走線的技巧。如,系統(tǒng)通過蛇形走線增加SDRAM 中某些數(shù)據(jù)線和時(shí)鐘線的長度,以實(shí)現(xiàn)兩片SDRAM 數(shù)據(jù)線之間和時(shí)鐘線之間的等長。這樣做不但減少了電磁輻射,也調(diào)節(jié)了延時(shí)以滿足系統(tǒng)的時(shí)序設(shè)計(jì)要求, 從而使得系統(tǒng)更加可靠。

4.2.3 差分布線

網(wǎng)絡(luò)收發(fā)芯片DP83848IVV,DP83849IVS 中存在差分信號(hào),如TD±,RD±,這些成對(duì)的信號(hào)在布線時(shí)要采用差分布線。一般來說,差分對(duì)信號(hào)的走線要在同一布線層(side-by-side),它們長度相同并且盡量保持平行,這樣既可以保證兩個(gè)差分信號(hào)時(shí)刻保持相反極性, 又可避免出現(xiàn)兩線忽遠(yuǎn)忽近引起差分阻抗不一致的情況,從而達(dá)到減少共模分量和減少反射的目的, 更有利于解決信號(hào)完整性(signal integrity)問題。以圖4 為例,系統(tǒng)PCB設(shè)計(jì)中,在PCB 繪圖軟件中對(duì)差分信號(hào)的規(guī)則進(jìn)行了設(shè)置,以達(dá)到差分布線等長等距的要求,從而提高了系統(tǒng)的抗干擾能力,有效地抑制了EMI,還使得時(shí)序定位更加準(zhǔn)確。

4.3 電源平面(線)和地平面(線)的處理

六層電路板中其中一層全部用銅箔做成地平面,有效地解決了高頻電路的信號(hào)完整性問題。另外,電源使用整層平面,然后根據(jù)系統(tǒng)電壓的大小對(duì)電源平面進(jìn)行分割,以減少電壓之間的相互干擾。其中,在進(jìn)行電源分割時(shí),盡量使芯片的電源引腳就近打孔后可以直接到達(dá)電源平面。

增加信號(hào)層中的電源線和地線寬度,使得它們大于一般信號(hào)的線寬。同時(shí),電源線、地線的走向要和數(shù)據(jù)傳遞的方向一致,以增強(qiáng)系統(tǒng)的抗噪聲能力,從而使系統(tǒng)更加可靠。

5 結(jié)論

從系統(tǒng)電路原理設(shè)計(jì)到PCB 繪制,采取合理的抗干擾措施,是高速電路設(shè)計(jì)的關(guān)鍵。本文基于PowerPC 實(shí)現(xiàn)嵌入式多網(wǎng)絡(luò)終端,硬件設(shè)計(jì)的可靠性更是不可忽視的問題。論文解決了電源電路的抗干擾、重要信號(hào)線的阻抗匹配、網(wǎng)絡(luò)接口電路的抗干擾及PCB 的抗干擾等關(guān)鍵問題,按照論文的設(shè)計(jì)原則設(shè)計(jì)的系統(tǒng)樣板如圖5 所示。該系統(tǒng)能夠可靠地工作, 完成數(shù)據(jù)交換和存儲(chǔ)功能。