慢門(mén)限恒虛警處理是一種對(duì)接收機(jī)內(nèi)部噪聲電平進(jìn)行恒虛警處理的電路,,內(nèi)部噪聲隨著溫度、電源等因素的改變而改變,,這種變化是緩慢的,,所以針對(duì)內(nèi)部噪聲的處理稱(chēng)為慢門(mén)限恒虛警處理,。通過(guò)對(duì)雷達(dá)信號(hào)的慢門(mén)限處理降低了虛警概率,為后處理提供了必要條件,。

利用大規(guī)模可編程電路來(lái)實(shí)現(xiàn)慢門(mén)限恒虛警處理,,具有方便、可靠的特點(diǎn),,可以方便地修改和仿真。雷達(dá)工作期,,接收機(jī)輸出除噪聲外還有信號(hào)和地物雜波等,所以對(duì)噪聲的采樣應(yīng)在休止期進(jìn)行。接收機(jī)檢測(cè)器后噪聲電壓的概率密度函數(shù)服從瑞利分布

由式(2)可得出,P(y)與σ無(wú)關(guān),,如果能將變量x歸一化為變量y,,則噪聲強(qiáng)度σ變化時(shí)將保持輸出恒虛警;恒虛警處理裝置就是設(shè)法檢測(cè)出噪聲x的均方差σ值,,再算出值;這個(gè)過(guò)程稱(chēng)為歸一化,,歸一化的結(jié)果就達(dá)到了恒虛警的目的,。

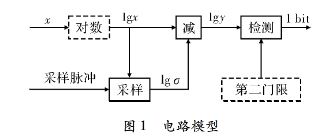

用數(shù)字電路實(shí)現(xiàn)除法運(yùn)算比較復(fù)雜,故采用取對(duì)數(shù)的方法,,將除法運(yùn)算轉(zhuǎn)化為減法運(yùn)算,,簡(jiǎn)化了電路實(shí)現(xiàn)

FPGA" p="" src="http://files.chinaaet.com/images/2012/07/24/6b72bd77-7904-4c2c-a762-9f65dabc5124.jpg" title="FPGA" />

1 工作原理

在休止期對(duì)噪聲值lgx采樣,,得到lgσ,。取雷達(dá)工作期的lgx減去lgσ,,算出lgy式(3),完成了歸一化處理,。設(shè)計(jì)中慢門(mén)限恒虛警處理電路是采用開(kāi)環(huán)式噪聲電平恒定電路,,省略了反對(duì)數(shù)電路,,增加了部分檢測(cè)電路,原理如圖1所示,。

2 FPGA設(shè)計(jì)

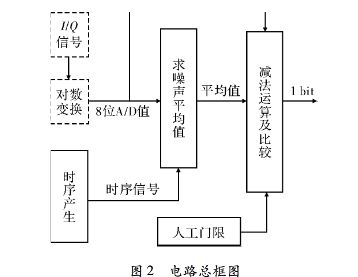

在休止期選8位I/Q信號(hào)幅度值進(jìn)行累加,,并對(duì)累加值進(jìn)行鎖存,,當(dāng)累加128個(gè)單元后,取出平均值并鎖存作為第一門(mén)限值,。在工作期選取8位I/Q信號(hào)幅度值一方面與噪聲平均值比較,,另一方面減去噪聲平均值再與人工門(mén)限比較,如果兩次比較都為大于,,則輸出1 bit過(guò)門(mén)限信號(hào),。人工門(mén)限值的選定要根據(jù)虛警率確定,如果虛警點(diǎn)多則調(diào)高門(mén)限值,,反之降低門(mén)限,,保持一定的虛警點(diǎn)數(shù)。

電路總框圖如圖2所示,,包括3個(gè)子模塊分別為時(shí)序產(chǎn)生模塊,、求噪聲平均值模塊、減法運(yùn)算及比較模塊,,虛框表示FPGA芯片外圍電路,。

設(shè)計(jì)遵從了流水線和模塊化設(shè)計(jì)原則,把總模塊劃分為幾個(gè)功能獨(dú)立又相互聯(lián)系的子模塊,;上一個(gè)模塊的輸出即為下一個(gè)模塊的輸入,,由最后一個(gè)模塊完成最終結(jié)果的輸出。

各子模塊電路設(shè)計(jì)完成后,,建立相應(yīng)電路符號(hào),,在原理圖輸入方式下,將各單元電路符號(hào)按原理框圖邏輯關(guān)系連接,,通過(guò)保存,、編譯,再進(jìn)行項(xiàng)目處理包括器件選擇,、引腳定義,確認(rèn)正確無(wú)誤后便完成了FPCA內(nèi)部電路的設(shè)計(jì),,將設(shè)計(jì)項(xiàng)目下載至芯片,,嵌入板級(jí)電路與其它器件配合使用,完成電路功能,。

2.1 時(shí)序產(chǎn)生模塊

利用10 MHz時(shí)鐘產(chǎn)生τ脈沖RM,;在休止期128 τ處產(chǎn)生平均值打入脈沖RM128和清除脈沖RST128。原理圖如圖3所示,。

2.2 求噪聲平均值模塊

當(dāng)休止期時(shí),,選8位I/Q信號(hào)幅度值進(jìn)行累加,并對(duì)累加值進(jìn)行鎖存,,當(dāng)累加128個(gè)單元后取出平均值用RM128打入存儲(chǔ)器鎖存輸出作為第一門(mén)限值,,然后清除脈沖RST128清除累加值,。取平均值方法:128個(gè)單元8位I/Q信號(hào)幅度值累加最大能達(dá)到15位數(shù),平均值即為高8位值,,所以取累加值的高8位作為平均值即可,,原理如圖4所示。

2.3 減法運(yùn)算及比較模塊

在工作期選取8位I/Q信號(hào)幅度值一方面與噪聲平均值比較,,另一方面減去噪聲平均值再與人工門(mén)限比較,,如果兩次比較都為大于,則輸出 1 bit過(guò)門(mén)限信號(hào),。原理圖如圖5所示,。

3 仿真

慢門(mén)限恒虛警處理電路仿真波形如圖6所示。PM=‘1’時(shí)為休止期,,PM=‘0’時(shí)為工作期,;為使仿真波形更直觀、易理解,,休止期恒取8位I/Q信號(hào)幅度值X[8..1]=“33”,,128單元后送出平均值C[8..1]=“33”;人工門(mén)限為恒定門(mén)限,,此處設(shè)為K[8..1]=“44”,;在工作期,當(dāng)X[8..1]=“66”和“44”時(shí),,66-33<44,、44-33<44故1 bit=‘0’,當(dāng)X[8..1]=“DC”時(shí),,DC>33,,DC-33>44連續(xù)通過(guò)兩道門(mén)限故1 bit=‘1’。

4 結(jié)束語(yǔ)

以上是在MaxplusⅡ環(huán)境中設(shè)計(jì),、編譯,、仿真。一般為減少積累單元數(shù)和存儲(chǔ)計(jì)數(shù)設(shè)備,,采用降低第一門(mén)限以達(dá)到高虛警率,,而后面采用較高的人工門(mén)限以保證工作時(shí)的低虛警概率。該慢門(mén)限恒虛警處理電路的設(shè)計(jì)成功,,為設(shè)計(jì)此類(lèi)型電路提供了借鑒,。采用8位二進(jìn)制值累加128次,取高8位作為平均值的方法,,使得電路易于實(shí)現(xiàn),,該方法簡(jiǎn)單、可靠,。