文獻(xiàn)標(biāo)識(shí)碼: A

文章編號(hào): 0258-7998(2015)01-0104-03

0 引言

衛(wèi)星導(dǎo)航系統(tǒng)是最近半個(gè)世紀(jì)發(fā)展起來的通過衛(wèi)星作為通信平臺(tái)的無線電通信導(dǎo)航系統(tǒng),該系統(tǒng)能提供全天候連續(xù)高精度的位置、速度和精密時(shí)間信息[1],現(xiàn)在已成為軍事大國在戰(zhàn)爭(zhēng)中獲得軍事優(yōu)勢(shì)的重要手段之一,所以具備抗干擾能力、能夠抵抗來自不同敵對(duì)力量的各種干擾的導(dǎo)航接收機(jī)在未來的軍事應(yīng)用中具有重要的意義。

1 抗干擾方案

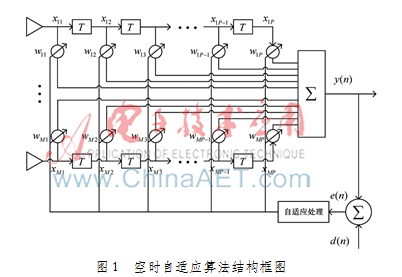

目前,在導(dǎo)航系統(tǒng)中應(yīng)用比較多的是空域自適應(yīng)算法和空時(shí)聯(lián)合自適應(yīng)算法。空域自適應(yīng)算法實(shí)現(xiàn)簡(jiǎn)單,耗資源少,但由于其只能在空域上進(jìn)行濾波,所以對(duì)于寬帶干擾的抑制能力有限,容易形成零陷點(diǎn)擴(kuò)散和偏移;而空時(shí)聯(lián)合自適應(yīng)算法可以利用每個(gè)天線陣元后面的延時(shí)抽頭來增加自適應(yīng)算法的頻率響應(yīng),從而提高算法對(duì)寬帶干擾的抗干擾能力。空時(shí)自適應(yīng)算法的結(jié)構(gòu)如圖1所示[2]。

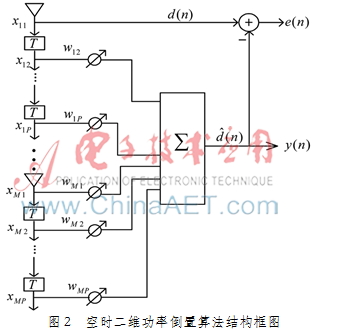

本文采用功率倒置算法來實(shí)現(xiàn)自適應(yīng)抗干擾,該算法是基于線性約束最小方差(LCMV)準(zhǔn)則的,算法使自適應(yīng)陣列的輸出功率最小[3]。對(duì)于導(dǎo)航信號(hào)和干擾,功率倒置算法均對(duì)其進(jìn)行抑制,輸入陣列信號(hào)能量越大,算法零陷深度就越深,由于干擾信號(hào)通常情況下為壓制式干擾,其能量遠(yuǎn)遠(yuǎn)大于負(fù)信噪比的導(dǎo)航信號(hào)。所以功率倒置算法適合衛(wèi)星導(dǎo)航抗干擾。圖2為空時(shí)二維功率倒置算法結(jié)構(gòu)框圖。

將LMS算法應(yīng)用于功率倒置算法,即將第一路天線接收到的信號(hào)作為參考信號(hào),其他支路信號(hào)通過LMS算法加權(quán)求和逼近第一路天線信號(hào),相減輸出,從而使得輸出信號(hào)功率盡量小。

2 一種無乘法器的DLMS算法設(shè)計(jì)

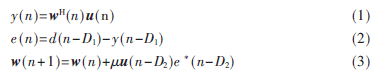

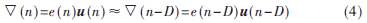

在實(shí)際工程中對(duì)LMS算法進(jìn)行硬件實(shí)現(xiàn),如FPGA實(shí)現(xiàn)等,受限于硬件處理速度,無法在較高的采樣率的一個(gè)快拍中完成迭代運(yùn)算,需要引入DLMS(延時(shí)最小均方)算法[4]。DLMS算法是在權(quán)值更新和誤差計(jì)算中的乘法和加減法運(yùn)算中引入延時(shí)單元D,當(dāng)前DLMS算法的權(quán)值更新是用經(jīng)過延時(shí)D以后的誤差信號(hào)和輸入信號(hào)來完成的,加入延時(shí)信息后的DLMS算法公式如下。

當(dāng)延遲小于系統(tǒng)階數(shù)時(shí),誤差梯度:

此時(shí)延遲后的數(shù)據(jù)不降低收斂速度。由于采用空時(shí)二維自適應(yīng)算法,所以系統(tǒng)階數(shù)較空域自適應(yīng)算法大,更適用于流水線設(shè)計(jì)。

在FPGA中,乘法器資源非常寶貴,一般較為昂貴的FPGA中才有較多的乘法器核。設(shè)計(jì)使用CORDIC算法實(shí)現(xiàn)乘法運(yùn)算,不過其缺點(diǎn)是如果要得到較高的運(yùn)算精度,則運(yùn)算需要多級(jí),會(huì)引入較大的延遲。若是將其使用在空域DLMS算法中,并要求較高的計(jì)算精度,則帶來的延遲會(huì)引起梯度估計(jì)的較大誤差,同時(shí)還會(huì)影響收斂速度;空時(shí)二維自適應(yīng)算法具有較大的系統(tǒng)階數(shù),所以CORDIC算法引入的延遲不會(huì)對(duì)梯度估計(jì)造成較大的誤差,同時(shí)對(duì)DLMS算法的收斂速度也沒有影響。所以本設(shè)計(jì)使用CORDIC算法來實(shí)現(xiàn)DLMS算法中的乘法運(yùn)算,并結(jié)合設(shè)計(jì)要求對(duì)相關(guān)參數(shù)設(shè)計(jì)進(jìn)行了介紹。

2.1 基于CORDIC算法的乘法器設(shè)計(jì)

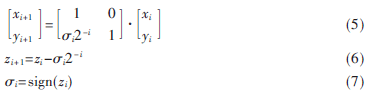

CORDIC(Coordinate Rotation Digital Computer)算法具有圓周和向量兩種模式,在兩種模式下能夠計(jì)算正弦余弦、反正切、平方根、雙曲余弦正弦、乘除法等運(yùn)算[5]。在CORDIC算法的圓周模式下能夠完成乘法運(yùn)算,其迭代方程如式(5)~式(7)所示。

但是傳統(tǒng)的CORDIC乘法運(yùn)算只有滿足|z0|<2的情況下,計(jì)算結(jié)果才是正確的,表1為CORDIC算法的MATLAB仿真結(jié)果,可以看出確實(shí)|z0|>2時(shí)計(jì)算結(jié)果錯(cuò)誤。

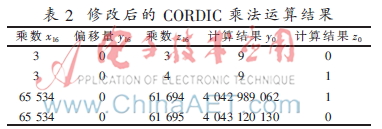

考慮到FPGA中的運(yùn)算都是整數(shù)的運(yùn)算,所以對(duì)傳統(tǒng)CORDIC乘法運(yùn)算進(jìn)行修改,將式(5)、式(6)中的2-i改為2i,并且迭代以變量i的降序來進(jìn)行。假設(shè)系統(tǒng)的AD采樣位數(shù)為16位,所以為保證乘法運(yùn)算精度,設(shè)計(jì)16級(jí)CORDIC迭代,即是變量i從16開始降序迭代。修改后的CORDIC運(yùn)算迭代結(jié)構(gòu)示意圖如圖3所示。運(yùn)算的最終輸出為result=y0+x0 z0。表2為修改后的CORDIC乘法運(yùn)算的結(jié)果。從表2中可以看出,在16位位寬下修改后的CORDIC算法能保證整數(shù)運(yùn)算的正確。

CORDIC算法容易實(shí)現(xiàn)流水線設(shè)計(jì),在每一級(jí)迭代之間(P15、P14、P13……)均可引入流水線,從而提高設(shè)計(jì)的速度。本設(shè)計(jì)使用CORDIC乘法單元代替DLMS算法中的乘法運(yùn)算,并在CORDIC乘法單元中引入適當(dāng)?shù)牧魉拇嫫鳎瑥亩岣逤ORDIC乘法單元的運(yùn)行速度。

2.2 空時(shí)二維DLMS算法的時(shí)域抽頭數(shù)設(shè)計(jì)

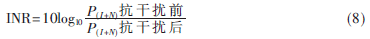

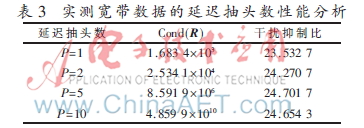

空時(shí)二維DLMS算法的參數(shù)設(shè)計(jì)關(guān)鍵在于確定天線陣列后的抽頭數(shù)。抽頭數(shù)決定了空時(shí)二維自適應(yīng)算法的階數(shù),同時(shí)決定了算法中能引入流水線的上限和對(duì)寬帶干擾的抗干擾能力。分析干擾信號(hào)被抑制的程度,采用求解未抗干擾前干擾信號(hào)+噪聲的功率和抗干擾后干擾信號(hào)+噪聲功率的比值作為標(biāo)準(zhǔn)。用式(8)表示,INR稱為干擾抑制比:

使用寬帶干擾建模進(jìn)行仿真,得到干擾抑制比結(jié)果如表3所示。從表3中可以看出,延遲抽頭數(shù)P增加會(huì)使DLMS算法的干擾抑制比增加,不過同時(shí)會(huì)增加自相關(guān)矩陣R的條件數(shù),使R病態(tài),導(dǎo)致DLMS算法收斂性能降低。當(dāng)P過大時(shí)反而會(huì)降低干擾抑制比,同時(shí)會(huì)增加硬件實(shí)現(xiàn)的資源消耗。所以系統(tǒng)綜合選取抽頭數(shù)P=5。

2.3 空時(shí)二維DLMS算法的simulink實(shí)現(xiàn)

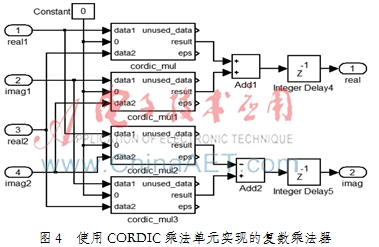

本文采用Simulink完成算法設(shè)計(jì)的仿真,圖4為使用CORDIC乘法單元實(shí)現(xiàn)的復(fù)數(shù)乘法器,其中CORDIC乘法單元的結(jié)構(gòu)如圖3所示。復(fù)數(shù)乘法器的表達(dá)式為:

x+yj=(a+bj)(c+dj)=(ac-bd)+(ad+bc)j(9)

設(shè)計(jì)使用CORDIC乘法單元完成式(9)中的4個(gè)乘法運(yùn)算,再結(jié)合一次加法運(yùn)算和一次減法運(yùn)算從而完成復(fù)數(shù)乘法器。CORDIC乘法單元中具有16級(jí)迭代單元,設(shè)計(jì)插入流水線以增加硬件的運(yùn)算速度。由于抽頭數(shù)選擇為5,則系統(tǒng)階數(shù)為5×4-1=19,考慮不影響梯度的估計(jì),這里設(shè)計(jì)在16級(jí)迭代單元中插入8級(jí)流水,使得梯度估計(jì)延遲數(shù)為11個(gè)延遲單位,小于系統(tǒng)階數(shù),不會(huì)影響DLMS算法的收斂性能。圖5為四天線、抽頭數(shù)為5、步長取DLMS抗干擾算法的第一路天線后端的4路抽頭的迭代模塊的結(jié)構(gòu)示意圖。

設(shè)計(jì)中需要考慮的一個(gè)問題是要保證流水線后的數(shù)據(jù)同步地進(jìn)行處理。設(shè)計(jì)中CORDIC乘法器引入了8個(gè)單位的延遲,再加上4路天線后時(shí)域抽頭輸出的yi(n)(i=1,2,3,…,19)相加過程中引入兩級(jí)加法樹延遲,所以y(n)的延遲是10個(gè)單位的延遲,需要將參考信號(hào)d(n)也延遲10個(gè)單位后保持與y(n)的同步,同時(shí)參考信號(hào)d(n)與y(n)相減的減法器后再加入一級(jí)延遲,使得e(n)的延遲數(shù)為11個(gè)單位,所以需要將輸入信號(hào)u(n)延遲11個(gè)單位后與e(n)相乘得到梯度估計(jì),如圖5所示。

3 測(cè)試結(jié)果及分析

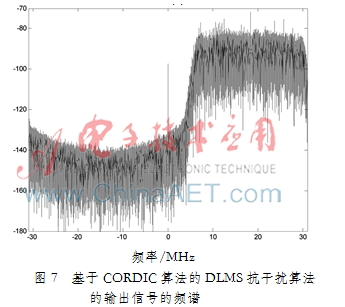

利用Simulink對(duì)實(shí)測(cè)采集數(shù)據(jù)進(jìn)行算法的仿真,其中采集數(shù)據(jù)的參數(shù)為4路天線數(shù)據(jù),中頻信號(hào)頻率為46.52 MHz,帶寬為20.46 MHz,采樣率為65.28 MHz。實(shí)驗(yàn)中給系統(tǒng)添加了一個(gè)50 dB干信比的1 268.52 MHz的單頻干擾信號(hào)和一個(gè)65 dB干信比的寬帶QPSK信號(hào),信號(hào)中心頻率為1 268.52 MHz,帶寬為20 MHz,其信號(hào)頻譜如圖6所示。仿真輸出結(jié)果如圖7和圖8所示。其中圖7為基于CORDIC算法的DLMS抗干擾算法的輸出信號(hào)e(n)的頻譜,從結(jié)果中可以看出,在數(shù)字中頻18.76±10.23 MHz頻段,e(n)輸出的頻率分量與輸入信號(hào)頻譜相比較,加入的單頻和寬帶干擾被有效地抑制了,帶內(nèi)功率譜密度降低為-80 dBm/Hz,提高了輸出的信干噪比。圖8為普通DLMS算法與基于CORDIC算法的DLMS算法的權(quán)向量?棕11的收斂曲線的比較。從結(jié)果中可以看到,基于CORDIC算法的DLMS算法沒有影響算法的收斂性能以及最終的最佳權(quán)向量。

4 結(jié)束語

本文研究了一種基于CORDIC算法的無乘法器的DLMS抗干擾算法設(shè)計(jì),結(jié)合實(shí)測(cè)數(shù)據(jù)仿真,分析了算法中關(guān)鍵參數(shù)的選取,重點(diǎn)闡述了在Simulink環(huán)境下,基于CORDIC算法的乘法器及相關(guān)的DLMS算法的結(jié)構(gòu)與實(shí)現(xiàn)。最后完成了對(duì)算法的仿真及驗(yàn)證,從仿真結(jié)果可以看出本算法設(shè)計(jì)不影響DLMS算法的特性,同時(shí)節(jié)約了乘法器資源,在CORDIC算法中引入流水線,能有效地提高算法的速度。

參考文獻(xiàn)

[1] 童鎧.中國導(dǎo)航定位衛(wèi)星系統(tǒng)的進(jìn)展[J].中國航天,2002(8):3-10.

[2] 郭藝.GPS接收機(jī)空時(shí)抗干擾理論與實(shí)現(xiàn)關(guān)鍵技術(shù)研究[D].長沙:國防科學(xué)技術(shù)大學(xué),2007.

[3] 龔耀寰.自適應(yīng)濾波[M].第2版,北京:電子工業(yè)出版社,2003.

[4] Lok-Kee Ting,Roger Woods.Virtex FPGA implementation of a pipelined adaptive LMS predictor for electronic sup-port measures receivers[J].IEEE Transactions on Verylarge Scale Integration(VLSI) Systems,2005(1).

[5] MEHER P K,VALLS J,Tso-Bing Juang,et al.50 years of CORDIC:algorithms, architectures,and applications[J].IEEE Transactions on Circuits and Systems,2009,56(9).