除了先進(jìn)制程之外,先進(jìn)封裝也成為延續(xù)摩爾定律的關(guān)鍵技術(shù),像是2.5D,、3D 和Chiplets 等技術(shù)在近年來成為半導(dǎo)體產(chǎn)業(yè)的熱門議題,。究竟,,先進(jìn)封裝是如何在延續(xù)摩爾定律上扮演關(guān)鍵角色,?而2.5D、3D 和Chiplets 等封裝技術(shù)又有何特點,?

人工智能(AI),、車聯(lián)網(wǎng)、5G 等應(yīng)用相繼興起,,且皆須使用到高速運算,、高速傳輸,、低延遲、低耗能的先進(jìn)功能芯片,;然而,隨著運算需求呈倍數(shù)成長,,究竟要如何延續(xù)摩爾定律,,成為半導(dǎo)體產(chǎn)業(yè)的一大挑戰(zhàn)。

芯片微縮愈加困難,,異構(gòu)整合由此而生

換言之,,半導(dǎo)體先進(jìn)制程紛紛邁入了7 納米、5 納米,,接著開始朝3 納米和2 納米邁進(jìn),,電晶體大小也因此不斷接近原子的物理體積限制,電子及物理的限制也讓先進(jìn)制程的持續(xù)微縮與升級難度越來越高,。

也因此,,半導(dǎo)體產(chǎn)業(yè)除了持續(xù)發(fā)展先進(jìn)制程之外,也「山不轉(zhuǎn)路轉(zhuǎn)」地開始找尋其他既能讓芯片維持小體積,,同時又保有高效能的方式,;而芯片的布局設(shè)計,遂成為延續(xù)摩爾定律的新解方,,異構(gòu)整合(Heterogeneous Integration Design Architecture System,,HIDAS)概念便應(yīng)運而生,同時成為IC 芯片的創(chuàng)新動能,。

所謂的異構(gòu)整合,,廣義而言,就是將兩種不同的芯片,,例如記憶體+邏輯芯片,、光電+電子元件等,透過封裝,、3D 堆疊等技術(shù)整合在一起,。換句話說,將兩種不同制程,、不同性質(zhì)的芯片整合在一起,,都可稱為是異構(gòu)整合。

因為應(yīng)用市場更加的多元,,每項產(chǎn)品的成本,、性能和目標(biāo)族群都不同,因此所需的異構(gòu)整合技術(shù)也不盡相同,,市場分眾化趨勢逐漸浮現(xiàn),。為此,,IC 代工、制造及半導(dǎo)體設(shè)備業(yè)者紛紛投入異構(gòu)整合發(fā)展,,2.5D,、3D 封裝、Chiplets 等現(xiàn)今熱門的封裝技術(shù),,便是基于異構(gòu)整合的想法,,如雨后春筍般浮現(xiàn)。

2.5D 封裝有效降低芯片生產(chǎn)成本

過往要將芯片整合在一起,,大多使用系統(tǒng)單封裝(System in a Package,,SiP)技術(shù),像是PiP(Package in Package)封裝,、PoP(Package on Package)封裝等,。然而,隨著智能手機,、AIoT 等應(yīng)用,,不僅需要更高的性能,還要保持小體積,、低功耗,,在這樣的情況下,必須想辦法將更多的芯片堆積起來使體積再縮小,,因此,,目前封裝技術(shù)除了原有的SiP 之外,也紛紛朝向立體封裝技術(shù)發(fā)展,。

立體封裝概略來說,,意即直接使用硅晶圓制作的「硅中介板」(Silicon interposer),而不使用以往塑膠制作的「導(dǎo)線載板」,,將數(shù)個功能不同的芯片,,直接封裝成一個具更高效能的芯片。換言之,,就是朝著芯片疊高的方式,,在硅上面不斷疊加硅芯片,改善制程成本及物理限制,,讓摩爾定律得以繼續(xù)實現(xiàn),。

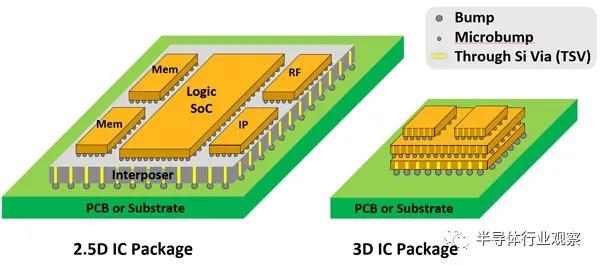

而立體封裝較為人熟知的是2.5D 與3D 封裝,這邊先從2.5D 封裝談起,。所謂的2.5D 封裝,,主要的概念是將處理器、記憶體或是其他的芯片,,并列排在硅中介板(Silicon Interposer)上,,先經(jīng)由微凸塊(Micro Bump)連結(jié),,讓硅中介板之內(nèi)金屬線可連接不同芯片的電子訊號;接著再透過硅穿孔(TSV)來連結(jié)下方的金屬凸塊(Solder Bump),,再經(jīng)由導(dǎo)線載板連結(jié)外部金屬球,,實現(xiàn)芯片、芯片與封裝基板之間更緊密的互連,。

2.5D和3D封裝是熱門的立體封裝技術(shù),。(Source:ANSYS)

目前為人所熟知的2.5D 封裝技術(shù),不外乎是臺積電的CoWoS,。CoWoS 技術(shù)概念,簡單來說是先將半導(dǎo)體芯片(像是處理器,、記憶體等),,一同放在硅中介層上,再透過Chip on Wafer(CoW)的封裝制程連接至底層基板上,。換言之,,也就是先將芯片通過Chip on Wafer(CoW)的封裝制程連接至硅晶圓,再把CoW 芯片與基板連接,,整合成CoWoS,;利用這種封裝模式,使得多顆芯片可以封裝到一起,,透過Si Interposer 互聯(lián),,達(dá)到了封裝體積小,功耗低,,引腳少的效果,。

臺積電CoWos封裝技術(shù)概念。(Source:臺積電)

除了CoWos 外,,扇出型晶圓級封裝也可歸為2.5D 封裝的一種方式,。扇出型晶圓級封裝技術(shù)的原理,是從半導(dǎo)體裸晶的端點上,,拉出需要的電路至重分布層(Redistribution Layer),,進(jìn)而形成封裝。因此不需封裝載板,,不用打線(Wire),、凸塊(Bump),能夠降低30% 的生產(chǎn)成本,,也讓芯片更薄,。同時也讓芯片面積減少許多,也可取代成本較高的直通硅晶穿孔,,達(dá)到透過封裝技術(shù)整合不同元件功能的目標(biāo),。

當(dāng)然,,立體封裝技術(shù)不只有2.5D,還有3D 封裝,。那么,,兩者之間的差別究竟為何,而3D 封裝又有半導(dǎo)體業(yè)者正在采用,?

相較于2.5D 封裝,,3D 封裝的原理是在芯片制作電晶體(CMOS)結(jié)構(gòu),并且直接使用硅穿孔來連結(jié)上下不同芯片的電子訊號,,以直接將記憶體或其他芯片垂直堆疊在上面,。此項封裝最大的技術(shù)挑戰(zhàn)便是,要在芯片內(nèi)直接制作硅穿孔困難度極高,,不過,,由于高效能運算、人工智能等應(yīng)用興起,,加上TSV 技術(shù)愈來愈成熟,,可以看到越來越多的CPU、GPU 和記憶體開始采用3D 封裝,。

3D封裝是直接將芯片堆疊起來,。(Source:英特爾)

臺積電、英特爾積極發(fā)展3D 封裝技術(shù)

在3D 封裝上,,英特爾(Intel)和臺積電都有各自的技術(shù),。英特爾采用的是「Foveros」的3D 封裝技術(shù),使用異構(gòu)堆疊邏輯處理運算,,可以把各個邏輯芯片堆棧一起,。也就是說,首度把芯片堆疊從傳統(tǒng)的被動硅中介層與堆疊記憶體,,擴(kuò)展到高效能邏輯產(chǎn)品,,如CPU、繪圖與AI 處理器等,。以往堆疊僅用于記憶體,,現(xiàn)在采用異構(gòu)堆疊于堆疊以往僅用于記憶體,現(xiàn)在采用異構(gòu)堆疊,,讓記憶體及運算芯片能以不同組合堆疊,。

另外,英特爾還研發(fā)3 項全新技術(shù),,分別為Co-EMIB,、ODI 和MDIO。Co-EMIB 能連接更高的運算性能和能力,并能夠讓兩個或多個Foveros 元件互連,,設(shè)計人員還能夠以非常高的頻寬和非常低的功耗連接模擬器,、記憶體和其他模組。ODI 技術(shù)則為封裝中小芯片之間的全方位互連通訊提供了更大的靈活性,。頂部芯片可以像EMIB 技術(shù)一樣與其他小芯片進(jìn)行通訊,,同時還可以像Foveros 技術(shù)一樣,通過硅通孔(TSV)與下面的底部裸片進(jìn)行垂直通訊,。

英特爾Foveros技術(shù)概念,。(Source:英特爾)

同時,該技術(shù)還利用大的垂直通孔直接從封裝基板向頂部裸片供電,,這種大通孔比傳統(tǒng)的硅通孔大得多,,其電阻更低,因而可提供更穩(wěn)定的電力傳輸,;并透過堆疊實現(xiàn)更高頻寬和更低延遲,。此一方法減少基底芯片中所需的硅通孔數(shù)量,為主動元件釋放了更多的面積,,優(yōu)化裸片尺寸。

而臺積電,,則是提出「3D 多芯片與系統(tǒng)整合芯片」(SoIC)的整合方案,。此項系統(tǒng)整合芯片解決方案將不同尺寸、制程技術(shù),,以及材料的已知良好裸晶直接堆疊在一起,。

臺積電提到,相較于傳統(tǒng)使用微凸塊的3D 積體電路解決方案,,此一系統(tǒng)整合芯片的凸塊密度與速度高出數(shù)倍,,同時大幅減少功耗。此外,,系統(tǒng)整合芯片是前段制程整合解決方案,,在封裝之前連結(jié)兩個或更多的裸晶;因此,,系統(tǒng)整合芯片組能夠利用該公司的InFO 或CoWoS 的后端先進(jìn)封裝技術(shù)來進(jìn)一步整合其他芯片,,打造一個強大的「3D×3D」系統(tǒng)級解決方案。

此外,,臺積電亦推出3DFabric,,將快速成長的3DIC 系統(tǒng)整合解決方案統(tǒng)合起來,提供更好的靈活性,,透過穩(wěn)固的芯片互連打造出強大的系統(tǒng),。藉由不同的選項進(jìn)行前段芯片堆疊與后段封裝,3DFabric 協(xié)助客戶將多個邏輯芯片連結(jié)在一起,甚至串聯(lián)高頻寬記憶體(HBM)或異構(gòu)小芯片,,例如類比,、輸入/輸出,以及射頻模組,。3DFabric 能夠結(jié)合后段3D 與前段3D 技術(shù)的解決方案,,并能與電晶體微縮互補,持續(xù)提升系統(tǒng)效能與功能性,,縮小尺寸外觀,,并且加快產(chǎn)品上市時程。

在介紹完2.5D 和3D 之后,,近來還有Chiplets 也是半導(dǎo)體產(chǎn)業(yè)熱門的先進(jìn)封裝技術(shù)之一,;最后,就來簡單說明Chiplets 的特性和優(yōu)勢,。

除了2.5D 和3D 封裝之外,,Chiplets 也是備受關(guān)注的技術(shù)之一。由于電子終端產(chǎn)品朝向高整合趨勢發(fā)展,,對于高效能芯片需求持續(xù)增加,,但隨著摩爾定律逐漸趨緩,在持續(xù)提升產(chǎn)品性能過程中,,如果為了整合新功能芯片模組而增大芯片面積,,將會面臨成本提高和低良率問題。因此,,Chiplets 成為半導(dǎo)體產(chǎn)業(yè)因摩爾定律面臨瓶頸所衍生的技術(shù)替代方案,。

Chiplets就像拼圖一樣,把小芯片組成大芯片

Chiplets 的概念最早源于1970 年代誕生的多芯片模組,,其原理大致而言,,即是由多個同質(zhì)、異構(gòu)等較小的芯片組成大芯片,,也就是從原來設(shè)計在同一個SoC 中的芯片,,被分拆成許多不同的小芯片分開制造再加以封裝或組裝,故稱此分拆之芯片為小芯片Chiplets,。

由于先進(jìn)制程成本急速上升,,不同于SoC 設(shè)計方式,將大尺寸的多核心的設(shè)計,,分散到較小的小芯片,,更能滿足現(xiàn)今的高效能運算處理器需求;而彈性的設(shè)計方式不僅提升靈活性,,也能有更好的良率及節(jié)省成本優(yōu)勢,,并減少芯片設(shè)計時程,加速芯片Time to market 時間。

使用Chiplets 有三大好處,。因為先進(jìn)制程成本非常高昂,,特別是模擬電路、I/O 等愈來愈難以隨著制程技術(shù)縮小,,而Chiplets 是將電路分割成獨立的小芯片,,并各自強化功能、制程技術(shù)及尺寸,,最后整合在一起,,以克服制程難以微縮的挑戰(zhàn)。此外,,基于Chiplets 還可以使用現(xiàn)有的成熟芯片降低開發(fā)和驗證成本,。

目前已有許多半導(dǎo)體業(yè)者采用Chiplets 方式推出高效能產(chǎn)品。像是英特爾的Intel Stratix 10 GX 10M FPGA 便是采用Chiplets 設(shè)計,,以達(dá)到更高的元件密度和容量,。該產(chǎn)品是以現(xiàn)有的Intel Stratix 10 FPGA 架構(gòu)及英特爾先進(jìn)的嵌入式多芯片互連橋接(EMIB)技術(shù)為基礎(chǔ),運用了EMIB 技術(shù)融合兩個高密度Intel Stratix 10 GX FPGA 核心邏輯芯片以及相應(yīng)的I /O 單元,。至于AMD 第二代EPYC 系列處理器也是如此,。有別于第一代將Memory 與I/O 結(jié)合成14 納米CPU 的Chiplet 方式,第二代是把I/O 與Memory 獨立成一個芯片,,并將7 納米CPU 切成8 個Chiplets 進(jìn)行組合,。

總而言之,過去的芯片效能都仰賴半導(dǎo)體制程的改進(jìn)而提升,,但隨著元件尺寸越來越接近物理極限,芯片微縮難度越來越高,,要保持小體積,、高效能的芯片設(shè)計,半導(dǎo)體產(chǎn)業(yè)不僅持續(xù)發(fā)展先進(jìn)制程,,同時也朝芯片架構(gòu)著手改進(jìn),,讓芯片從原先的單層,轉(zhuǎn)向多層堆疊,。也因如此,,先進(jìn)封裝也成為改善摩爾定律的關(guān)鍵推手之一,在半導(dǎo)體產(chǎn)業(yè)中引領(lǐng)風(fēng)騷,。