設(shè)計(jì)一個(gè)大規(guī)模芯片/系統(tǒng)集成的最佳路徑是什么?這是一個(gè)大家都關(guān)心的好問題。

Cerebras 通過其wafer scale engine 2 ( WSE-2 )為行業(yè)設(shè)定了一個(gè)高標(biāo)準(zhǔn):它擁有 2.6 萬億個(gè)晶體管,包括 850,000 個(gè)內(nèi)核,這個(gè)成就是他們采用臺(tái)積電的 7 納米工藝在大約 8 英寸 x 8 英寸的硅片上成就的。

達(dá)成這寫目標(biāo)的另一種不同的方法是使用chiplet技術(shù),然后使用無源硅互連技術(shù)將各種“設(shè)備”安裝到單個(gè)硅片上。加州大學(xué)洛杉磯分校和伊利諾伊大學(xué)厄巴納-香檳分校的研究人員最近發(fā)表的一篇新論文稱,這種方法更靈活,可以擴(kuò)展,并提供顯著的成本優(yōu)勢(shì)。

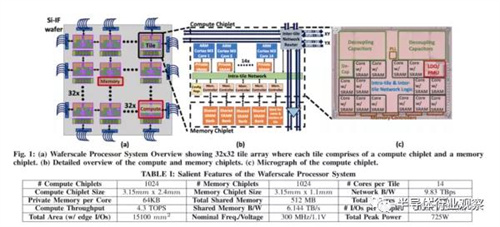

根據(jù)最近的一篇論文,該團(tuán)隊(duì)的研究人員團(tuán)隊(duì)已經(jīng)在設(shè)計(jì)并正在制作擁有2048個(gè)chiplet和14336個(gè)核心的晶圓級(jí)處理器原型,在這篇論文中,他們還很好地展示了chiplet的 方法的優(yōu)勢(shì)和挑戰(zhàn)。

“據(jù)我們所知,這是有史以來最大的基于小芯片組裝的系統(tǒng)。就活動(dòng)區(qū)域而言,我們的原型系統(tǒng)比 Nvidia/AMD 等公司的基于小芯片的系統(tǒng)大 10 倍左右,比 Nvidia 的 64 小芯片 Simba(研究)系統(tǒng)大 100 倍左右,”研究人員在論文中寫道。

基本前提是熟悉的。他們表示,“圖形處理、數(shù)據(jù)分析和機(jī)器學(xué)習(xí)等高度并行工作負(fù)載的激增正在推動(dòng)對(duì)具有大量處理核心、廣泛內(nèi)存容量和高內(nèi)存帶寬的大規(guī)模并行高性能系統(tǒng)的需求。”

到目前為止,使用傳統(tǒng)的封裝外通信鏈路連接的離散封裝處理器的異構(gòu)架構(gòu)已成為處理新工作負(fù)載的主要解決方案。此外,還有大量針對(duì)這些工作負(fù)載的新芯片和系統(tǒng),Cerebras 的 WSE-2 就是一個(gè)例子。

研究人員認(rèn)為,單片晶圓級(jí)“芯片無法集成來自異構(gòu)技術(shù)(如 DRAM 或其他密集存儲(chǔ)技術(shù))的組件。此外,為了獲得良好的產(chǎn)量,需要在晶圓級(jí)芯片上保留冗余內(nèi)核和網(wǎng)絡(luò)鏈接。

因此他們指出,小芯片策略應(yīng)該能夠克服其中的一些限制:

”構(gòu)建晶圓級(jí)系統(tǒng)的一種競(jìng)爭(zhēng)方法是在晶圓級(jí)互連基板上集成預(yù)先測(cè)試過的已知良好的小芯片(在這項(xiàng)工作中,我們將未封裝的裸芯片/小芯片稱為小芯片)。硅互連結(jié)構(gòu) (Silicon interconnect Fabric :Si-IF) 是一種候選技術(shù),它使我們能夠在高密度互連晶片上緊密集成許多小芯片。Si-IF 技術(shù)提供基于細(xì)間距銅柱(10μm 間距)的 I/O,其密度至少是基于中介層的系統(tǒng)中使用的傳統(tǒng) μ-bumps的 16 倍,以及~100μm 的小芯片間距。因此,它為小芯片間互連提供了全局的片上布線特性。此外,在基于小芯片的晶圓級(jí)系統(tǒng)中,小芯片可以采用異構(gòu)技術(shù)制造,并有可能提供更好的性價(jià)比權(quán)衡。“

下圖很好地概述了設(shè)計(jì)。

正如您所期望的那樣,芯片組方法帶來了自己的一組設(shè)計(jì)挑戰(zhàn),團(tuán)隊(duì)列舉了這些挑戰(zhàn):

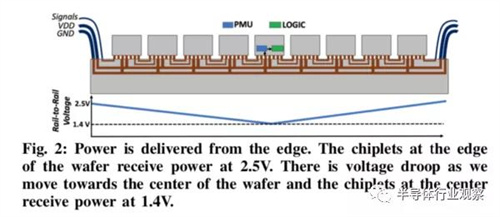

”我們應(yīng)該如何為整個(gè)晶圓上的所有倒裝芯片鍵合小芯片供電?

“我們?nèi)绾卧谌绱舜蟮膮^(qū)域內(nèi)可靠地分配時(shí)鐘?

”當(dāng)每個(gè)小芯片需要支持大量基于細(xì)間距銅柱的 I/O 時(shí),我們?nèi)绾卧O(shè)計(jì)面積高效的 I/O,我們?nèi)绾螌?shí)現(xiàn)非常高的整體小芯片組裝和鍵合良率?

“芯片間網(wǎng)絡(luò)架構(gòu)應(yīng)該怎么搭建,如果幾個(gè)小芯片出現(xiàn)故障,我們?nèi)绾螌?shí)現(xiàn)彈性?

”當(dāng) I/O pads尺寸較小時(shí),測(cè)試策略是什么?我們?nèi)绾未_保測(cè)試方案的可擴(kuò)展性?

“在制造過程的不確定性和限制條件下,我們?nèi)绾卧O(shè)計(jì)小芯片和基板?”

在那篇論文中,研究團(tuán)隊(duì)詳細(xì)介紹了針對(duì)整體架構(gòu)、計(jì)算小芯片、內(nèi)存小芯片和所選晶圓級(jí)基板的解決方案方法和具體考慮因素。還詳細(xì)檢查了網(wǎng)絡(luò)、配電和測(cè)試基礎(chǔ)設(shè)施。

該團(tuán)隊(duì)還通過在 FPGA 平臺(tái)上模擬縮小尺寸的多塊系統(tǒng)來驗(yàn)證系統(tǒng)設(shè)計(jì)和架構(gòu)。“我們能夠成功地在這個(gè)系統(tǒng)上運(yùn)行各種工作負(fù)載,包括圖應(yīng)用程序,例如廣度優(yōu)先搜索 ( breadth-first search :BFS)、單源最短路徑 ( single-source shortest path :SSSP) 等,”該論文稱。

查看一下這些原型的行為會(huì)很有趣。

該論文的作者之一、加州大學(xué)洛杉磯分校的博士Saptadeep Pal告訴HPCwire,“一個(gè)較小的硅原型現(xiàn)在已經(jīng)啟動(dòng)并運(yùn)行程序。目前正在建造晶圓級(jí)原型。我們正在一步一步地進(jìn)行。流片和系統(tǒng)在許多方面都是”第一次“,而且在大學(xué)里,重新制作的時(shí)間和金錢成本非常高。完整的晶圓級(jí)系統(tǒng)可能還需要幾個(gè)月的時(shí)間。”