最新行業(yè)報告顯示,臺積電正積極上調系統(tǒng)級集成單芯片(SoIC)的產能計劃,計劃到 2024 年年底,月產能躍升至 5000-6000 顆,以應對未來人工智能(AI)和高性能計算(HPC)的強勁需求。

AMD 是臺積電 SoIC 的首發(fā)客戶,其最新 AI 芯片產品 MI300 搭配 SoIC 和 CoWoS 封裝,如果能取得成功,那么將成為臺積電 SoIC 的一大“代表作”。

臺積電最大的客戶蘋果公司對 SoIC 非常感興趣。蘋果計劃讓 SoIC 搭配熱塑碳纖板復合成型技術,目前正小量試產,預計 2025-2026 年量產,擬應用在 Mac、iPad 等產品,制造成本比當前方案更具有優(yōu)勢。

業(yè)內人士分析稱,蘋果這一路線主要是基于產品設計、定位、成本等綜合考量。若未來 SoIC 順利導入筆電、手機等消費電子產品,有望創(chuàng)造更多需求,并大幅提升其他大客戶的跟進意愿。

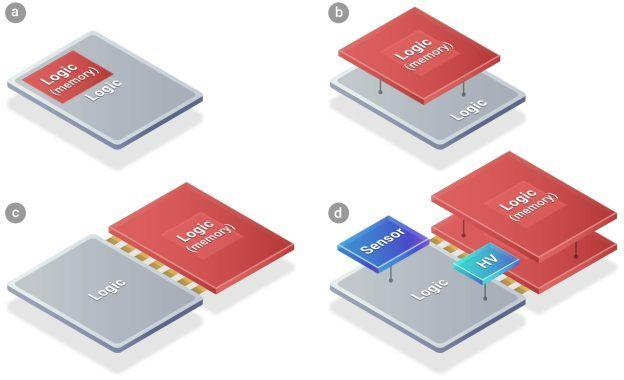

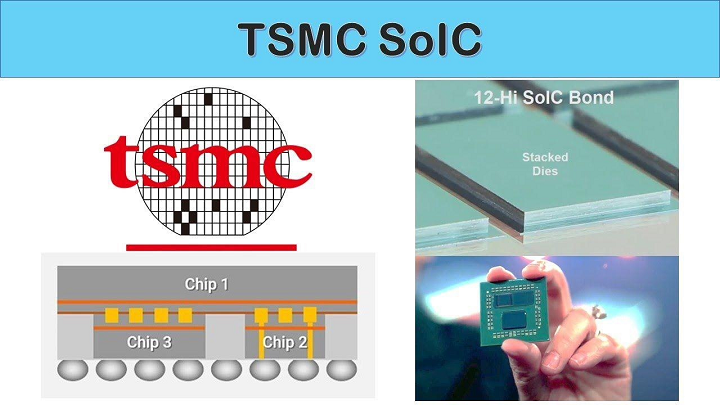

編者注:臺積電 SoIC 是業(yè)內第一個高密度 3D chiplet 堆疊技術。SoIC 設計是在創(chuàng)造鍵合界面,讓芯片可以直接堆疊在芯片上。

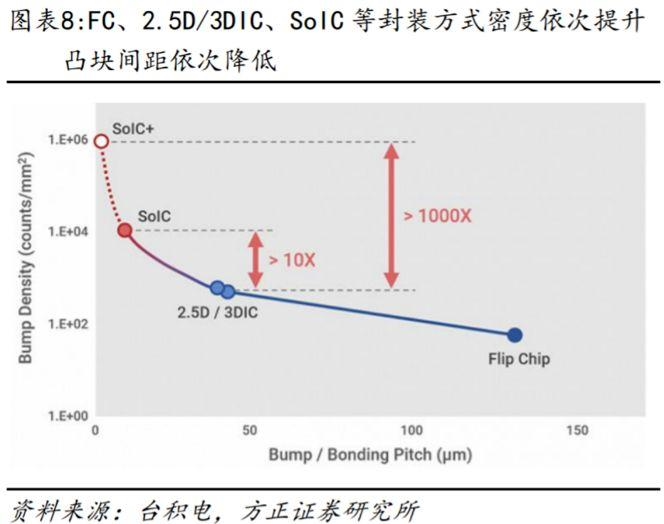

封裝技術主要指標為凸點間距(Bump Pitch),凸點間距越小,封裝集成度越高,難度越大,臺積電的 3D SoIC 的凸點間距最小可達 6um,居于所有封裝技術首位。

SoIC 是一種“3D 封裝最前沿”技術,是臺積電異構小芯片封裝的關鍵,具有高密度垂直堆疊性能。與 CoWoS 及 InFo 技術相比,SoIC 可提供更高的封裝密度、更小的鍵合間隔,還可以與 CoWoS / InFo 共用,基于 SoIC 的 CoWoS / InFo 封裝將帶來更小的芯片尺寸,實現(xiàn)多個小芯片集成。

業(yè)內人士表示,SoIC 在 2023 年年底,月產能為 2000 顆,原本計劃 2024 年擴大到 3000-4000 顆,而最新計劃被上調至 5000-6000 顆,而且 2025 年目標月產能再翻番。

CoWoS 是一項經過 15 年發(fā)展的成熟技術,預計到今年年底月產能將達到 30000 至 34000 件。