4 月 12 日消息,根據(jù)供應(yīng)鏈消息,在 AMD 之后,蘋(píng)果、英偉達(dá)、博通三家公司也開(kāi)始和臺(tái)積電合作,推進(jìn) SoIC 封裝方案。

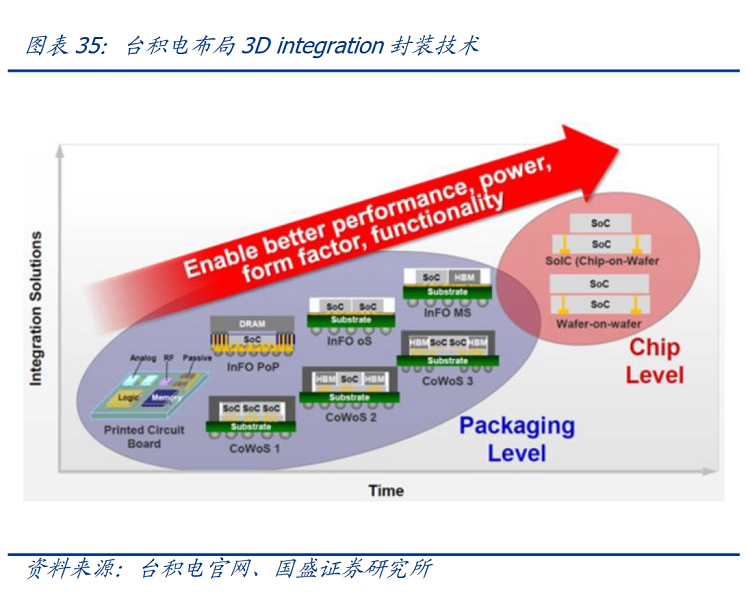

臺(tái)積電正在積極提高 CoWoS 封裝產(chǎn)能的同時(shí),也在積極推動(dòng)下一代 SoIC 封裝方案落地投產(chǎn)。

AMD 是臺(tái)積電 SoIC 的首發(fā)客戶(hù),旗下的 MI300 加速卡就使用了 SoIC+CoWoS 封裝解決方案,可將不同尺寸、功能、節(jié)點(diǎn)的晶粒進(jìn)行異質(zhì)整合,目前在位于竹南的第五座封測(cè)廠(chǎng) AP6 生產(chǎn)。

最新消息稱(chēng)臺(tái)積電最大客戶(hù)蘋(píng)果對(duì) SoIC 封裝也非常感興趣,將采取 SoIC 搭配 Hybrid molding(熱塑碳纖板復(fù)合成型技術(shù)),目前正小量試產(chǎn),預(yù)計(jì) 2025~2026 年量產(chǎn),計(jì)劃應(yīng)用在 Mac 上。

而英偉達(dá)和博通公司目前也和臺(tái)積電展開(kāi)合作,嘗試部署 SoIC 封裝方案。

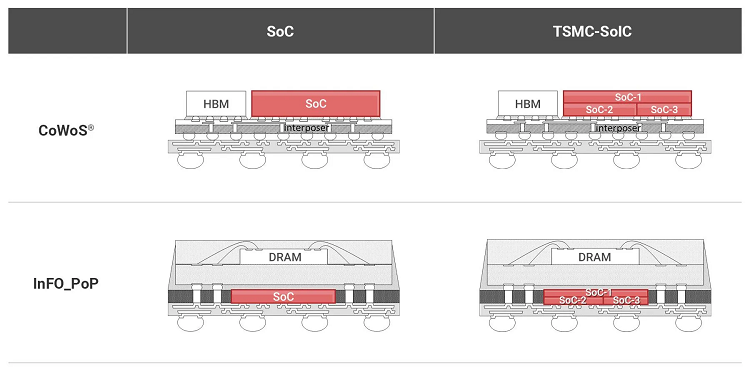

CoWoS CoWoS(Chip On Wafer On Substrate)是一種 2.5D 的整合生產(chǎn)技術(shù),由 CoW 和 oS 組合而來(lái):先將芯片通過(guò) Chip on Wafer(CoW)的封裝制程連接至硅晶圓,再把 CoW 芯片與基板(Substrate)連接,整合成 CoWoS。

SoIC SoIC 于 2018 年 4 月公開(kāi),是臺(tái)積電基于 CoWoS 與多晶圓堆疊 (WoW) 封裝技術(shù),開(kāi)發(fā)的新一代創(chuàng)新封裝技術(shù),這標(biāo)志著臺(tái)積電已具備直接為客戶(hù)生產(chǎn) 3D IC 的能力。

相較 2.5D 封裝方案,SoIC 的凸塊密度更高,傳輸速度更快,功耗更低。