1 前言

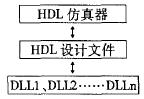

協(xié)同仿真就是利用仿真工具提供的外部接口,用其它程序設(shè)計(jì)語(yǔ)言(非HDL語(yǔ)言,如c語(yǔ)言等)編程,用輔助仿真工具進(jìn)行仿真。MODELsim 提供了與c語(yǔ)言的協(xié)同仿真接口。以Windows平臺(tái)為例,用戶可通過(guò)MODELsim 提供的c語(yǔ)言接口函數(shù)編程,生成動(dòng)態(tài)鏈接庫(kù),由MODELsim 調(diào)用這些動(dòng)態(tài)鏈接庫(kù)進(jìn)行輔助仿真,如圖1所示。

圖1 協(xié)同仿真示意圖

2 MODELsim及FLI接口介紹

MODELsim是MODEL Technology(Mentor Graphics的子公司)的HDL硬件描述語(yǔ)言仿真軟件,可以實(shí)現(xiàn)VHDL、Verilog以及VHDL-Verilog混合設(shè)計(jì)的仿真。除此之外,MODELsim 還能夠與c語(yǔ)言一起對(duì)HDL設(shè)計(jì)文件實(shí)現(xiàn)協(xié)同仿真。同時(shí),相對(duì)于大多數(shù)的HDL仿真軟件來(lái)說(shuō),MODELsim 在仿真速度上也有明顯優(yōu)勢(shì)。這些特點(diǎn)使MODELsim 越來(lái)越受到EDA設(shè)計(jì)者、尤其是FPGA設(shè)計(jì)者的青睞。

MODELsim的FLI(Foreign Language Interface)接口,提供了c語(yǔ)言動(dòng)態(tài)鏈接程序與仿真器的接口,可以通過(guò)c語(yǔ)言編程對(duì)設(shè)計(jì)文件進(jìn)行輔助仿真。

3 協(xié)同仿真系統(tǒng)的結(jié)構(gòu)及意義

MODELsim與c語(yǔ)言協(xié)同仿真,一是用于產(chǎn)生測(cè)試向量,避免手工編寫(xiě)測(cè)試向量的繁瑣;二是可以根據(jù)程序計(jì)算結(jié)果自動(dòng)檢查仿真結(jié)果正確與否;三是模擬其它模塊(如RAM)的功能,在系統(tǒng)級(jí)對(duì)設(shè)計(jì)文件仿真。實(shí)踐中一般是把一和二結(jié)合在一起,用程序產(chǎn)生仿真向量,一方面輸出給設(shè)計(jì)文件作為輸入,另一方面由程序本身對(duì)該向量計(jì)算,把得到的結(jié)果與仿真器的輸出結(jié)果比較,檢查邏輯是否正確,如圖2所示。至于模擬功能,現(xiàn)在已經(jīng)有一些通用芯片的模擬程序,如denali可以模擬RAM的功能。另外,用戶也可以利用MODELsim 提供的編程接口自己模擬一些芯片的行為,然后與設(shè)計(jì)文件連接到一起仿真。

圖2 語(yǔ)言測(cè)試程序?qū)HDL設(shè)計(jì)文件的協(xié)同仿真結(jié)構(gòu)圖

4 C語(yǔ)言對(duì)VHDL設(shè)計(jì)文件的協(xié)同仿真

4.1 構(gòu)成框圖

仿真文件的構(gòu)成如圖3所示,包括HDL文件和動(dòng)態(tài)鏈接庫(kù)(即c程序)。圖中c程序?qū)?yīng)的VHDL文件要負(fù)責(zé)聲明對(duì)應(yīng)的動(dòng)態(tài)鏈接庫(kù)文件名及初始化函數(shù),另外還可以給出一些調(diào)用參數(shù)。動(dòng)態(tài)鏈接中用到的輸入輸出信號(hào)也要在對(duì)應(yīng)的VHDL文件中聲明。

例如,假定有一個(gè)DLL文件名為sim.dll,對(duì)應(yīng)的初始化函數(shù)為sim_init,有輸入信號(hào)in1、in2,輸出信號(hào)out1、 out2,可以這樣編寫(xiě)對(duì)應(yīng)的VHDL文件

(sim.vhd):

library ieee;

use ieee.std_logic_1164.all;

entity sim is

port(

in1 :in std_logic;

in2 :in std logic;

out1 :out std_logic;

out2 :out std_logic;

);

end entity sire;

architecture dll of sim is

attribute foreign :string;

attribute foreign of dll :architecture is "sim_init

sim.dll”

begin

end;

仿真時(shí),仿真器對(duì)頂層的HDL文件進(jìn)行仿真,并根據(jù)各VHDL文件的動(dòng)態(tài)鏈接庫(kù)聲明來(lái)調(diào)用、執(zhí)行相應(yīng)的動(dòng)態(tài)鏈接庫(kù)。

4.2 動(dòng)態(tài)鏈接庫(kù)的程序結(jié)構(gòu)

利用MODELsim仿真時(shí),可根據(jù)VHDL文件的聲明,調(diào)用DLL文件(如sim.dll)。在VHDL文件中已經(jīng)給出了調(diào)用文件(sim.dll)和初始化函數(shù)名(如sim_init),MODELsim 根據(jù)這些信息,調(diào)用sim.dll中的sim_init函數(shù),完成初始化工作。初始化包括:

①初始化全局變量;

②設(shè)置VHDL輸入輸出信號(hào)與c程序變量的對(duì)應(yīng)關(guān)系;

③設(shè)置輸出信號(hào)的一些初始狀態(tài)(mti_ScheduleDriver);

④設(shè)置在仿真器重新仿真(restart)和仿真器退出仿真(quit)等情況下執(zhí)行的一些函數(shù)(mti_AddRestartCB和 mti_AddQuitCB等),如釋放動(dòng)態(tài)申請(qǐng)內(nèi)存等;

⑤設(shè)置敏感表,給出在某些信號(hào)發(fā)生變化(如時(shí)鐘上升沿等)時(shí)執(zhí)行的函數(shù)。

⑥其它。

C程序的設(shè)計(jì)步驟如下:

(1)包含頭文件,包括c程序常用的一些頭文件和MODELsim 給出的外部語(yǔ)言接口頭文件mti.h。MODELsim 給出的外部接口函數(shù)說(shuō)明、類(lèi)型定義等都在mti.h中。

(2)定義自己的結(jié)構(gòu)體,這一點(diǎn)主要是為了編程方便,例如輸入輸出信號(hào)對(duì)應(yīng)的變量在各函數(shù)中基本上都會(huì)用到,可以把這些變量定義成一個(gè)結(jié)構(gòu),便于參數(shù)傳遞。

(3)編寫(xiě)初始化函數(shù)

初始化函數(shù)的定義為:

init_func(mtiReginoIdT region,char *param,

mtiInterfaceListT *generics,mtiInterfaceListT *ports)

各參數(shù)的意義可以參閱MODELsim用戶手冊(cè)。

下面結(jié)合上面給出的初始化函數(shù)要完成的任務(wù)進(jìn)行詳細(xì)說(shuō)明。

a.初始化全局變量(略)

b.設(shè)置VHDL輸入輸出信號(hào)與c程序變量的對(duì)應(yīng)關(guān)系。這是通過(guò)調(diào)用mti_FindPort函數(shù)實(shí)現(xiàn)的。mti_FindPort函數(shù)定義為:

mfiSignalIdT mti_FindPort(mtiInterfaceListT *list,char *name);

例如,定義輸入輸出信號(hào)對(duì)應(yīng)的結(jié)構(gòu)ip:

PortStruct ip;

就可以用:

ip_in1=mti_FindPort(ports,"in1");

來(lái)實(shí)現(xiàn)輸入信號(hào)in1與變量in1的對(duì)應(yīng)關(guān)系。

對(duì)輸出信號(hào)來(lái)說(shuō),它的目的是產(chǎn)生驅(qū)動(dòng)。因此,這些變量(out1和out2)除了要找到對(duì)應(yīng)的輸出信號(hào)外,還要驅(qū)動(dòng)這些信號(hào)。對(duì)信號(hào)的驅(qū)動(dòng)可以通過(guò)調(diào)用mti_CreateDriver函數(shù)來(lái)實(shí)現(xiàn)。該函數(shù)的定義為:

mtiDriverIdT mti_CreateDriver(mtiSignalIdT sig);

由于這些變量一般只用于對(duì)外驅(qū)動(dòng),因此可以簡(jiǎn)單寫(xiě)成下面的形式:

ip.out1 = mti+ CreateDriver(mti_FindPort(ports,"out1"));

C.調(diào)用mti_ScheduleDriver函數(shù),設(shè)置輸出信號(hào)的初始狀態(tài)。mti_ScheduleDriver函數(shù)的定義為:

void mti_ScheduIeDriver(mtiDriverIdT driver,long value,mtiDelayT delay,mtiDriverModeT mode);

其中,driver是輸出信號(hào)對(duì)應(yīng)的變量名,如ip.out1和ip.out2;value是要設(shè)置(驅(qū)動(dòng))的值,如高電平('1',對(duì)應(yīng) value為3)、低電平('0',對(duì)應(yīng)value為2)、高阻('z',對(duì)應(yīng)value為4)、未賦值('U',對(duì)應(yīng)value為0)等等;delay 是從當(dāng)前時(shí)間開(kāi)始到把信號(hào)驅(qū)動(dòng)成給定值(value)的等待時(shí)間,單位與仿真器當(dāng)前使用的最小時(shí)間單位相同;mode為信號(hào)模式,有兩個(gè)值可供選擇:MTI_INERTIAL或者是MTI_TRANSPORT,分別對(duì)應(yīng)于標(biāo)準(zhǔn)VHDL語(yǔ)言的INERTIAL和TRANSPORT。例如,設(shè)置信號(hào) out1的初始狀態(tài)為低電平:

mti_ScheduleDriver(ip.out1,2,0,MTI_INERTIAL);

d.設(shè)置在仿真器重新仿真(運(yùn)行命令restart)或退出仿真(運(yùn)行命令quit-sim)等情況下調(diào)用的函數(shù)。這一部分主要是為了釋放內(nèi)存或者保存當(dāng)前狀態(tài)等。以restart為例,假設(shè)在程序中用malloc申請(qǐng)了存儲(chǔ)空間buf,在仿真器"restart"時(shí)需要釋放,就可以用以下的函數(shù)調(diào)用來(lái)注冊(cè):

mti_AddRestartCB(free,buf);

注冊(cè)后,當(dāng)仿真器運(yùn)行命令restart時(shí)就會(huì)調(diào)用free(buf)。

其它一些函數(shù)可以參照MODELsim的用戶手冊(cè)這里不再詳述。

e.設(shè)置敏感表,給出在某些信號(hào)發(fā)生某些變化時(shí)(如時(shí)鐘上升沿等)執(zhí)行的函數(shù)。例如,在輸入信號(hào)in1發(fā)生變化時(shí),要執(zhí)行函數(shù) in1_change(in1_change為用戶定義好的函數(shù)),可以這樣定義:

processed proc;

proc=mti_CreateProcess("P_in 1 change",in1_

change,&ip);

mti_Sensitize(proc,ip.in1,MTI_EVENT);

也就是說(shuō),先創(chuàng)建進(jìn)程,然后設(shè)置敏感表。當(dāng)滿足敏感表的條件時(shí),仿真器就會(huì)執(zhí)行該進(jìn)程。mti_CreateProcess函數(shù)的定義為:

mtiProcessldT mti_CreateProcess(char *name,mtiVoidFuncPtrT func,void * Param);其中,name是將要在仿真器窗口中顯示的名稱(chēng);func是要執(zhí)行的函數(shù);后面的param是要傳給func的參數(shù)。 mti_Sensitize的定義為:

void mti_Sensitize(mtiProcessIdT proc,mtiSignalIdT sig,mtiProcessTriggerT when);

其中,proc為調(diào)用mti_CreateProcess的返回值;sig為信號(hào)名,即VHDL文件的輸入輸出信號(hào)對(duì)應(yīng)于C程序的變量;when可以取MTI_EVENT或者M(jìn)TI_ACTIVE兩種值。

4.3 C程序的編譯

對(duì)Windows平臺(tái),采用的編譯器是MicrosoftVisual C++,并用如下的命令進(jìn)行編譯:

cl -c -I app.c

link -dll -export: app.obj

MODELtech.lib

上面的是MODELsim 的安裝目錄,是c程序的初始化函數(shù)名,如我們給出的sim.c的sim_init。編譯之后就可以生成.dll文件。

仿真向量是用c語(yǔ)言還是用HDL直接產(chǎn)生,要視設(shè)計(jì)者的應(yīng)用而定,選取最簡(jiǎn)單的方式。在大多數(shù)情況下,用c語(yǔ)言和HDL聯(lián)合生成測(cè)試向量會(huì)更方便些。

5 結(jié)論

利用Moelsim的FLI功能,用c語(yǔ)言對(duì)所設(shè)計(jì)的模型進(jìn)行功能驗(yàn)證,可以加大驗(yàn)證代碼的覆蓋率,減少驗(yàn)證代碼的復(fù)雜度,加快驗(yàn)證的速度,縮短設(shè)計(jì)周期,可以更好的驗(yàn)證系統(tǒng)的通用性。另外,MODELsim 的FLI功能使硬件描述語(yǔ)言(Verilog,VHDL)與c語(yǔ)言緊密結(jié)合在一起,為設(shè)計(jì)人員提供了更廣闊的驗(yàn)證平臺(tái),更方便的驗(yàn)證方法。