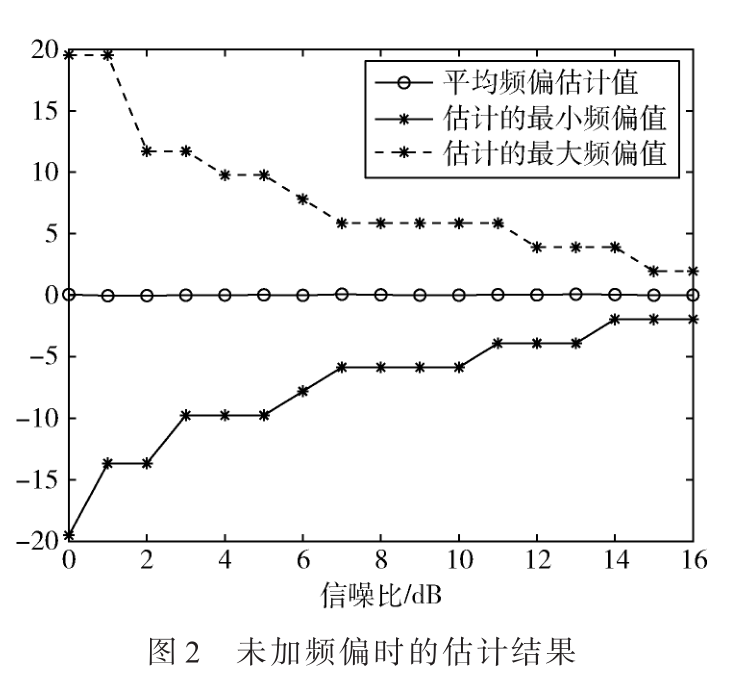

一種數(shù)字集群系統(tǒng)中GMSK信號(hào)的相偏跟蹤算法[通信與網(wǎng)絡(luò)][通信網(wǎng)絡(luò)]

發(fā)表于:9/4/2024 3:09:37 PM

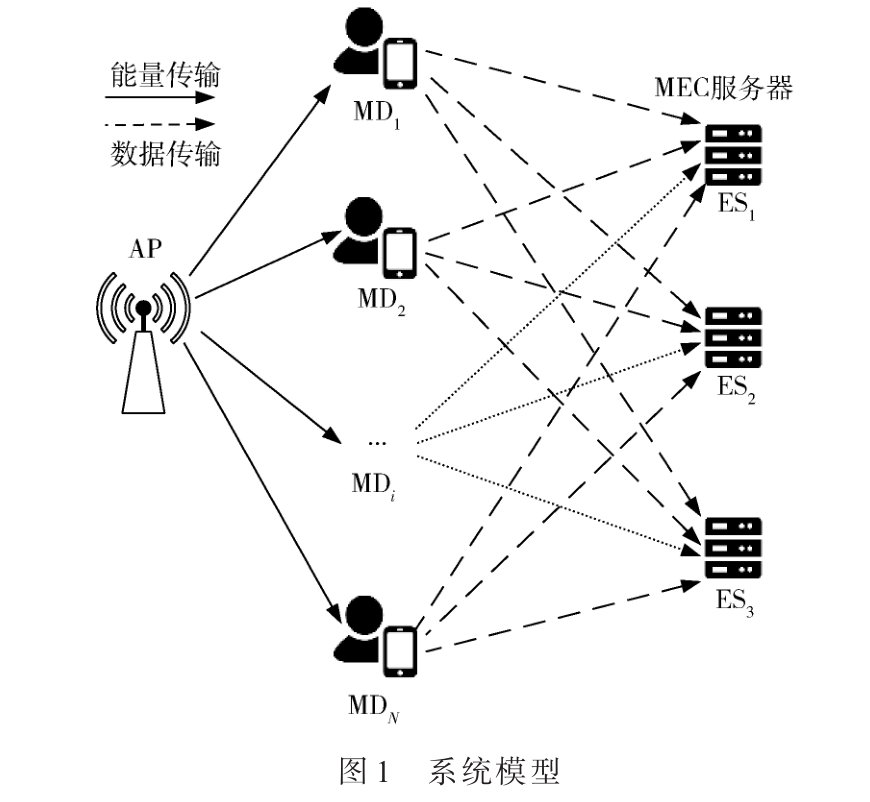

無(wú)線供電MEC中基于S-PSO的任務(wù)卸載策略研究[通信與網(wǎng)絡(luò)][物聯(lián)網(wǎng)]

發(fā)表于:9/4/2024 2:57:57 PM

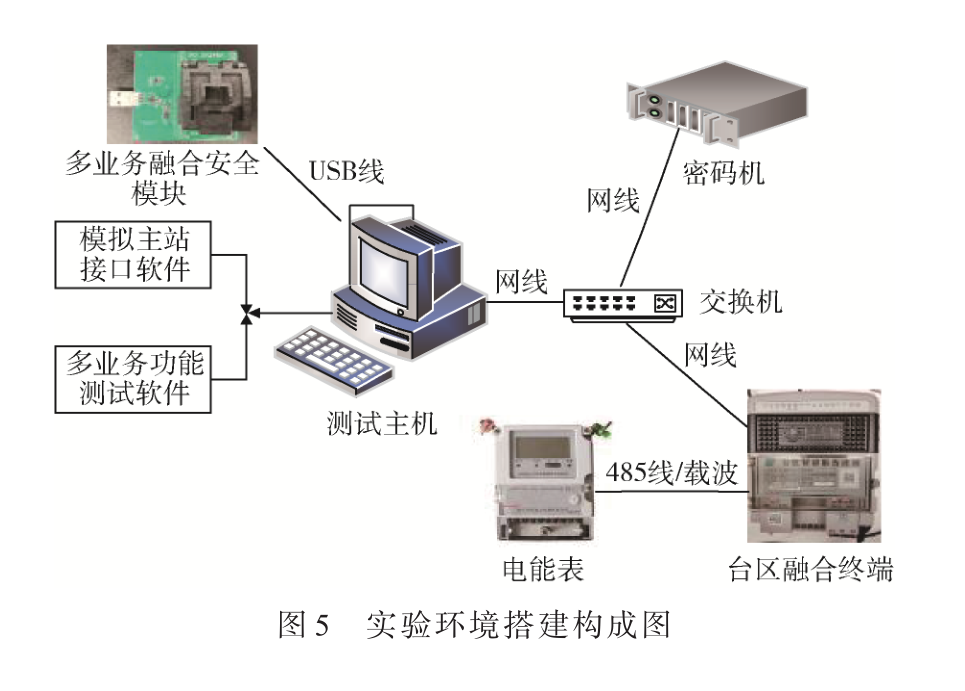

面向臺(tái)區(qū)智能終端的高強(qiáng)度商用密碼安全管理方法研究[測(cè)試測(cè)量][智能電網(wǎng)]

發(fā)表于:9/4/2024 2:36:15 PM

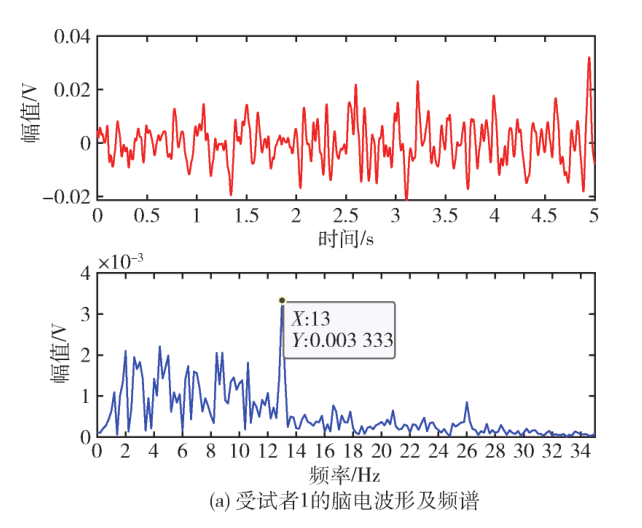

雙模態(tài)穩(wěn)態(tài)誘發(fā)腦電刺激系統(tǒng)設(shè)計(jì)[測(cè)試測(cè)量][醫(yī)療電子]

發(fā)表于:9/4/2024 2:25:30 PM

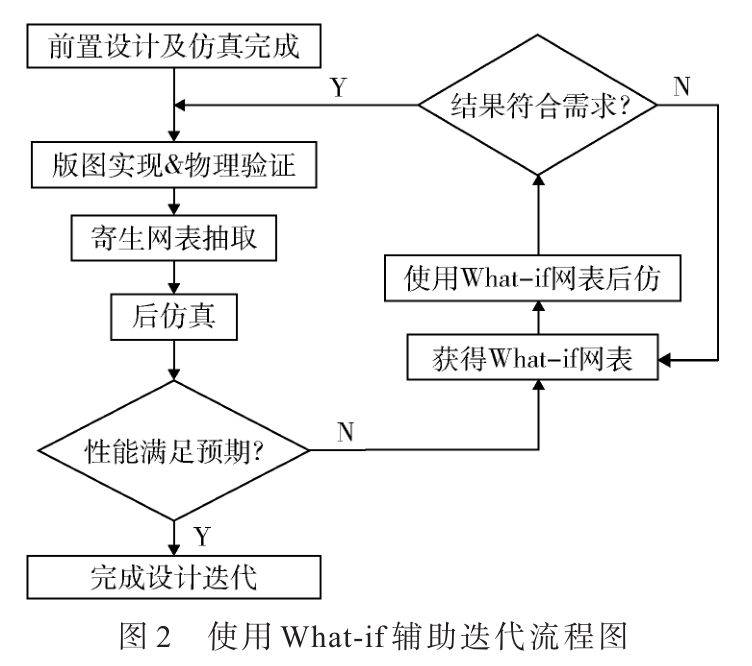

Optimality在多個(gè)場(chǎng)景的時(shí)域仿真中高效性的深度研究[模擬設(shè)計(jì)][工業(yè)自動(dòng)化]

發(fā)表于:9/4/2024 2:14:34 PM

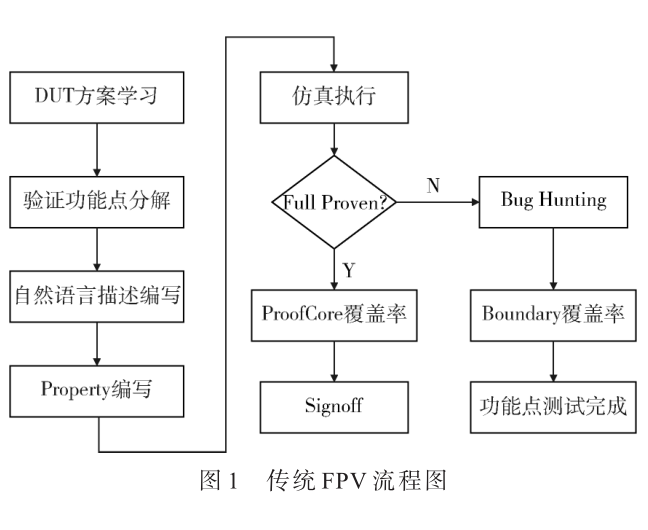

基于AI加速的可復(fù)用FPV平臺(tái)庫(kù)[人工智能][汽車電子]

發(fā)表于:9/4/2024 2:03:07 PM

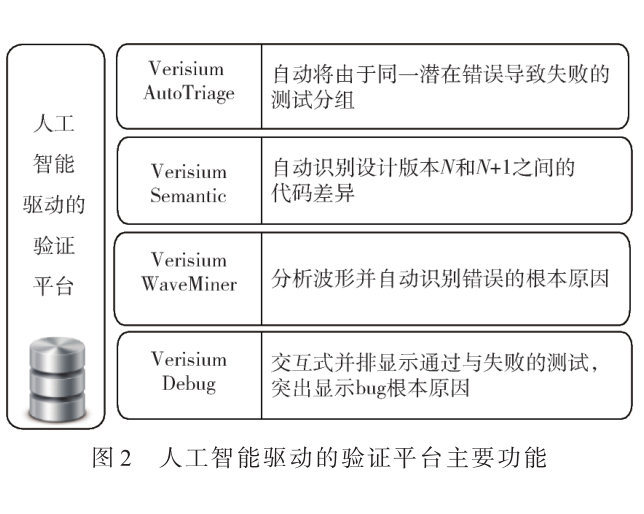

使用Cadence AI技術(shù)加速驗(yàn)證效率提升[EDA與制造][消費(fèi)電子]

發(fā)表于:9/4/2024 1:52:25 PM

基于Cerebrus的Genus+Innovus流程的功耗面積優(yōu)化[模擬設(shè)計(jì)][消費(fèi)電子]

發(fā)表于:9/4/2024 1:31:51 PM

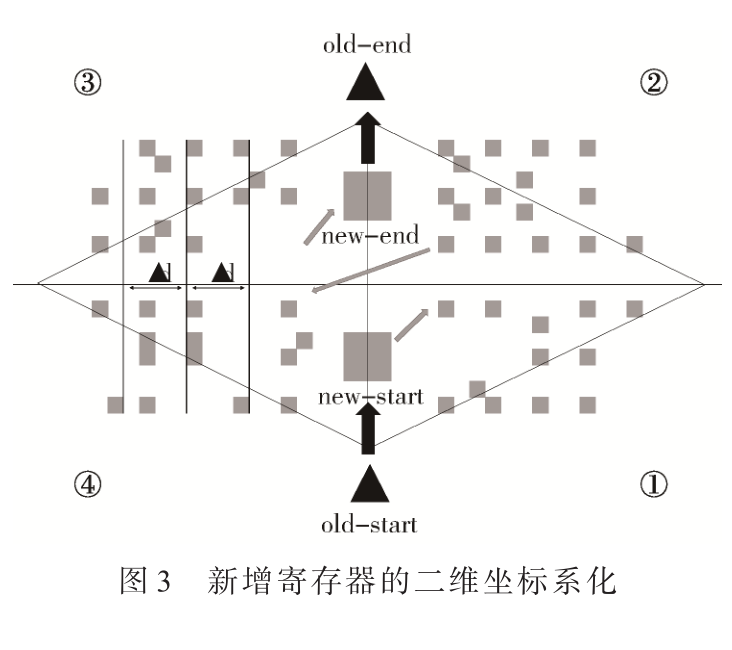

Conformal ECO寄存器新增的掃描鏈自動(dòng)化接入方案[模擬設(shè)計(jì)][工業(yè)自動(dòng)化]

發(fā)表于:9/4/2024 1:21:13 PM